没有合适的资源?快使用搜索试试~ 我知道了~

32位MIPS CPU 设计 实验报告.pdf

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 97 浏览量

2022-07-01

21:21:04

上传

评论

收藏 1.67MB PDF 举报

温馨提示

试读

33页

32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf32位MIPS CPU 设计 实验报告.pdf

资源推荐

资源详情

资源评论

数字逻辑与处理器基础实验

32 位 MIPS CPU 设计

综述:

我们的最后验收结果时钟频率是 84.9MHz。

本实验报告主要分为实验设计说明与实验收获总结两个部分。

附件中有 CPU 工程文档与模块代码。

第一部分 实验设计

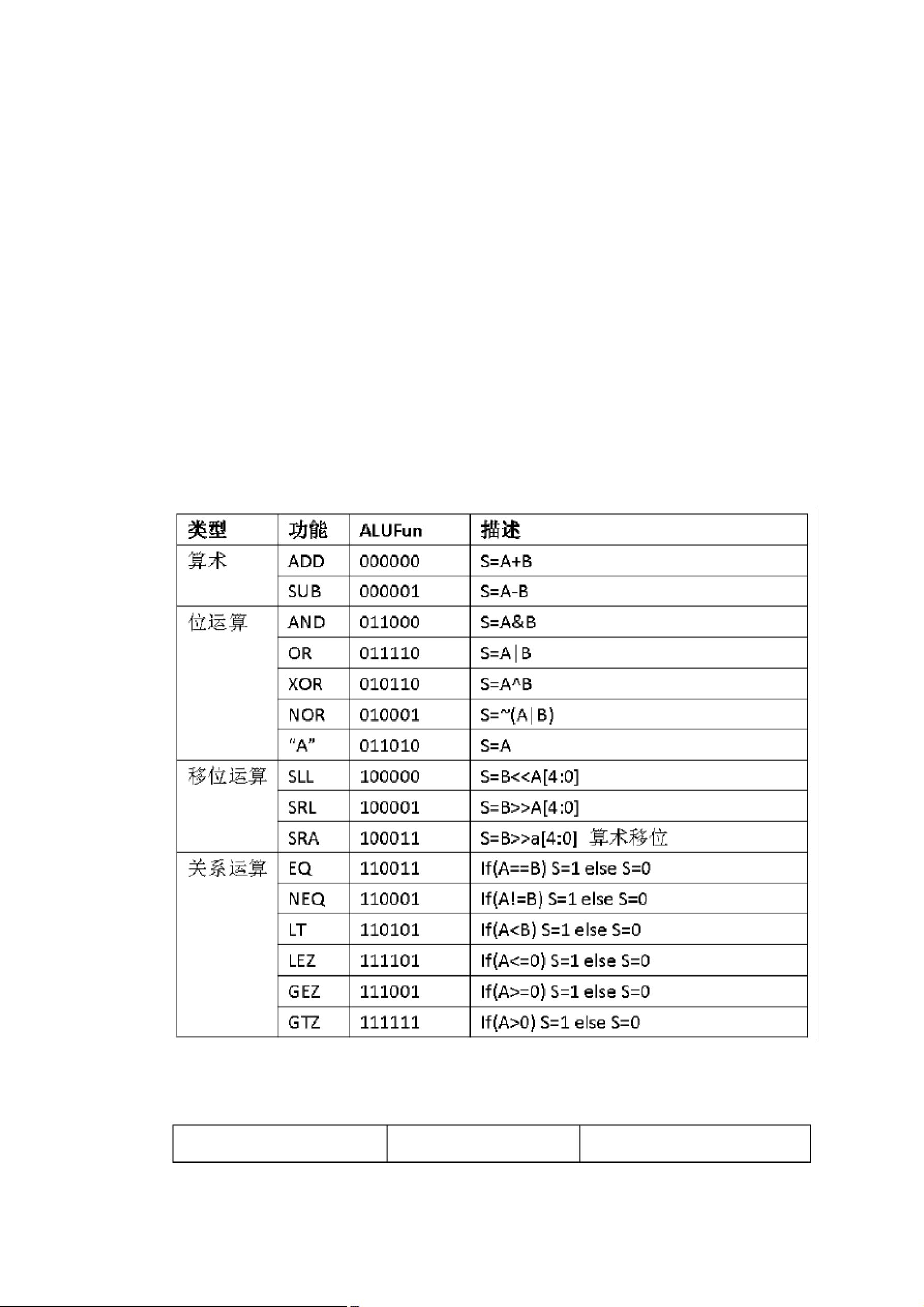

一、 ALU 设计

1、设计思路

实现基本的算术、逻辑、关系、位与移位运算,尽量优化以达到最小的面积延时积。

结构图如下:

主要设计思想:

A. 加法运算实现可以采用逐次进位、超前进位等结构,减法可以通过加法实现(参见

见面理论课讲义或者前面实验);同时输出 Z(结果为零)、V(结果溢出)、N(结果为

负)等标志位,注意有符号数和无符号数标志产生的不同。

B. 比较运算根据减法运算的结果(Z/V/N)产生,自行分析比较操作与算术运算之间的

关系。

C. 移位运算可以考虑将移位操作拆分为 16 位移位、8 位移位、4 位移位、2 位移位、

1 位移位等几个子运算的组合,然后级联形成最后的运算结果。

D. 逻辑运算可以根据要求直接产生。

功能表

接口说明

名称 类型 描述

A[31:0]

B[31:0]

ALUFun[5:0]

Sign

S[31:0]

输入

输入

输入

输入

输出

操作数 1

操作数 2

功能码

符号:有符号 1,无符号 0

结果输出

2、主要模块

a) 32bit 加法器

采用 8 个 4bit 超前进位加法器极连的方式,构成 32bit 加法器。对于逸出位 v 的

处理如下:由有符号数的性质可知,对最高位 32 和次高位 31 位取抑或,输出信号

则为是否逸出。对 32 位运算结果取反后,再对相邻两位反复取与,最终得到结果

是否为零的输出 z.如果是有符号数,则符号位=n。

由于这一方法部分程度上减弱了高位计算对低位计算的依赖程度,因此可以实现延

时的降低。同时,由于其超前进位网络的大量逻辑运算,较大程度上提升了电路的

面积,造成最终的面积延时积特性恶化。

关键代码见附录 1

b) 32bit 减法器

对加法器按位取反,再加一。

关键代码见附录 1

c) 32bit 右移

32bit 左移

32bit 算术右移

将移位操作拆分为 16 位移位、8 位移位、4 位移位、2 位移位、1 位移位等几个

子运算的组合,然后级联得到最后的运算结果。

关键代码见附录 1

d) 32bit 逻辑比较单元

采用行为级语句直实现逻辑比较功能。

关键代码见附录 1

e) ALU 顶层控制模块

用多路选择器实现对输出结果的控制,采用行为级语句实现设计。

附加说明:对于无符号运算的结果,由于z,v,n 已经将符号的作用考虑进去,因

此,对于需要实现的六个指令,仅有 A<B 需要特殊处理,而其他指令对于无符号

数和有符号数的结果一致。因此,针对 A<B 指令,添加针对无符号数的专用比较

电路,并使用与超前进位加法器类似的方式进行并行加速操作。

关键代码见附录 1

二、单周期MIPS处理器设计

流程框图:

剩余32页未读,继续阅读

资源评论

xxpr_ybgg

- 粉丝: 6430

- 资源: 3万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功