没有合适的资源?快使用搜索试试~ 我知道了~

AT91SAM7XC256_AU_Preliminary

需积分: 9 3 下载量 118 浏览量

2009-06-27

02:36:45

上传

评论

收藏 9.95MB PDF 举报

温馨提示

试读

687页

AT91SAM7XC256 Datasheet Preliminary

资源推荐

资源详情

资源评论

Features

• Incorporates the ARM7TDMI

®

ARM

®

Thumb

®

Processor

– High-performance 32-bit RISC Architecture

– High-density 16-bit Instruction Set

• Leader in MIPS/Watt

– EmbeddedICE

™

In-circuit Emulation, Debug Communication Channel Support

• Internal High-speed Flash

– 512 Kbytes (AT91SAM7X512) Organized in Two Banks of 1024 Pages of

256 Bytes (Dual Plane)

– 256 Kbytes (AT91SAM7X256) Organized in 1024 Pages of 256 Bytes (Single Plane)

– 128 Kbytes (AT91SAM7X128) Organized in 512 Pages of 256 Bytes (Single Plane)

• Single Cycle Access at Up to 30 MHz in Worst Case Conditions

• Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed

• Page Programming Time: 6 ms, Including Page Auto-erase,

Full Erase Time: 15 ms

• 10,000 Write Cycles, 10-year Data Retention Capability,

Sector Lock Capabilities, Flash Security Bit

• Fast Flash Programming Interface for High Volume Production

• Internal High-speed SRAM, Single-cycle Access at Maximum Speed

– 128 Kbytes (AT91SAM7X512)

– 64 Kbytes (AT91SAM7X256)

– 32 Kbytes (AT91SAM7X128)

• Memory Controller (MC)

– Embedded Flash Controller, Abort Status and Misalignment Detection

• Reset Controller (RSTC)

– Based on Power-on Reset Cells and Low-power Factory-calibrated Brownout

Detector

– Provides External Reset Signal Shaping and Reset Source Status

• Clock Generator (CKGR)

– Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL

• Power Management Controller (PMC)

– Power Optimization Capabilities, Including Slow Clock Mode (Down to 500 Hz) and

Idle Mode

– Four Programmable External Clock Signals

• Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Two External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt

Protected

• Debug Unit (DBGU)

– 2-wire UART and Support for Debug Communication Channel interrupt,

Programmable ICE Access Prevention

– Mode for General Purpose 2-wire UART Serial Communication

• Periodic Interval Timer (PIT)

– 20-bit Programmable Counter plus 12-bit Interval Counter

• Windowed Watchdog (WDT)

– 12-bit key-protected Programmable Counter

– Provides Reset or Interrupt Signals to the System

– Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

AT91 ARM

Thumb-based

Microcontrollers

AT91SAM7X512

AT91SAM7X256

AT91SAM7X128

Preliminary

6120H–ATARM–17-Feb-08

2

6120H–ATARM–17-Feb-08

AT91SAM7X512/256/128 Preliminary

• Real-time Timer (RTT)

– 32-bit Free-running Counter with Alarm

– Runs Off the Internal RC Oscillator

• Two Parallel Input/Output Controllers (PIO)

– Sixty-two Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line

– Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output

• Thirteen Peripheral DMA Controller (PDC) Channels

• One USB 2.0 Full Speed (12 Mbits per second) Device Port

– On-chip Transceiver, 1352-byte Configurable Integrated FIFOs

• One Ethernet MAC 10/100 base-T

– Media Independent Interface (MII) or Reduced Media Independent Interface (RMII)

– Integrated 28-byte FIFOs and Dedicated DMA Channels for Transmit and Receive

• One Part 2.0A and Part 2.0B Compliant CAN Controller

– Eight Fully-programmable Message Object Mailboxes, 16-bit Time Stamp Counter

• One Synchronous Serial Controller (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

– I²S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

• Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)

– Individual Baud Rate Generator, IrDA

®

Infrared Modulation/Demodulation

– Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

– Full Modem Line Support on USART1

• Two Master/Slave Serial Peripheral Interfaces (SPI)

– 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

• One Three-channel 16-bit Timer/Counter (TC)

– Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel

– Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

• One Four-channel 16-bit Power Width Modulation Controller (PWMC)

• One Two-wire Interface (TWI)

– Master Mode Support Only, All Two-wire Atmel EEPROMs and I

2

C Compatible Devices Supported

• One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os

• SAM-BA

®

Boot Assistance

– Default Boot program

– Interface with SAM-BA Graphic User Interface

• IEEE

®

1149.1 JTAG Boundary Scan on All Digital Pins

• 5V-tolerant I/Os, Including Four High-current Drive I/O lines, Up to 16 mA Each

• Power Supplies

– Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components

– 3.3V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply

– 1.8V VDDCORE Core Power Supply with Brownout Detector

• Fully Static Operation: Up to 55 MHz at 1.65V and 85° C Worst Case Conditions

• Available in 100-lead LQFP Green and 100-ball TFBGA Green Packages

3

6120H–ATARM–17-Feb-08

AT91SAM7X512/256/128 Preliminary

1. Description

Atmel's AT91SAM7X512/256/128 is a member of a series of highly integrated Flash microcon-

trollers based on the 32-bit ARM RISC processor. It features 512/256/128 Kbyte high-speed

Flash and 128/64/32 Kbyte SRAM, a large set of peripherals, including an 802.3 Ethernet MAC

and a CAN controller. A complete set of system functions minimizes the number of external

components.

The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via

a parallel interface on a production programmer prior to mounting. Built-in lock bits and a secu-

rity bit protect the firmware from accidental overwrite and preserve its confidentiality.

The AT91SAM7X512/256/128 system controller includes a reset controller capable of managing

the power-on sequence of the microcontroller and the complete system. Correct device opera-

tion can be monitored by a built-in brownout detector and a watchdog running off an integrated

RC oscillator.

By combining the ARM7TDMI processor with on-chip Flash and SRAM, and a wide range of

peripheral functions, including USART, SPI, CAN Controller, Ethernet MAC, Timer Counter, RTT

and Analog-to-Digital Converters on a monolithic chip, the AT91SAM7X512/256/128 is a power-

ful device that provides a flexible, cost-effective solution to many embedded control applications

requiring communication over, for example, Ethernet, CAN wired and Zigbee

™

wireless

networks.

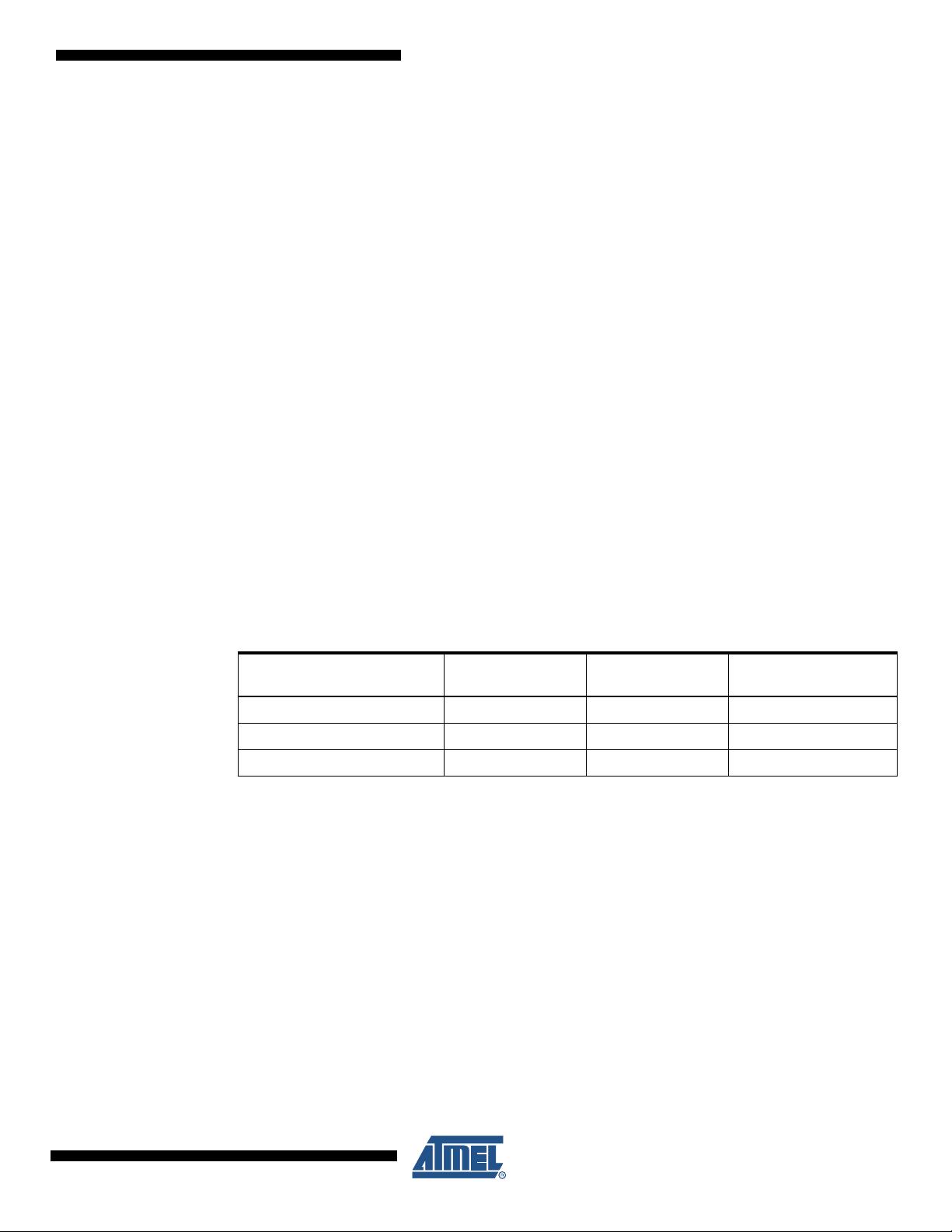

1.1 Configuration Summary of the AT91SAM7X512/256/128

The AT91SAM7X512, AT91SAM7X256 and AT91SAM7X128 differ only in memory sizes. Table

1-1 summarizes the configurations of the three devices.

Table 1-1. Configuration Summary

Device Flash

Flash

Organization SRAM

AT91SAM7X512 512 Kbytes dual plane 128 Kbytes

AT91SAM7X256 256 Kbytes single plane 64 Kbytes

AT91SAM7X128 128 Kbytes single plane 32 Kbytes

4

6120H–ATARM–17-Feb-08

AT91SAM7X512/256/128 Preliminary

2. AT91SAM7X512/256/128 Block Diagram

Figure 2-1. AT91SAM7X512/256/128 Block Diagram

TDI

TDO

TMS

TCK

NRST

FIQ

IRQ0-IRQ1

PCK0-PCK3

PMC

Peripheral Bridge

Peripheral DMA

Controller

AIC

PLL

RCOSC

SRAM

128/64/32 Kbytes

ARM7TDMI

Processor

ICE

JTAG

SCAN

JTAGSEL

PIOA

USART0

SSC

Timer Counter

RXD0

TXD0

SCK0

RTS0

CTS0

SPI0_NPCS0

SPI0_NPCS1

SPI0_NPCS2

SPI0_NPCS3

SPI0_MISO

SPI0_MOSI

SPI0_SPCK

Flash

512/256/128

Kbytes

Reset

Controller

DRXD

DTXD

TF

TK

TD

RD

RK

RF

TCLK0

TCLK1

TCLK2

TIOA0

TIOB0

TIOA1

TIOB1

TIOA2

TIOB2

Memory Controller

Abort

Status

Address

Decoder

Misalignment

Detection

PIO

PIO

APB

POR

Embedded

Flash

Controllers

AD0

AD1

AD2

AD3

ADTRG

PLLRC

13 Channels

PDC

PDC

USART1

RXD1

TXD1

SCK1

RTS1

CTS1

DCD1

DSR1

DTR1

RI1

PDC

PDC

PDC

PDC

SPI0

PDC

ADC

ADVREF

PDC

PDC

TC0

TC1

TC2

TWD

TWCK

TWI

OSC

XIN

XOUT

VDDIN

PWMC

PWM0

PWM1

PWM2

PWM3

1.8 V

Voltage

Regulator

USB Device

FIFO

DDM

DDP

Transceiver

GND

VDDOUT

BOD

VDDCORE

VDDCORE

VDDFLASH

AD4

AD5

AD6

AD7

VDDFLASH

Fast Flash

Programming

Interface

ERASE

PIO

PGMD0-PGMD15

PGMNCMD

PGMEN0-PGMEN1

PGMRDY

PGMNVALID

PGMNOE

PGMCK

PGMM0-PGMM3

VDDIO

TST

DBGU

PDC

PDC

PIT

WDT

RTT

System Controller

VDDCORE

CAN

CANRX

CANTX

PIO

Ethernet MAC 10/100

ETXCK-ERXCK-EREFCK

ETXEN-ETXER

ECRS-ECOL, ECRSDV

ERXER-ERXDV

ERX0-ERX3

ETX0-ETX3

EMDC

EMDIO

DMA

FIFO

PIOB

SPI1_NPCS0

SPI1_NPCS1

SPI1_NPCS2

SPI1_NPCS3

SPI1_MISO

SPI1_MOSI

SPI1_SPCK

PDC

PDC

SPI1

EF100

SAM-BA

ROM

VDDFLASH

5

6120H–ATARM–17-Feb-08

AT91SAM7X512/256/128 Preliminary

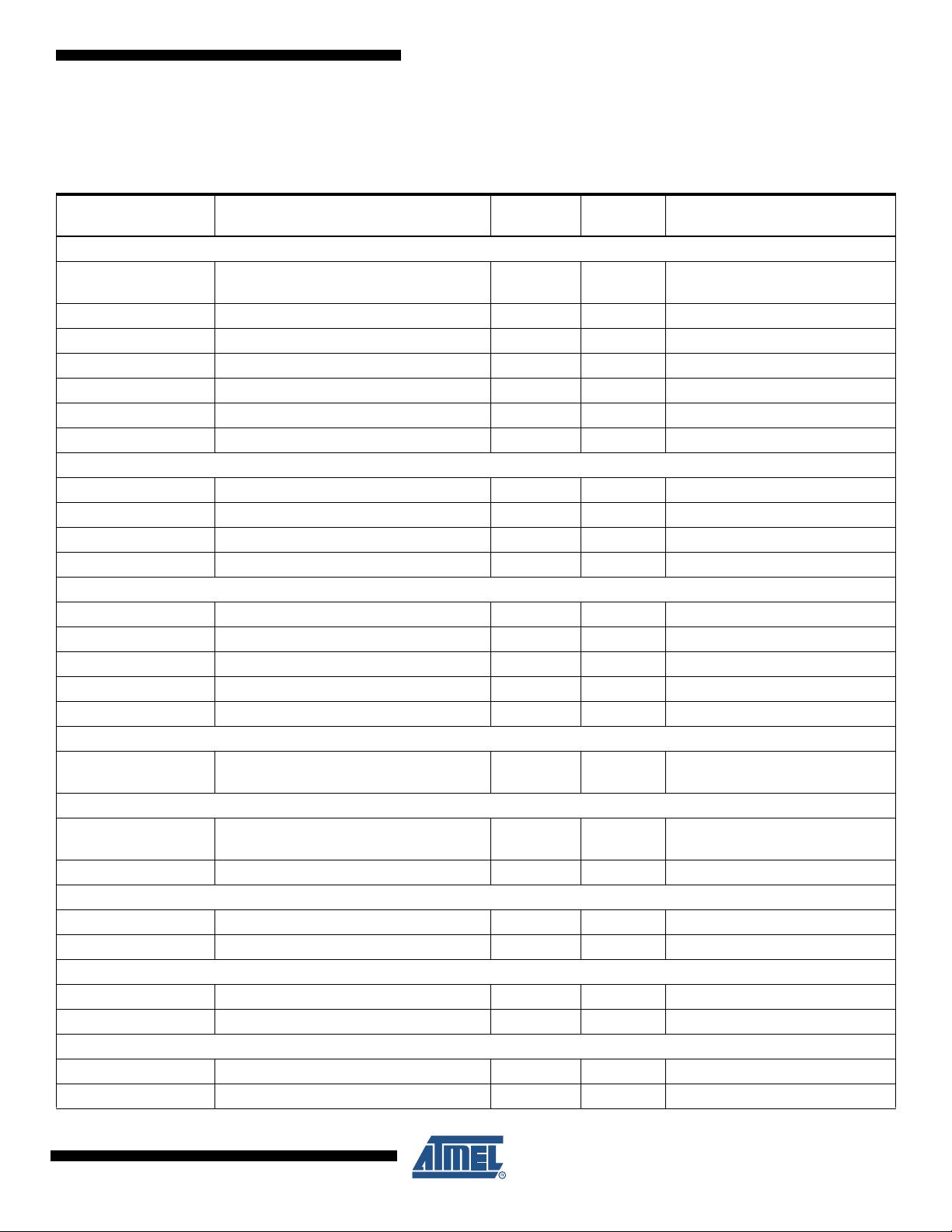

3. Signal Description

Table 3-1. Signal Description List

Signal Name Function Type

Active

Level Comments

Power

VDDIN

Voltage Regulator and ADC Power

Supply Input

Power 3V to 3.6V

VDDOUT Voltage Regulator Output Power 1.85V

VDDFLASH Flash and USB Power Supply Power 3V to 3.6V

VDDIO I/O Lines Power Supply Power 3V to 3.6V

VDDCORE Core Power Supply Power 1.65V to 1.95V

VDDPLL PLL Power 1.65V to 1.95V

GND Ground Ground

Clocks, Oscillators and PLLs

XIN Main Oscillator Input Input

XOUT Main Oscillator Output Output

PLLRC PLL Filter Input

PCK0 - PCK3 Programmable Clock Output Output

ICE and JTAG

TCK Test Clock Input No pull-up resistor

TDI Test Data In Input No pull-up resistor

TDO Test Data Out Output

TMS Test Mode Select Input No pull-up resistor

JTAGSEL JTAG Selection Input Pull-down resistor

(1)

Flash Memory

ERASE

Flash and NVM Configuration Bits Erase

Command

Input High Pull-down resistor

(1)

Reset/Test

NRST Microcontroller Reset I/O Low

Pull-up resistor, Open Drain

Output

TST Test Mode Select Input High Pull-down resistor

(1)

Debug Unit

DRXD Debug Receive Data Input

DTXD Debug Transmit Data Output

AIC

IRQ0 - IRQ1 External Interrupt Inputs Input

FIQ Fast Interrupt Input Input

PIO

PA0 - PA30 Parallel IO Controller A I/O Pulled-up input at reset

PB0 - PB30 Parallel IO Controller B I/O Pulled-up input at reset

剩余686页未读,继续阅读

资源评论

xujiejia

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 自动驾驶-状态估计和定位之Error State EKF.pdf

- STM32F103ZET6+北斗

- 程序流程图的说明及图形示例

- FDN5618P-NL-VB一款SOT23封装P-Channel场效应MOS管

- Go语言基础(变量和基本类型).zip

- 基于CYCLONE2 (EP2C8Q) FPGA 设计PLL锁相环设置时钟Verilog源码Quartus工程文件.zip

- FDN372S-NL-VB一款SOT23封装N-Channel场效应MOS管

- date0425111111111111111111111

- 包含贪心算法的定义及python代码部分实现

- 自动驾驶-状态估计和定位之扩展卡尔曼滤波.pdf

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功