没有合适的资源?快使用搜索试试~ 我知道了~

基于EDA的HDB3码编码译码器设计

温馨提示

试读

31页

介绍了HDB3编码的原理和方法,提出了一种基于EDA技术实现的HDB3编码器的方法,在MAX+plusⅡ平台以硬件描述语言VHDL语言编写程序来实现传输数据的HDB3码的编码译码,并利用CPLD实验平台来实现

资源推荐

资源详情

资源评论

基于 EDA 的 HDB3 码编码译码器设计

XXX

(xxxxxxxx,xx xx xxxxxx)

摘要

HDB3 码(High Density Bip01ar Code of threecodes,三阶高密度双极性码)是数字基带通

信系统中重要组成部分之一,因其具有无直流成份,检错能力强,具有时钟恢复性

能等优点,成为 ITU 推荐使用的基带传输码型之一。具有电路简单,成本低,开发

周期短,执行速度高,升级方便等特点

[1]

。

本文首先介绍了 HDB3 编码的原理和方法,提出了一种基于 EDA 技术实现的

HDB3 编码器的方法,在 MAX+plusⅡ 平台以硬件描述语言 VHDL 语言编写程序来

实现传输数据的 HDB3 码的编码译码,并利用 CPLD 实验平台来实现。

关键词:HDB3 编码译码;EDA 技术;VHDL;数字通信;MAX+plusⅡ

The 51 SCM Temperature Control System Design Based on

RS485 Communication

Yu Yikun

(College of Physics Science and Information Engineering,Jishou University,Jishou,Hunan 416000)

Abstract

HDB3 Code (High Density Bip01ar Code of threecodes, third-order high-density

bipolar code) is a digital communication system, an important part of, because of its non-

DC components, error detection ability, with advantages such as clock recovery

performance as ITU recommended pattern of baseband transmission. A simple circuit, low

cost, short development cycle, the implementation of high speed, upgrade conveniently.

This paper introduces the principles and methods of HDB3 encoding, a technology

based on EDA's HDB3 encoder means, in the MAX + plus platform hardware Ⅱ

description language VHDL language program to realize the HDB3 code to transfer data

coding and experimental platform using CPLD to implement.

Key words:HDB3 encoding decoding; EDA technology; VHDL; digital communication;

MAX + plusⅡ

- I -

- II -

基于 EDA 的 HDB3 码编码译码器设计 绪论

第一章 绪 论

1.1 研究背景

HDB3 码(High Density Bip01ar Code of threecodes,三阶高密度双极性码)是串

行数据传输的一种重要编码方式,也是数字通信系统中重要组成部分之一。和最常

用的 NRZ 码(Non—Return Zero,非归零码)相比,HDB3 码具有很多优点,例如:

消除了 NRZ 码的直流成分,具有时钟恢复和更好的抗干扰性能,这使它更适合于

长距离信道传输。同时,HDB3 码具有较强的检错能力,当数据序列用 HDB3 码传

输时,若传输过程中出现单个误码,其极性交替变化规律将受到破坏,因而在接收

端根据 HDB3 码这一独特规律特性,可检出错误并纠正错误,同时 HDB3 码方便提

取位定时信息。因而 HDB3 码作为数据传输的一种码型,应用广泛,成为 ITU 推荐

使用的码型之一。HDB3 码编译码器的实现有多种途径,常用的解决方案是应用专

用的 HDB3 收发芯片,如选用专用 E1 收发芯片 DS2153Q 和单片机实现该码制的转

换功能

[2]

。

1.2 研究目的和意义

本 文 提 供 了 一 种 利 用 现 代 EDA 技 术 , 以 GW48EDA 为 硬 件 平 台 , 以

MAX+plusⅡ 为软件平台,以 VHDL 为开发工具,适合于 CPLD 实现的 HDB3 编码

器的设计方案。以此来增加数据的抗干扰性能和稳定性,加快数据的传输数据的速

度。

1.3.研究内容

本系统主要是将编码数据转换成 HDB3 码, 本系统的转换过程如下:

(1)输入信号进行插 V 码。

(2)加 B 码操作。

(3)通过单极性一双极性转换单元。

再将输出信号通过译码系统翻译成输入的信号。

1.4 本文结构

- 1

基于 EDA 的 HDB3 码编码译码器设计 绪论

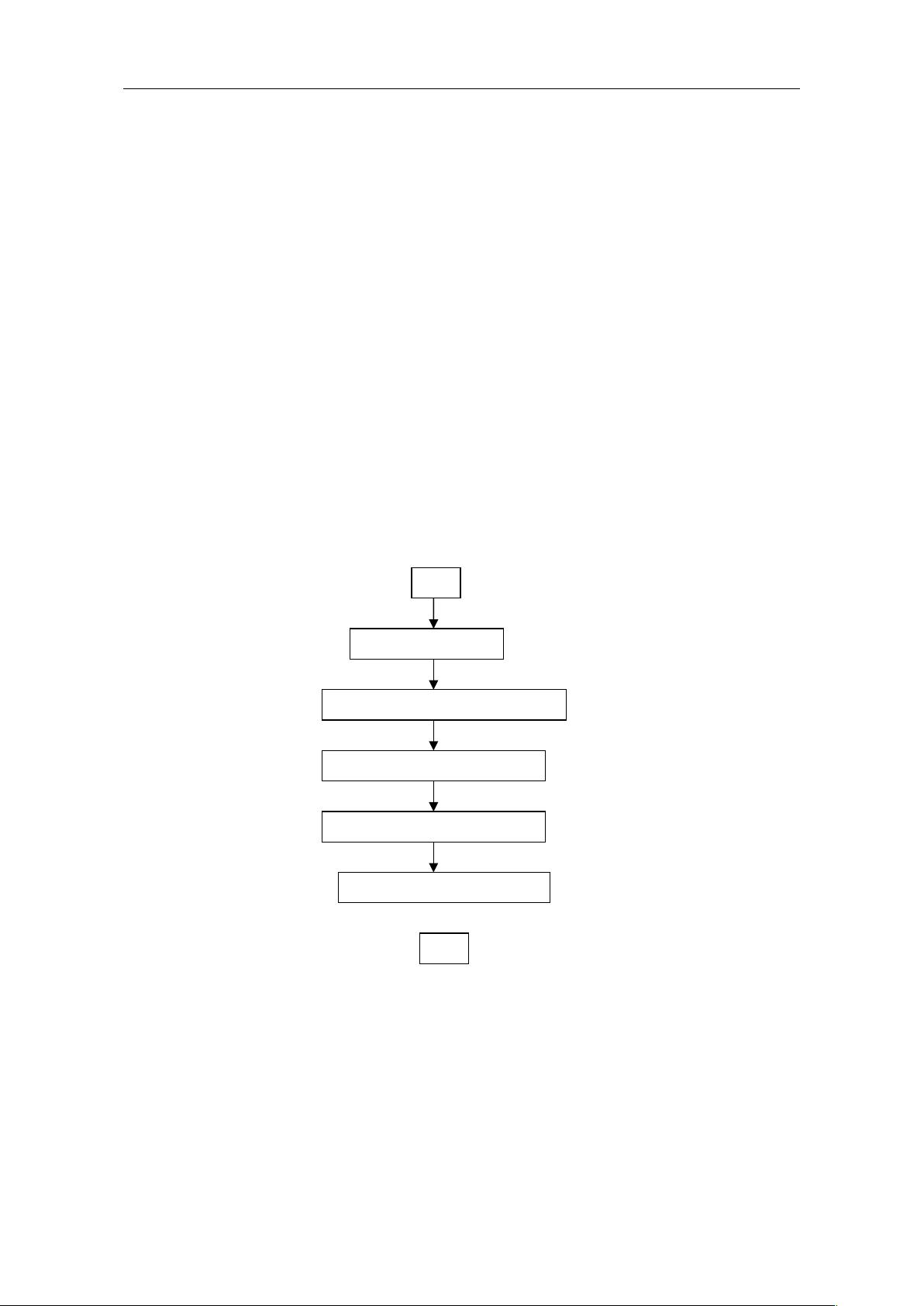

本文的结构如图 1.1

.

.

图 1.1 本文结构图

- 2

HDB3 码编码原理

HDB3 码编码器 VHDL 建模

HDB3 码编码器硬件电路设

计

HDB3 码编码器模拟仿真

HDB3 码译码设计及仿真

绪论

结束

剩余30页未读,继续阅读

资源评论

小海大鱼2012-12-31课程设计用的

小海大鱼2012-12-31课程设计用的

xlkang1987

- 粉丝: 0

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功