没有合适的资源?快使用搜索试试~ 我知道了~

W9825G6KH-带书签.pdf

需积分: 50 34 下载量 46 浏览量

2020-07-14

10:28:39

上传

评论

收藏 846KB PDF 举报

温馨提示

试读

43页

W9825G6KH-带.pdf,没有什么好说的,带,方便查看,自己编辑的,版本是A04,2017年更新的

资源推荐

资源详情

资源评论

W9825G6KH

4 M 4 BANKS 16 BITS SDRAM

Publication Release Date: Mar. 20, 2017

Revision: A04

- 1 -

Table of Contents-

1. GENERAL DESCRIPTION ......................................................................................................... 3

2. FEATURES ................................................................................................................................. 3

3. ORDER INFORMATION ............................................................................................................. 4

4. PIN CONFIGURATION ............................................................................................................... 4

5. PIN DESCRIPTION ..................................................................................................................... 5

6. BLOCK DIAGRAM ...................................................................................................................... 6

7. FUNCTIONAL DESCRIPTION .................................................................................................... 7

7.1 Power Up and Initialization ............................................................................................. 7

7.2 Programming Mode Register .......................................................................................... 7

7.3 Bank Activate Command ................................................................................................ 7

7.4 Read and Write Access Modes ...................................................................................... 7

7.5 Burst Read Command .................................................................................................... 8

7.6 Burst Write Command .................................................................................................... 8

7.7 Read Interrupted by a Read ........................................................................................... 8

7.8 Read Interrupted by a Write ............................................................................................ 8

7.9 Write Interrupted by a Write ............................................................................................ 8

7.10 Write Interrupted by a Read ............................................................................................ 8

7.11 Burst Stop Command ..................................................................................................... 8

7.12 Addressing Sequence of Sequential Mode .................................................................... 9

7.13 Addressing Sequence of Interleave Mode ...................................................................... 9

7.14 Auto-precharge Command ........................................................................................... 10

7.15 Precharge Command .................................................................................................... 10

7.16 Self Refresh Command ................................................................................................ 10

7.17 Power Down Mode........................................................................................................ 11

7.18 No Operation Command ............................................................................................... 11

7.19 Deselect Command ...................................................................................................... 11

7.20 Clock Suspend Mode .................................................................................................... 11

8. OPERATION MODE ................................................................................................................. 12

9. ELECTRICAL CHARACTERISTICS ......................................................................................... 13

9.1 Absolute Maximum Ratings .......................................................................................... 13

9.2 Recommended DC Operating Conditions .................................................................... 13

9.3 Capacitance .................................................................................................................. 14

9.4 DC Characteristics ........................................................................................................ 14

9.5 AC Characteristics and Operating Condition ................................................................ 15

10. TIMING WAVEFORMS ............................................................................................................. 17

10.1 Command Input Timing ................................................................................................ 17

10.2 Read Timing .................................................................................................................. 18

10.3 Control Timing of Input/Output Data ............................................................................. 19

10.4 Mode Register Set Cycle .............................................................................................. 20

11. OPERATING TIMING EXAMPLE ............................................................................................. 21

W9825G6KH

Publication Release Date: Mar. 20, 2017

Revision: A04

- 2 -

11.1 Interleaved Bank Read (Burst Length = 4, CAS Latency = 3) ...................................... 21

11.2 Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge) ........... 22

11.3 Interleaved Bank Read (Burst Length = 8, CAS Latency = 3) ...................................... 23

11.4 Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge) ........... 24

11.5 Interleaved Bank Write (Burst Length = 8) ................................................................... 25

11.6 Interleaved Bank Write (Burst Length = 8, Auto-precharge) ........................................ 26

11.7 Page Mode Read (Burst Length = 4, CAS Latency = 3)............................................... 27

11.8 Page Mode Read / Write (Burst Length = 8, CAS Latency = 3) ................................... 28

11.9 Auto-precharge Read (Burst Length = 4, CAS Latency = 3) ........................................ 29

11.10 Auto-precharge Write (Burst Length = 4) .................................................................... 30

11.11 Auto Refresh Cycle ..................................................................................................... 31

11.12 Self Refresh Cycle ....................................................................................................... 32

11.13 Burst Read and Single Write (Burst Length = 4, CAS Latency = 3) ............................ 33

11.14 Power Down Mode ...................................................................................................... 34

11.15 Auto-precharge Timing (Read Cycle) .......................................................................... 35

11.16 Auto-precharge Timing (Write Cycle) .......................................................................... 36

11.17 Timing Chart of Read to Write Cycle ........................................................................... 37

11.18 Timing Chart of Write to Read Cycle ........................................................................... 37

11.19 Timing Chart of Burst Stop Cycle (Burst Stop Command) .......................................... 38

11.20 Timing Chart of Burst Stop Cycle (Precharge Command) .......................................... 38

11.21 CKE/DQM Input Timing (Write Cycle) ......................................................................... 39

11.22 CKE/DQM Input Timing (Read Cycle) ......................................................................... 40

12. PACKAGE SPECIFICATION .................................................................................................... 41

13. REVISION HISTORY ................................................................................................................ 42

W9825G6KH

Publication Release Date: Mar. 20, 2017

Revision: A04

- 3 -

1. GENERAL DESCRIPTION

W9825G6KH is a high-speed synchronous dynamic random access memory (SDRAM), organized as

4M words 4 banks 16 bits. W9825G6KH delivers a data bandwidth of up to 200M words per

second. To fully comply with the personal computer industrial standard, W9825G6KH is sorted into the

following speed grades: -5, -5I, -6, -6I, -6J, -6L, -75, 75J and 75L.

The -5/-5I grade parts are compliant to the 200MHz/CL3 specification (the -5I industrial grade which is

guaranteed to support -40°C ≤ TA ≤ 85°C).

The -6/-6I/-6J/-6L grade parts are compliant to the 166MHz/CL3 specification (the -6I industrial grade

which is guaranteed to support -40°C ≤ TA ≤ 85°C, the -6J industrial plus grade which is guaranteed to

support -40°C ≤ TA ≤ 105°C).

The -75/75J/75L grade parts are compliant to the 133MHz/CL3 specification (the 75J industrial plus

grade which is guaranteed to support -40°C ≤ TA ≤ 105°C).

The -6L and 75L grade parts support self refresh current IDD6 max. 1.5 mA.

Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be

accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE

command. Column addresses are automatically generated by the SDRAM internal counter in burst

operation. Random column read is also possible by providing its address at each clock cycle. The

multiple bank nature enables interleaving among internal banks to hide the precharging time.

By having a programmable Mode Register, the system can change burst length, latency cycle,

interleave or sequential burst to maximize its performance. W9825G6KH is ideal for main memory in

high performance applications.

2. FEATURES

3.3V ± 0.3V Power Supply

Up to 200 MHz Clock Frequency

4,194,304 Words 4 Banks 16 Bits Organization

Self Refresh Mode: Standard and Low Power

CAS Latency: 2 and 3

Burst Length: 1, 2, 4, 8 and Full Page

Burst Read, Single Writes Mode

Byte Data Controlled by LDQM, UDQM

Power Down Mode

Auto-precharge and Controlled Precharge

8K Refresh Cycles/64 mS, @ -40°C ≤ TA ≤ 85°C

8K Refresh Cycles/16 mS, @ 85°C < TA ≤ 105°C

Interface: LVTTL

Packaged in TSOP II 54-pin, 400 mil - 0.80, using Lead free materials with RoHS compliant

Note: Not support self refresh function with TA > 85°C

W9825G6KH

Publication Release Date: Mar. 20, 2017

Revision: A04

- 4 -

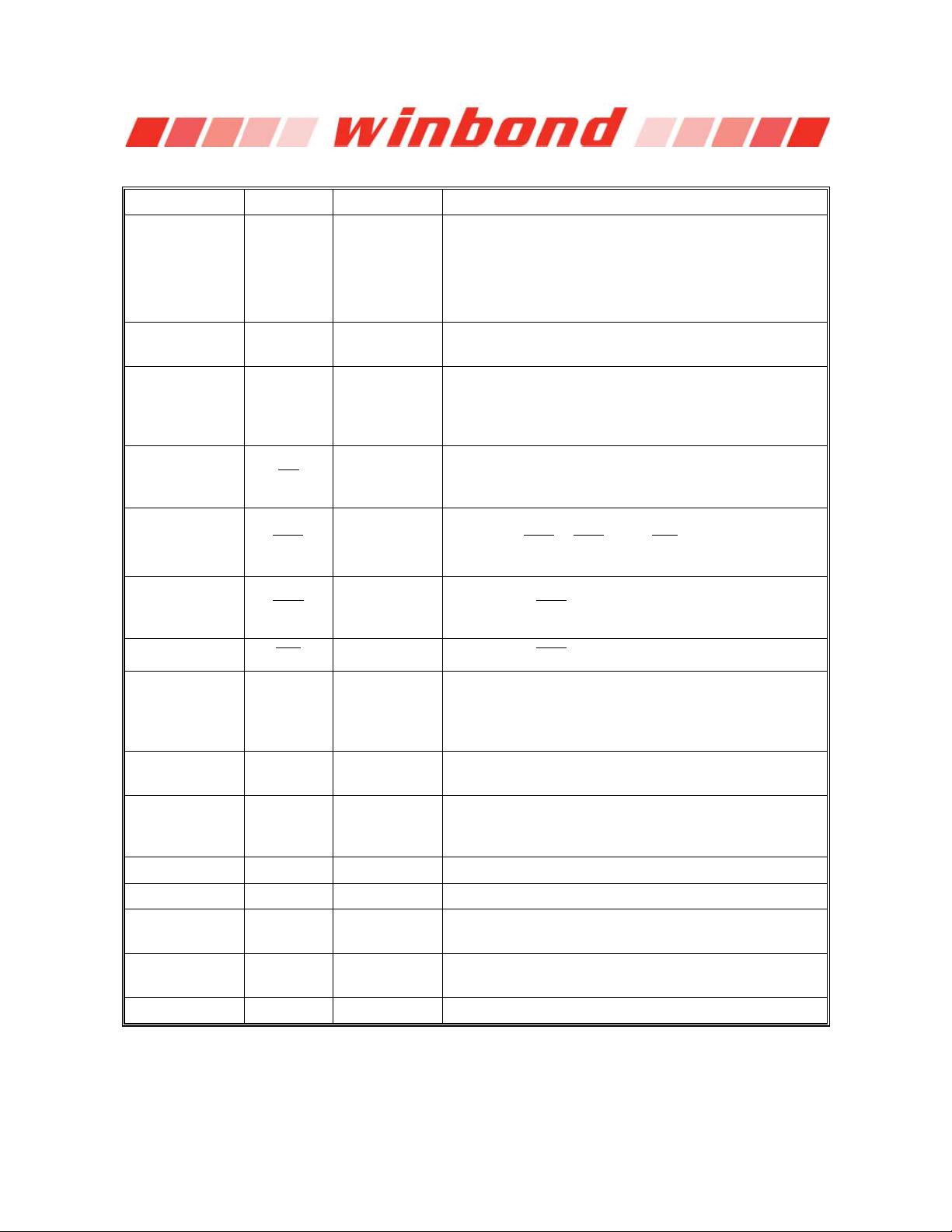

3. ORDER INFORMATION

PART NUMBER

SPEED GRADE

SELF REFRESH

CURRENT (MAX)

OPERATING

TEMPERATURE

W9825G6KH-5

200MHz/CL3 or 133MHz/CL2

2 mA

0°C ~ 70°C

W9825G6KH-5I

200MHz/CL3 or 133MHz/CL2

2 mA

-40°C ~ 85°C

W9825G6KH-6

166MHz/CL3 or 133MHz/CL2

2 mA

0°C ~ 70°C

W9825G6KH-6I

166MHz/CL3 or 133MHz/CL2

2 mA

-40°C ~ 85°C

W9825G6KH-6J

166MHz/CL3 or 133MHz/CL2

5 mA

-40°C ~ 105°C

W9825G6KH-6L

166MHz/CL3 or 133MHz/CL2

1.5 mA

0°C ~ 70°C

W9825G6KH-75

133MHz/CL3 or 100MHz/CL2

2 mA

0°C ~ 70°C

W9825G6KH75J

133MHz/CL3 or 100MHz/CL2

5 mA

-40°C ~ 105°C

W9825G6KH75L

133MHz/CL3 or 100MHz/CL2

1.5 mA

0°C ~ 70°C

4. PIN CONFIGURATION

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

VSS

NC

UDQM

CLK

CKE

A12

A11

A9

A8

A7

A6

A5

A4

VSS

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

VDD

DQ0

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

VDD

LDQM

BS0

BS1

A10/AP

A0

A1

A2

A3

VDD

CS

RAS

CAS

WE

VDDQ

W9825G6KH

Publication Release Date: Mar. 20, 2017

Revision: A04

- 5 -

5. PIN DESCRIPTION

PIN NUMBER

PIN NAME

FUNCTION

DESCRIPTION

2326, 2934,

22, 35, 36

A0A12

Address

A0A8Multiplexed pins for row and column address.

Row address: A0A12. Column address: A0A8.

A10 is sampled during a precharge command to

determine if all banks are to be precharged or bank

selected by BS0, BS1.

20, 21

BS0, BS1

Bank Select

Select bank to activate during row address latch time, or

bank to read/write during address latch time.

2, 4, 5, 7, 8, 10,

11, 13, 42, 44,

45, 47, 48, 50,

51, 53

DQ0DQ15

Data

Input/Output

Multiplexed pins for data output and input.

19

CS

Chip Select

Disable or enable the command decoder. When

command decoder is disabled, new command is

ignored and previous operation continues.

18

RAS

Row Address

Strobe

Command input. When sampled at the rising edge of

the clock,

RAS

,

CAS

and

WE

define the

operation to be executed.

17

CAS

Column

Address

Strobe

Referred to

RAS

16

WE

Write Enable

Referred to

RAS

15, 39

LDQM,

UDQM

Input/Output

Mask

The output buffer is placed at Hi-Z(with latency of 2)

when DQM is sampled high in read cycle. In write

cycle, sampling DQM high will block the write

operation with zero latency.

38

CLK

Clock Inputs

System clock used to sample inputs on the rising edge

of clock.

37

CKE

Clock Enable

CKE controls the clock activation and deactivation.

When CKE is low, Power Down mode, Suspend mode,

or Self Refresh mode is entered.

1, 14, 27

VDD

Power

Power for input buffers and logic circuit inside DRAM.

28, 41, 54

VSS

Ground

Ground for input buffers and logic circuit inside DRAM.

3, 9, 43, 49

VDDQ

Power

for I/O Buffer

Separated power from VDD, to improve DQ noise

immunity.

6, 12, 46, 52

VSSQ

Ground

for I/O Buffer

Separated ground from VSS, to improve DQ noise

immunity.

40

NC

No Connection

No connection.

剩余42页未读,继续阅读

资源评论

M小博士

- 粉丝: 8

- 资源: 15

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功