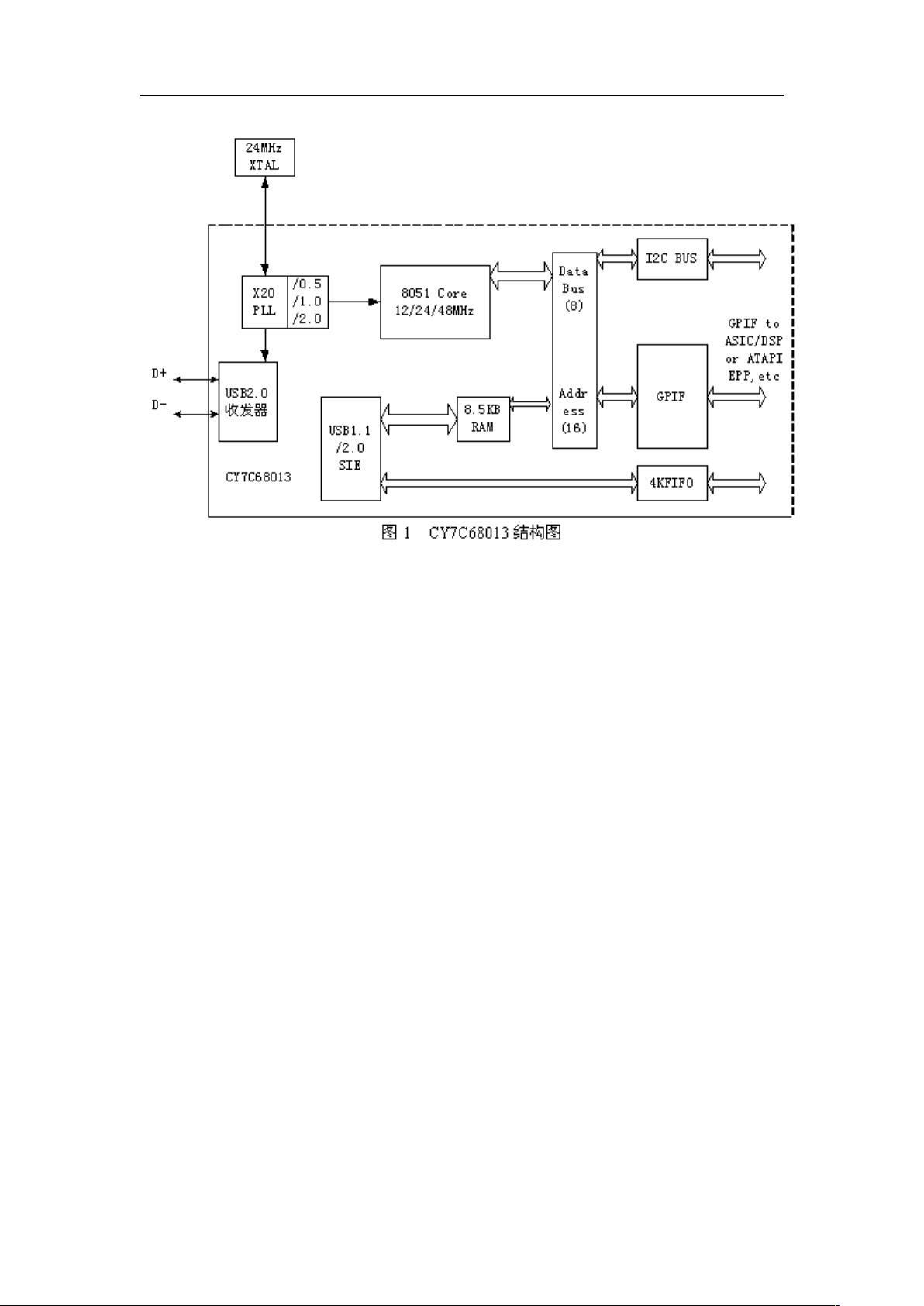

根据给定的文件信息,以下是对“68013 slave fifo 说明文档”相关知识点的详细解析: ### 一、FX2特性介绍 #### 1.1 引入 FX2是由Cypress Semiconductor公司推出的创新产品,作为全球首款集成USB 2.0功能的微处理器,FX2融合了USB 2.0收发器、串行接口引擎(SIE)、增强型8051微控制器以及可编程外围接口。这一集成设计不仅实现了高达56MB/s的数据传输速度,符合USB 2.0规定的最大带宽标准,而且其智能SIE能够硬件层面处理众多USB 1.1和USB 2.0协议,显著降低了开发周期并保障了与USB标准的兼容性。 #### 1.2 结构 FX2的结构复杂而精细,采用三种封装形式:56SSOP、100TQFP和128TQFP,满足不同应用场景的需求。其中,GPIF(General Programmable Interface)和主/从端点FIFO(支持8位或16位数据总线)为多种接口提供了无缝连接的可能,如ATA、UTOPIA、EPP、PCMCIA和DSP等,极大地拓宽了FX2的应用范围。 #### 1.3 特征 - **高速收发器**:内置480Mbps收发器、锁相环(PLL)以及SIE,完全覆盖USB 2.0协议的物理层需求。 - **高速FIFO端点**:为了匹配USB 2.0的高速率(480Mbps),FX2的FIFO端点可灵活配置为2、3或4个缓冲区,增强了数据处理能力和系统响应速度。 ### 二、Slave FIFO传输 #### 2.1 概述 Slave FIFO传输机制是FX2实现高效数据交换的关键技术之一。通过不同的传输模式,FX2能够支持多样化的数据流控制,满足复杂通信环境下的需求。 #### 2.2 硬件连接 FX2的硬件连接设计灵活,能够适应各种外部设备的接口标准,通过合理的配置实现高效的信号交互。 #### 2.3 Slave FIFO的几种传输方式 - **同步Slave FIFO写**:此模式下,数据写入操作与主机的时钟信号同步,确保数据的准确无误传输。 - **同步Slave FIFO读**:类似地,数据读取过程也遵循主机时钟同步,保证数据读取的可靠性。 - **异步Slave FIFO写**:异步模式下的数据写入,不受主机时钟约束,适用于实时性要求不高的场景。 - **异步Slave FIFO读**:异步读取数据,提供更宽松的时间窗口,适合处理非时间敏感的数据传输任务。 ### 三、寄存器设置 FX2的寄存器设置是实现特定功能的基础,包括IFCONFIG、PINFLAGSAB/CD、FIFORESET等在内的多个寄存器,分别用于配置设备的接口模式、引脚功能、FIFO复位状态等,是理解并掌握FX2操作不可或缺的部分。 ### 四、同步slavefifo测试操作指南 本部分详细介绍了如何进行同步slavefifo的测试操作,从软件包的安装,到具体测试步骤的执行,为开发者提供了清晰的操作流程,确保能够正确无误地验证FX2的Slave FIFO功能。 ### 五、艾曼技术II开发板USB2FPGA软件设计 针对艾曼技术II开发板,章节讲述了68013固件程序设计与FPGA源代码设计,深入探讨了如何利用FX2构建高性能的USB至FPGA通信系统。 ### 六、USB2FPGA硬件原理图 提供了USB2FPGA硬件电路的详细原理图,对于硬件工程师而言,这是实现系统设计的重要参考依据。 ### 七、改板后注意的问题 在对开发板进行修改或升级后,需特别关注可能出现的兼容性问题、信号完整性问题等,确保系统的稳定性和可靠性。 通过以上分析,可以看出“68013 slave fifo 说明文档”全面而深入地介绍了FX2芯片的特性和应用,为从事USB通信技术研究与开发的专业人士提供了宝贵的参考资料。

剩余40页未读,继续阅读

- 粉丝: 3

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功