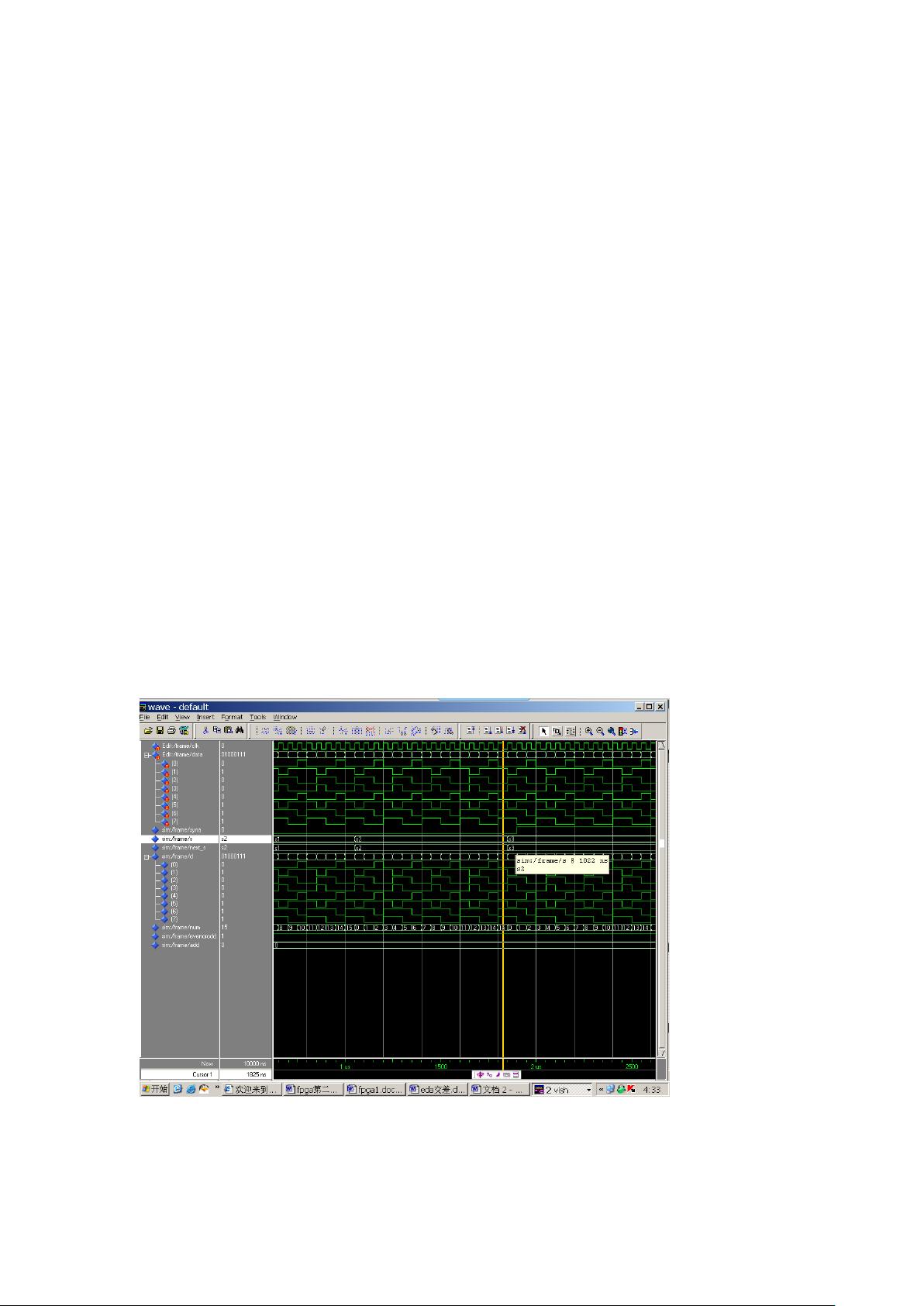

1、 仿真中是利用 modelsim 软件的自带加载仿真数据功能实现的仿真。所以没有编仿真数

据文件。数据流依次是(47)01000111 00110011 01100110 11001100。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY frame IS

PORT (clk:IN STD_LOGIC;

data: IN STD_LOGIC_vector(0 to 7);

syna:OUT STD_LOGIC);

END frame;

ARCHITECTURE behavior OF frame IS

TYPE state IS(s0,s1,s2,s3,s4);

SIGNAL s,next_s:state; 记录状态

SIGNAL d:STD_LOGIC_vector(0 to 7); 描述数据流

SIGNAL num:INTEGER RANGE 0 TO 15; num 用来找到祯头计数祯长的

SIGNAL evenorodd:STD_LOGIC; 记录是否找到祯

SIGNAL add:INTEGER RANGE 0 TO 2; 记录出错次数

BEGIN

PROCESS(clk,data) 逐字节找祯头

BEGIN

IF (next_s/=s0) and rising_edge(clk)THEN

IF num=15 THEN num<=0;

ELSE num<=num+1;

END IF;

d<=data;

ELSIF rising_edge(clk) THEN

d<=data;

END IF;

END PROCESS;

PROCESS(next_s) 状态转换

BEGIN

s<= next_s;

END PROCESS;

process(clk) 进入状态机

BEGIN

IF clk'event AND clk='1'THEN

CASE s IS

WHEN s0=>

IF d ="01000111"THEN

next_s <=s1;

syna<='0';