SPI Core

Specifications

Author: Richard Herveille

rherveille@opencores.org

Document rev. 0.1

January 7, 2003

This page left intentionally blank

OpenCores Simple SPI Core datasheet 1/7/2003

www.opencores.org Rev 0.1 Preliminary

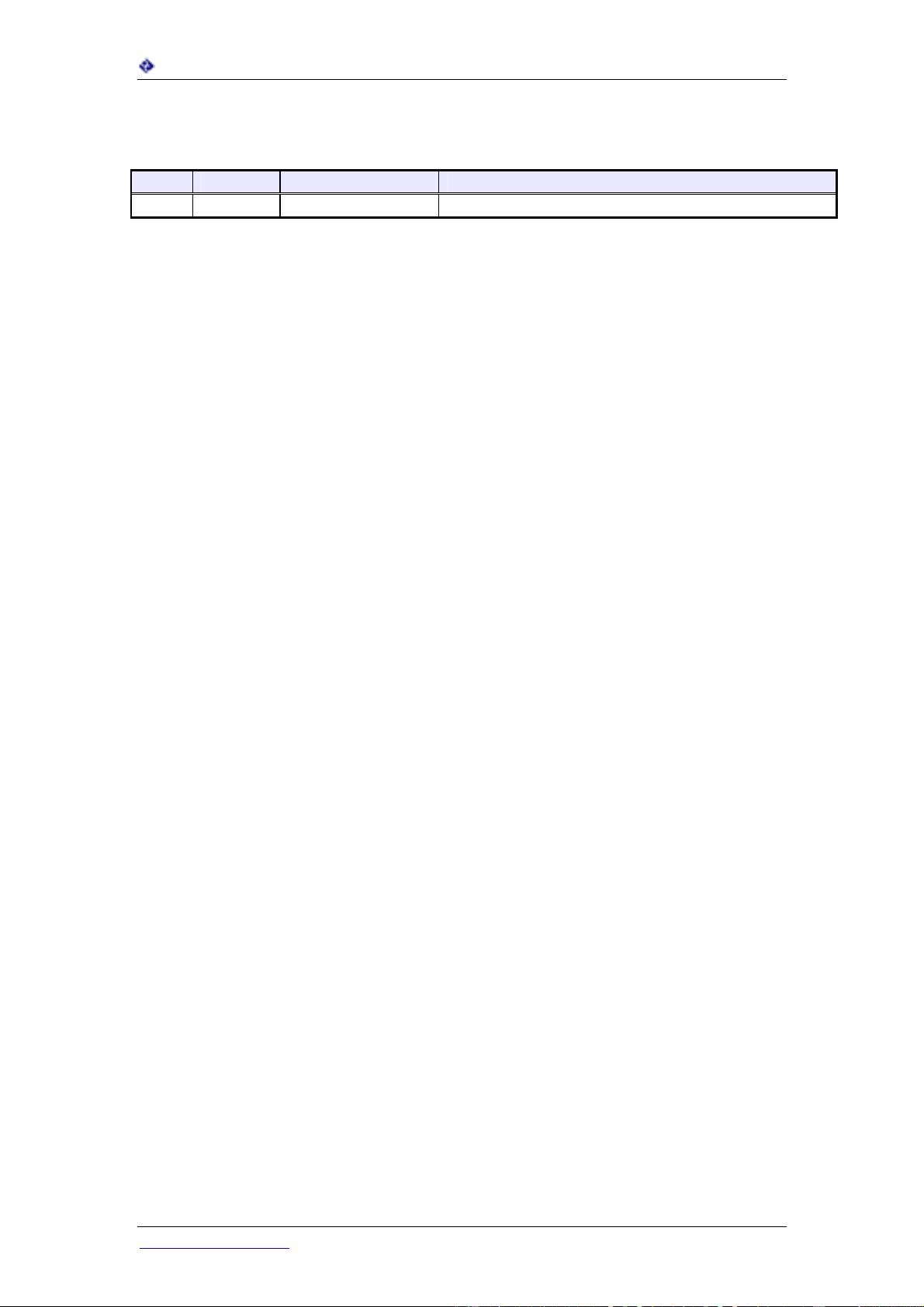

Revision History

Rev. Date Author Description

0.1 07/01/02 Richard Herveille First Draft

OpenCores Simple SPI Core datasheet 1/7/2003

www.opencores.org Rev 0.1 Preliminary

Table of contents

INTRODUCTION........................................................................................................1

IO PORTS.....................................................................................................................2

REGISTERS.................................................................................................................4

OPERATION................................................................................................................8

ARCHITECTURE .....................................................................................................10

OpenCores Simple SPI Core datasheet 1/7/2003

www.opencores.org Rev 0.1 Preliminary 1 of 40

1

Introduction

The OpenCores simple Serial Peripheral Interface core is an enhanced version of the

Serial Peripheral Interface found on Motorola's M68HC11 family of CPUs. The Serial

Peripheral Interface is a serial, synchronous communication protocol that requires a

minimum of 3 wires. Enhancements to the original interface include a wider

supported operating frequency range, 4 entries deep read and write FIFOs, and

programmable transfer count dependent interrupt generation. The high compatibility

with the M68HC11 SPI port ensures that existing software can use this core without

major modifications. New software can use existing examples as a starting point.

The core features an 8 bit wishbone interface.

FEATURES:

• Compatible with Motorola’s SPI specifications

• Enhanced M68HC11 Serial Peripheral Interface

• 4 entries deep read FIFO

• 4 entries deep write FIFO

• Interrupt generation after 1, 2, 3, or 4 transferred bytes

• 8 bit WISHBONE RevB.3 Classic interface

• Operates from a wide range of input clock frequencies

• Static synchronous design

• Fully synthesizable