http://www.paper.edu.cn

- 1 -

WCDMA 主同步的 FPGA 实现

高展宏

北京邮电大学信息工程学院,北京(100876)

E-mail:darney1982@yahoo.com.cn

摘 要:本文阐述了主同步搜索的改进型算法,并且针对这种算法提出了基于片上 RAM 的

实现方式,最大程度地节省了 FPGA 的硬件资源,为 WCDMA 同步的 FPGA 实现提供了很

好的解决方案。这种技术可以用于其它多种匹配滤波结构。

关键词:FPGA,P-SCH,匹配滤波

中图分类号:TN929.5

1. 引言

主同步是 WCDMA 中的第一步同步,同时对整个同步来说也是最重要的一个环节。不

过对于实时系统来说,如果要让主同步检测也是在实时的限制条件下工作的,那么就需要考

虑资源和速度的平衡问题,同时主同步搜索基于的算法也必需能够满足。

2. 系统介绍

2.1 PSCH 信道

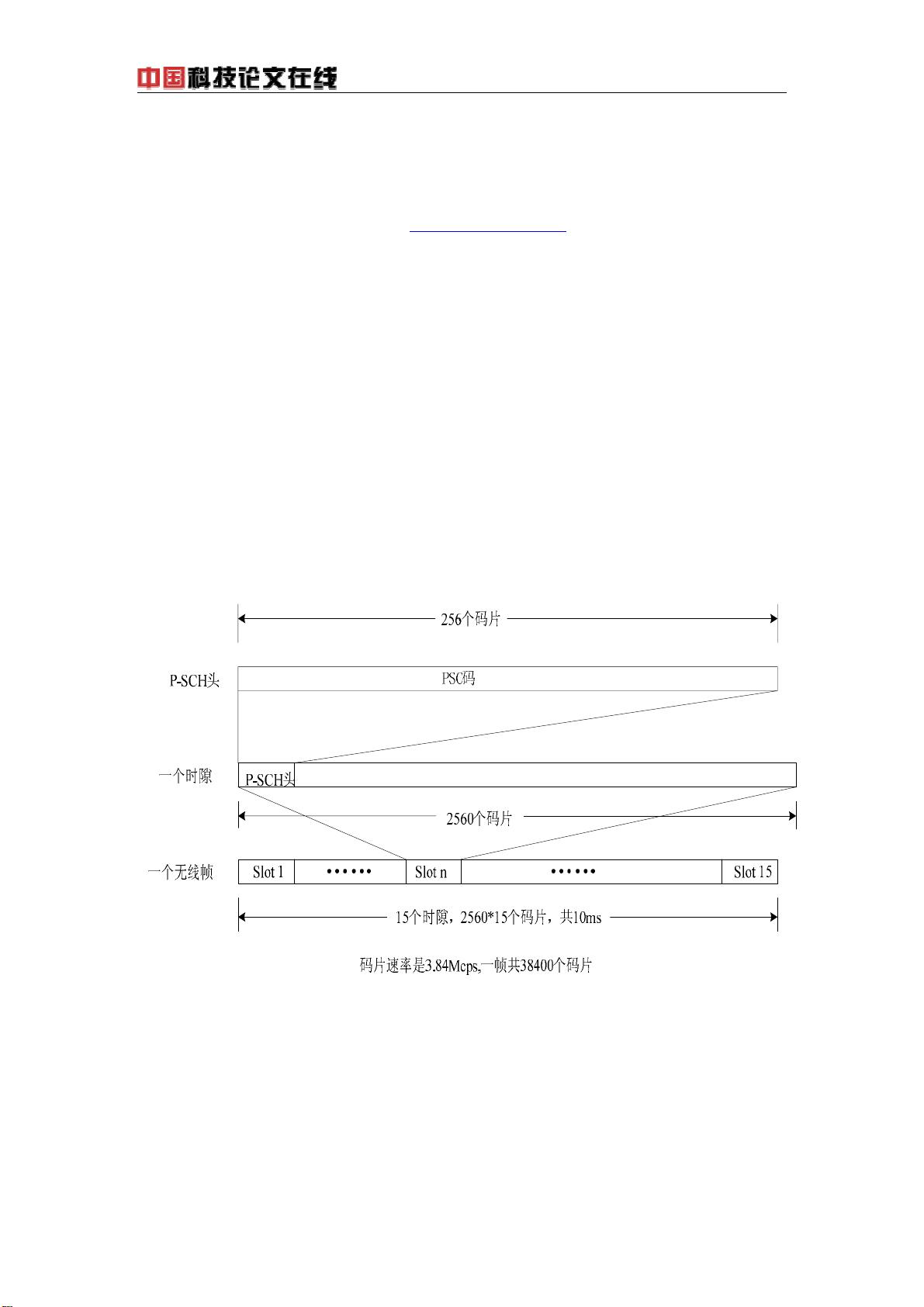

图 1 WCDMA的 P-SCH 信道结构

可以看到,WCDMA 的 P-SCH 信道给我们提供了很好的时隙同步信号。我们的任务就

是把用本地的 PSC 码序列和接收到的 P-SCH 路信号进行同步。

[1]

2.2 PSC 码生成原理

P-SCH 信道由 PSC(主同步码)码构成,是由所谓广义分层 Golay 序列构成的。