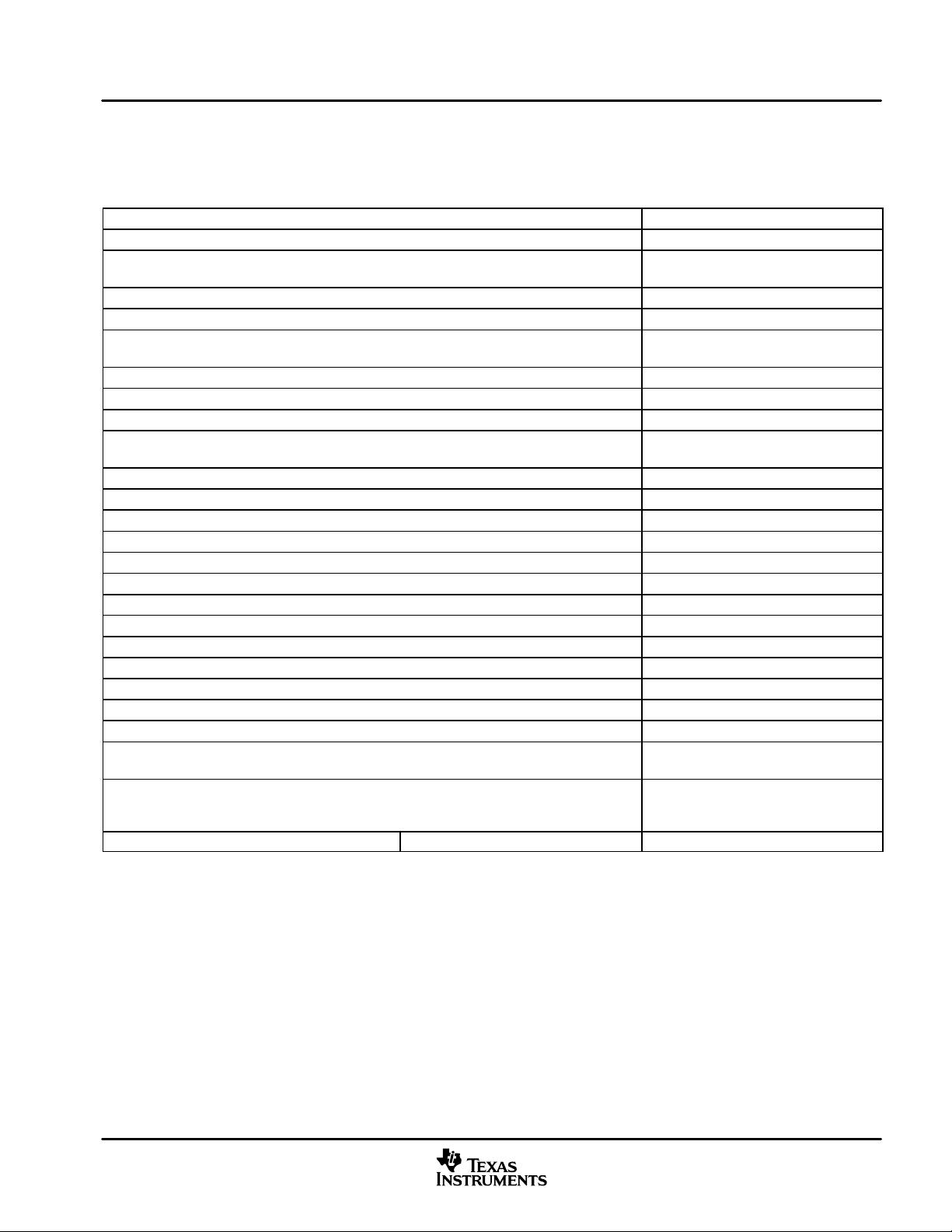

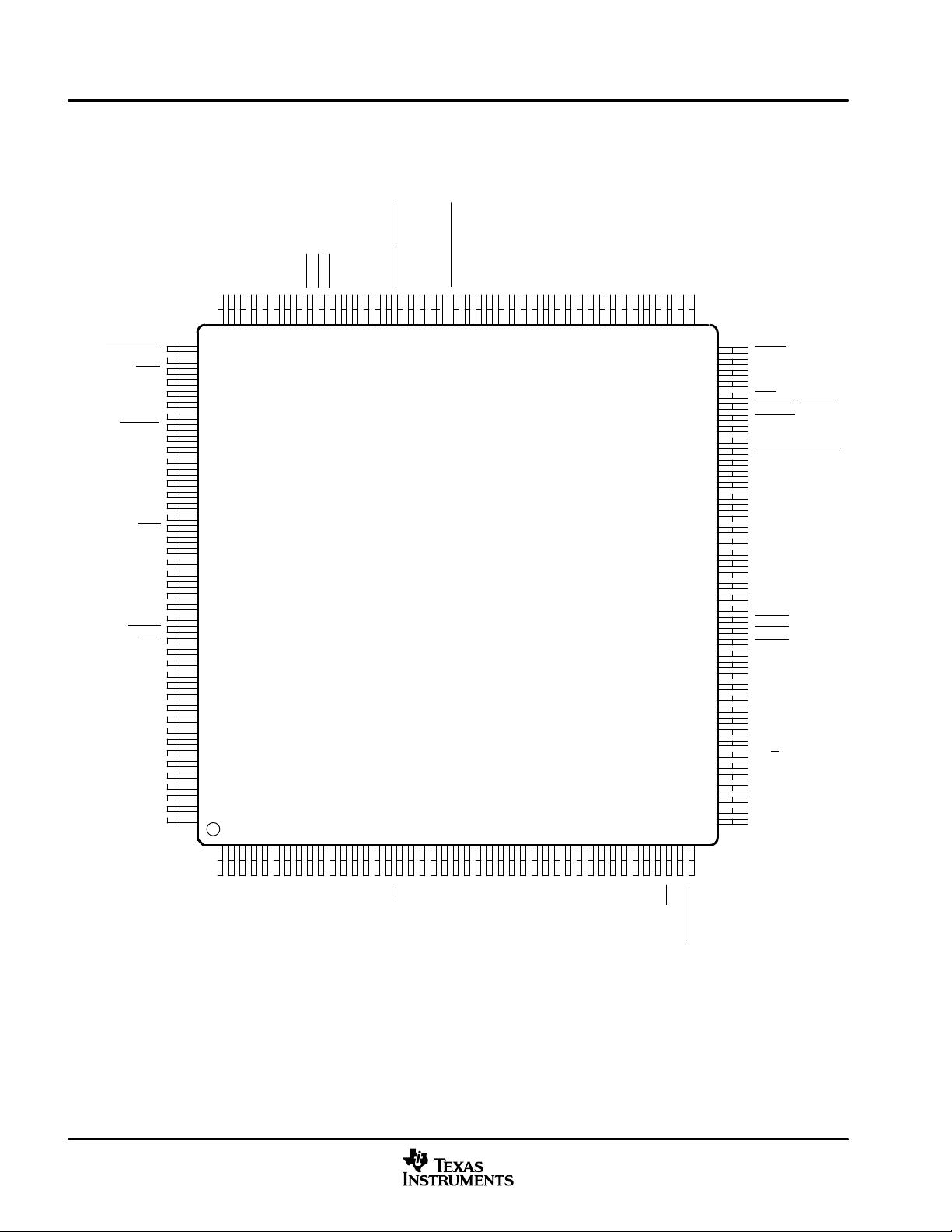

DSP 芯片 SMJ320F2812 使用说明书 DSP 芯片 SMJ320F2812 是一款高性能的数字信号处理器,具有高达 150MHz 的时钟频率和低功耗设计。该芯片基于 32 位 CPU架构,具有 Harvard 总线结构、快速中断响应和处理、统一存储器编程模型等特点。 高性能静态 CMOS 技术 SMJ320F2812 采用高性能静态 CMOS 技术,具有低功耗设计,核心电压为 1.8V,时钟频率为 135MHz;核心电压为 1.9V,时钟频率为 150MHz;I/O 电压为 3.3V。 JTAG 边界扫描支持 该芯片支持 JTAG 边界扫描,方便对芯片的调试和测试。 高性能 32 位 CPU SMJ320F2812 的 CPU基于 TMS320C28x 架构,具有 16×16 和 32×32 MAC 操作、16×16 双 MAC 操作、Harvard 总线结构、原子操作、快速中断响应和处理、统一存储器编程模型等特点。 On-Chip 存储器 该芯片具有丰富的 On-Chip 存储器资源,包括:Flash 设备:最高 128Kx16 位 Flash(四个 8Kx16 和六个 16Kx16扇区);ROM 设备:最高 128Kx16 位 ROM;1Kx16OTP ROM;L0 和 L1:两个 4Kx16 位 SARAM 块;H0:一个 8Kx16 位 SARAM 块;M0 和 M1:两个 1Kx16 位 SARAM 块。 Boot ROM 该芯片具有 4Kx16 位 Boot ROM,支持软件启动模式,内置标准数学表。 外部接口 SMJ320F2812 具有丰富的外部接口资源,包括:最高 1M 总存储器;可编程等待状态;可编程读/写脉冲定时器;三个独立的芯片选择。 时钟和系统控制 该芯片具有动态 PLL 比例变化支持、on-chip振荡器和看门定时器模块。 外部中断 SMJ320F2812 具有三个外部中断输入。 外围设备中断扩展 (PIE) 块 该芯片具有 PIE 块,支持 45 个外围设备中断。 128 位安全密钥/锁 该芯片具有 128 位安全密钥/锁,保护 Flash/ROM/OTP 和 L0/L1 SARAM,防止固件反向工程。 三個 32 位 CPU 计时器 SMJ320F2812 具有三个 32 位 CPU 计时器。 电机控制外围设备 该芯片具有两个事件管理器 (EVA, EVB),与 240xA 设备兼容。 串行端口外围设备 SMJ320F2812 具有串行外围接口 (SPI) 和两个串行通信接口。 SMJ320F2812 是一款功能强大、高性能的数字信号处理器,适合用于各种数字信号处理应用。

剩余139页未读,继续阅读

- 粉丝: 1

- 资源: 6

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功

评论0