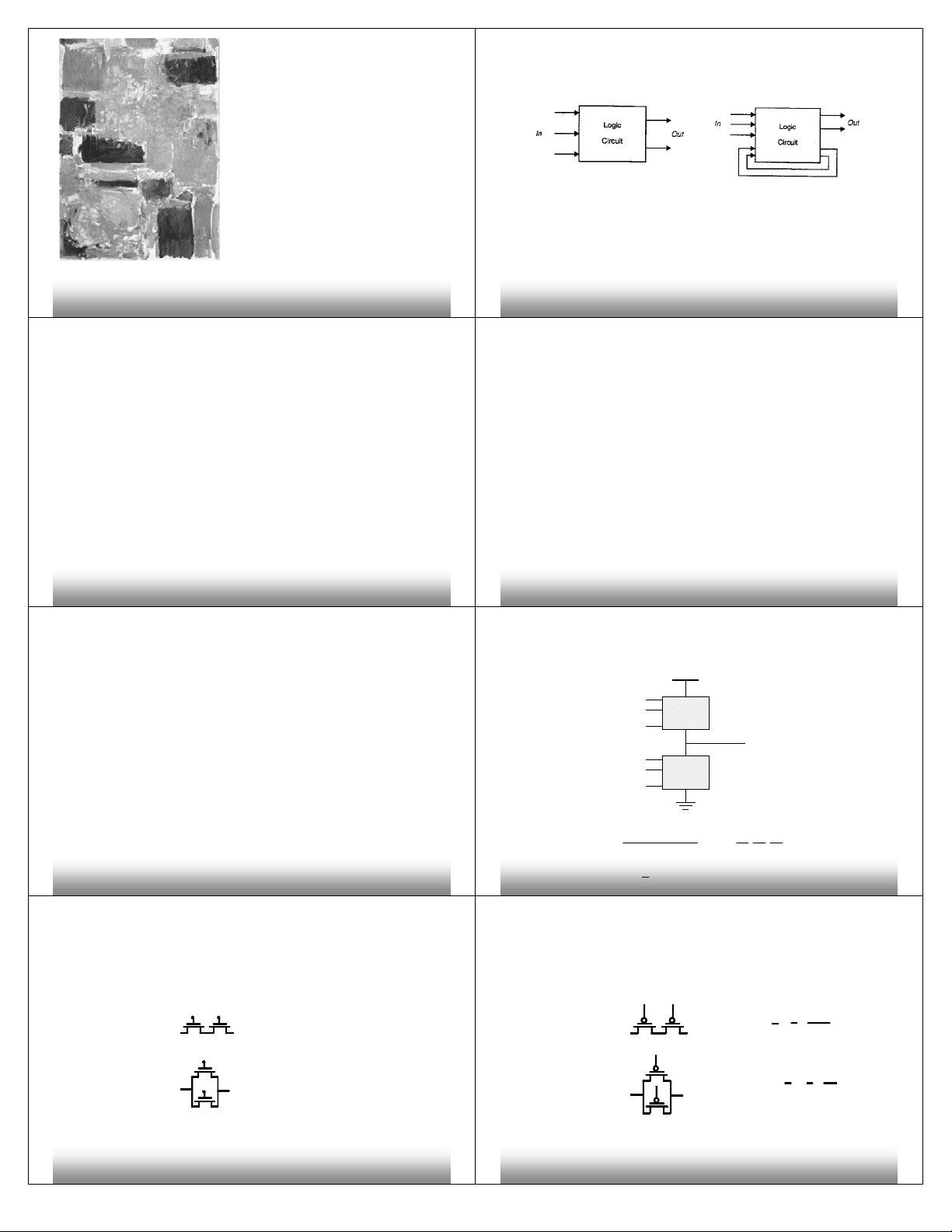

数字集成电路的设计是一个复杂的过程,其中组合逻辑电路的设计是基础。组合逻辑电路与时序逻辑电路是数字电路设计的两大类别。组合逻辑电路的特点是输出完全由当前输入决定,不存在内部状态,即电路没有记忆功能。而时序逻辑电路则包含存储元件,其输出不仅依赖于当前输入,还依赖于电路先前的状态。 在组合逻辑电路设计中,通常关注的是如何通过逻辑门构建出复杂的逻辑功能,实现对输入信号的处理。逻辑门如反相器(NOT门)、与非门(NAND门)、或非门(NOR门)等是最基础的构建模块。这些门电路能够根据输入的布尔逻辑值来控制输出。反相器是最简单的组合逻辑电路,其输出与输入相反。在更复杂的逻辑设计中,我们可能会使用到更复杂的逻辑门,比如异或门、或门等,以及它们的组合来实现复杂的逻辑功能。 静态CMOS技术在组合逻辑电路设计中占据重要地位。它由两部分组成:P型和N型场效应晶体管的网络,分别称为P型上拉网络(PUN)和N型下拉网络(PDN),它们是互补的逻辑网络。CMOS电路的优点在于它们只在开关瞬间消耗功率,而在静态时几乎不耗电。这种特性让CMOS成为了当今数字集成电路设计的主流技术。 在设计中,评价标准包括面积、速度、能量和功耗以及抗噪声能力和可靠性。对于复杂的逻辑门,可以通过不同类型的逻辑网络来构建。这些网络通常包括通用逻辑门和数据通路单元。通用逻辑门适用于可以综合的逻辑设计,而数据通路单元则用于实现算术运算等特定功能。 动态CMOS技术也是组合逻辑电路设计的一部分,它的运行原理与静态CMOS不同,主要依赖于高阻节点暂存电荷来维持信号。动态CMOS电路在结构上更简单,寄生电容小,因而速度较快,但是它们对噪声更为敏感。 在数字集成电路中,晶体管的串联和并联也是常见的结构。在NMOS和PMOS晶体管中,串联意味着晶体管将信号的通断组合起来,而并联则是通过不同路径实现同一信号的多重传输。NMOS晶体管在栅输入高电平时导通,而PMOS晶体管则在栅输入低电平时导通。晶体管的这种特性影响了电路的传输特性,如NMOS晶体管能够传输0(强0)和较弱的1信号,而PMOS晶体管则相反。 此外,CMOS逻辑电路设计遵循DeMorgan定律,这是一个重要的原理,它简化了逻辑表达式的转换。它指出,一个NAND门的输出等于其输入的AND门的输出的反相,而NOR门的输出等于其输入的OR门的输出的反相。 在实际应用中,标准单元版图方法是一种广泛使用的集成电路设计方法。它允许集成电路的布局通过标准单元的重复来实现,这些单元包括反相器、与非门和或非门等。这种方法的优势在于它能够优化电路的速度、功耗、面积等指标。 组合逻辑电路的设计还需要考虑到晶体管的物理层面。例如,N阱是指在P型衬底中的N型半导体区域,它使得可以在一个衬底上集成多种类型的晶体管。而单元边界是电路中不同逻辑单元的分界线。在单元版图中,会使用符号化版图来表示晶体管的相对位置和连接方式,而棒图则展示了不同逻辑电路的逻辑曲线。 为了实现特定的逻辑功能,比如实现逻辑表达式C=(A+B)(A+B),设计者需要构建相应的电路,并理解各种门电路如何结合起来产生预期的逻辑输出。这涉及到电路的逻辑设计、版图设计、物理实现等复杂的过程。 在数字集成电路设计中,Euler通路是指一种可以在图形中仅通过走遍每一条边一次的方式来遍历图中所有节点的路径。在实际电路设计中,Euler通路能够帮助设计者解决电路中的某些特定问题。 组合逻辑电路的设计需要对基本逻辑门有深刻理解,并结合CMOS技术的特点,通过标准单元版图方法实现集成电路的物理设计。设计者需要考虑到电路的逻辑功能、面积、速度、能量和功耗、抗噪声能力和可靠性等评价指标,并解决电路设计中出现的各种问题。最终设计出来的集成电路需要满足功能需求同时达到设计规范中的性能标准。

- 粉丝: 7

- 资源: 880

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功