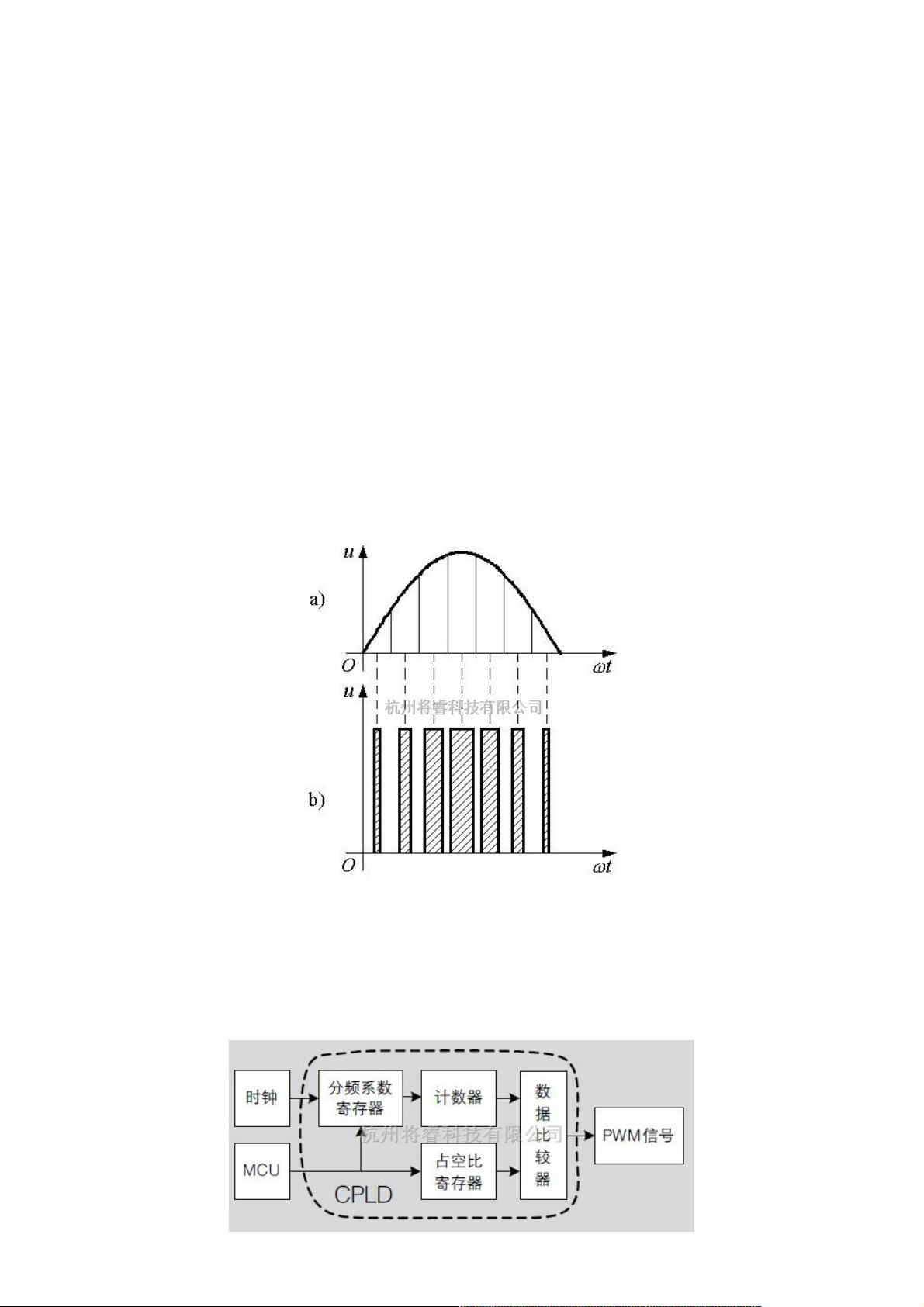

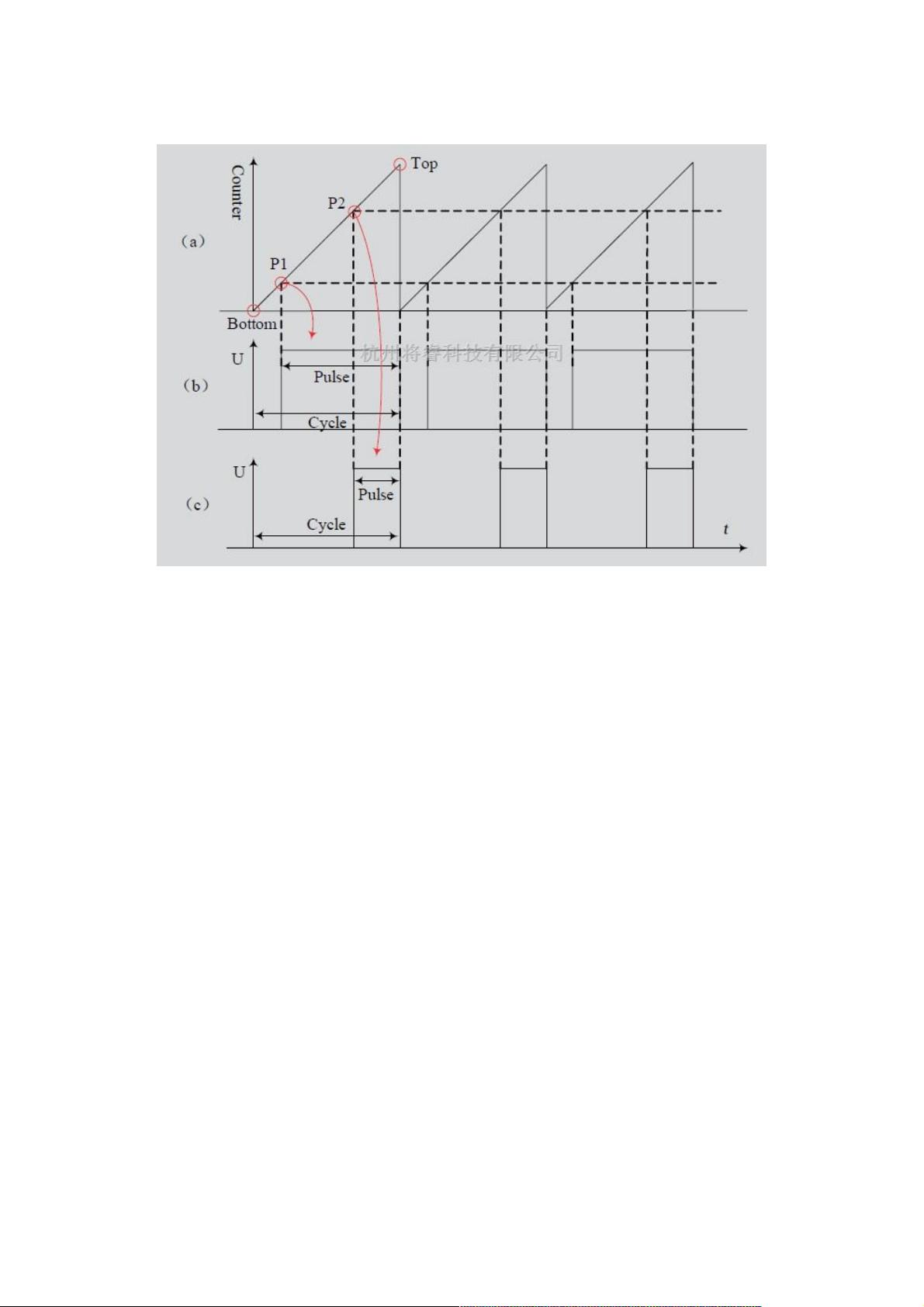

前面几期给读者介绍了单片机+CPLD 系统设计,本篇继续挖掘CPLD 潜力,给出一种单片机驱动CPLD的PWM 正弦信号发生器设计,充分体现了CPLD 的灵活多变,配合单片机控制,其妙无穷,以下方案均在Mini51 板上实现。 脉宽调制PWM(Pulse Width Modulation)是利用数字输出信号对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中。 一、PWM原理 PWM 是一种对模拟信号电平进行数字编码的方法。通过高分辨率计数器的使用,方波的占空比被调制用来对一个具体模拟信号的电平进行编码。PWM 信号仍然是数字的,因为在给 《电子测量中的单片机驱动CPLD的PWM正弦信号发生器设计》 本文将深入探讨一种基于单片机和复杂可编程逻辑器件(CPLD)的PWM正弦信号发生器的设计方法,该设计充分利用了CPLD的灵活性,并结合单片机的控制能力,实现了高效且精确的正弦波形生成。设计方案在Mini51开发板上得以实现,充分展示了这种技术在电子测量领域的应用潜力。 一、PWM原理与应用 PWM(Pulse Width Modulation)是一种利用数字信号控制模拟电路的技术,广泛应用于电子测量、通信和功率控制等多个领域。其基本思想是通过调整方波的占空比,即高电平时间与整个周期的比例,来编码模拟信号的电平。PWM信号本质上是数字的,因为信号在任何时候都处于全幅值的直流电源的“开”或“关”状态。通过快速开关电源的通断,可以模拟出任意连续的电压或电流波形,只要系统的带宽允许,几乎可以表示任何模拟值。 二、基于CPLD的PWM方案 一个完整的PWM发生器通常包含计数器、数据比较器以及用于配置PWM参数的时钟分频寄存器和占空比寄存器。CPLD因其可编程性,非常适合构建这类电路。计数器在一个高频时钟信号的驱动下工作,其输出与占空比寄存器的数据进行比较,从而生成PWM信号。当计数器的输出小于占空比设定值时,输出低电平,否则输出高电平,以此改变输出PWM信号的高电平与低电平的比例,从而实现模拟信号的数字编码。 图2所示的PWM控制器结构框图清晰地描绘了这一过程。计数器的周期等于PWM信号的周期,通过改变占空比寄存器的值,可以控制输出PWM信号的高低电平比例。例如,图3展示了两个不同占空比的PWM输出,尽管周期相同,但高低电平的比例不同。 三、Verilog HDL实现 在硬件描述语言(如Verilog HDL)中,可以编写CPLD的内部电路设计代码。以Mini51b_PWM模块为例,该模块接受来自单片机的数据输入、控制信号,并产生PWM输出。通过定义寄存器和计数器,以及使用条件语句根据地址选择要写入的数据,可以实现对PWM参数的灵活配置。 本文介绍的单片机驱动CPLD的PWM正弦信号发生器设计,不仅揭示了PWM技术的基本原理,还展示了如何利用CPLD的可编程性构建高效信号发生器。这种方法对于电子测量和控制系统的设计提供了新的思路,尤其是在需要精确模拟信号控制的场景中,具有显著的优势。

剩余7页未读,继续阅读

- 粉丝: 6

- 资源: 964

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功