没有合适的资源?快使用搜索试试~ 我知道了~

3D IC-TSV技术与可靠性研究

24 下载量 83 浏览量

2020-10-17

05:01:05

上传

评论 1

收藏 593KB PDF 举报

温馨提示

试读

8页

对三维(3 Dimension,3D)堆叠集成电路的硅通孔(Through Silicon Via,TSV)互连技术进行了详细的介绍,阐述了TSV的关键技术与工艺,比如对准、键合、晶圆减薄、通孔刻蚀、铜大马士革工艺等。着重对TSV可靠性分析的重要性、研究现状和热应力分析方面进行了介绍。以传热分析为例,实现简单TSV模型的热仿真分析和理论计算。最后介绍了TSV技术市场化动态和未来展望。

资源推荐

资源详情

资源评论

3D IC-TSV技术与可靠性研究技术与可靠性研究

对三维(3 Dimension,3D)堆叠集成电路的硅通孔(Through Silicon Via,TSV)互连技术进行了详细的介绍,

阐述了TSV的关键技术与工艺,比如对准、键合、晶圆减薄、通孔刻蚀、铜大马士革工艺等。着重对TSV可靠性

分析的重要性、研究现状和热应力分析方面进行了介绍。以传热分析为例,实现简单TSV模型的热仿真分析和

理论计算。最后介绍了TSV技术市场化动态和未来展望。

0 引言引言

随着半导体制作工艺尺寸缩小到深亚微米量级,摩尔定律受到越来越多的挑战。首先,互连线(尤其是全局互连线)延迟已经

远超过门延迟,,这标志着半导体产业已经从“晶体管时代”进入到“互连线时代”。为此,国际半导体技术路线图组织(ITRS)在

2005 年的技术路线图中提出了“后摩尔定律”的概念。“后摩尔定律”将发展转向综合创新,而不是耗费巨资追求技术节点的推

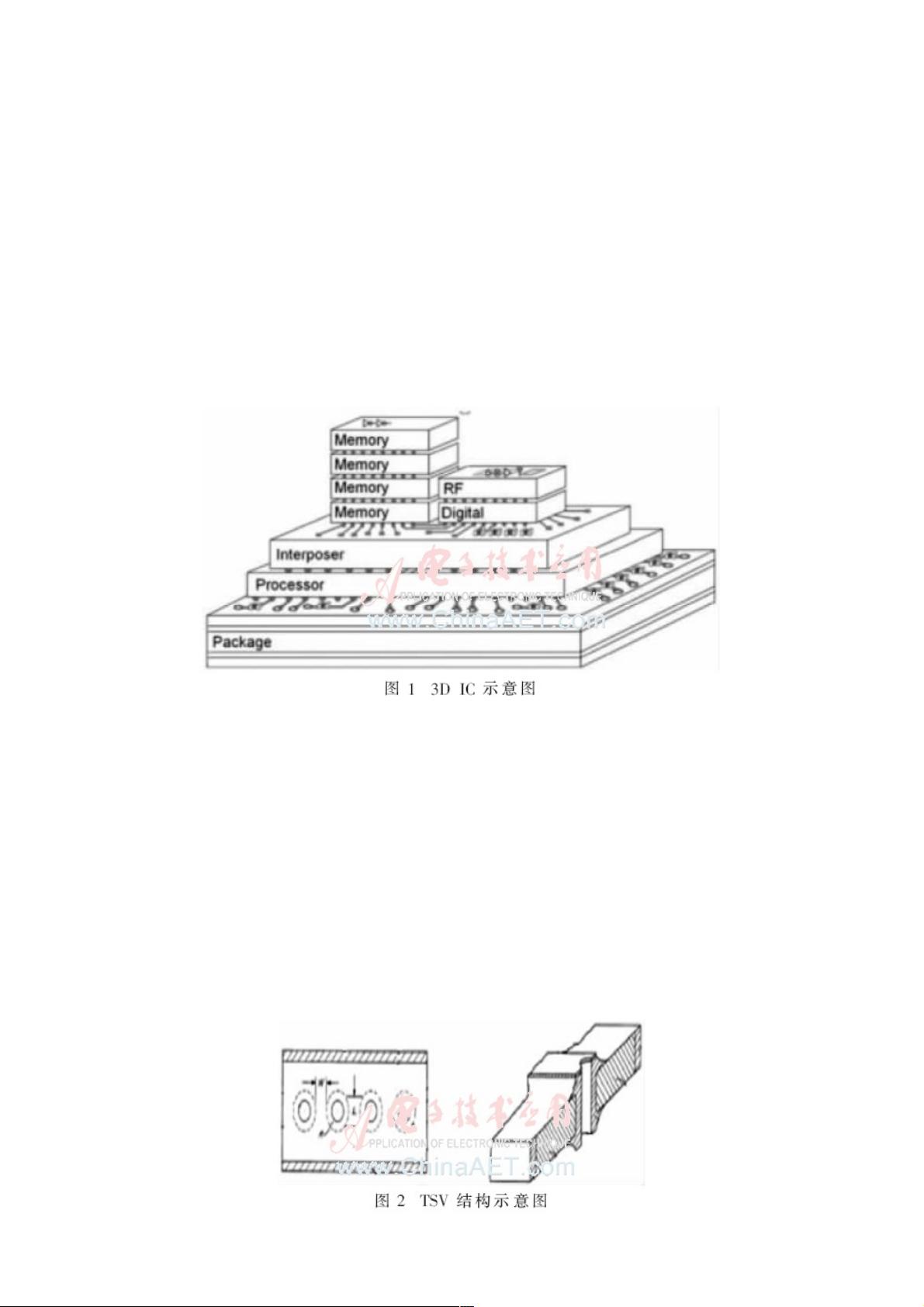

进。尤其是基于TSV(Through Silicon Via)互连的三维集成技术,引发了集成电路发展的根本性改变。三维集成电路(Three-

Dimensional Integrated Circuit,3D IC)可以将微机电系统(MEMS)、射频模块(RF module)、内存(Memory)及处理器

(Processor)等模块集成在一个系统内

[1]

,如图1所示,大大提高了系统的集成度,减小了功耗,提高了性能,因此被业界公认

为延续摩尔定律最有效的途径之一,成为近年来研究的热点。

目前3D集成技术主要有如下三种:焊线连接(Wire-Bonding)、单片集成(Monolithic Integration)和TSV技术

[2]

。焊线连接是一

种直接而经济的集成技术,但仅限于不需要太多层间互连的低功率、低频的集成电路。单片集成是在同一个衬底上制作多层器

件的新技术,它的应用受到工艺温度要求很高和晶体管质量较差等约束。基于TSV的3D集成可以实现短且密的层间互连,有

效缩短了互连线长度,大大提高了系统集成度,降低了互连延时,提高了系统性能,缩小了封装尺寸,高频特性出色,芯片功

耗降低(可将硅锗芯片的功耗降低大约40%),热膨胀可靠性高,同时还实现了异构集成,成为业界公认使摩尔定律持续有效的

有力保证,所以备受研究者的青睐。

1 TSV技术与相关工艺技术与相关工艺

1.1 TSV技术介绍技术介绍

TSV技术将在先进的三维集成电路(3D IC)设计中提供多层芯片之间的互连功能

[3]

。图2给出了最早的TSV结构示意图,这是

1958年诺贝尔奖得主WilliamShockley提出的

[4]

。它是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,一般用导体材

料钨、铝、铜、多晶硅或碳纳米管构成的互连线垂直穿过硅衬底以实现上下层芯片的信号互连

[5]

,需要穿透组成叠层电路的各

种材料以及很厚的硅衬底。TSV作为目前芯片互连的最新技术,使芯片在三维方向堆叠密度最大、芯片间的互连线最短、外形

尺寸最小,大大改善芯片速度,产生低功耗性能。

使用硅基板和TSV的三维堆叠的结构如图3所示。在 3D 芯片堆叠结构中,为了充分利用三维集成电路的优势

[6]

,硅

[7]

。与

资源评论

weixin_38681646

- 粉丝: 6

- 资源: 882

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功