Data Sheet, V1.0, February 2010

SmartLEWIS

TM

RX+

TDA5235

Enhanced Sensitivity

Double-Configuration Receiver with

Digital Baseband Processing

Wireless Control

Never stop thinking.

Edition February 19, 2010

Published by Infineon Technologies AG,

Am Campeon 1 - 12

85579 Neubiberg, Germany

© Infineon Technologies AG February 19, 2010.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or the Infineon Technologies Companies and our Infineon Technologies

Representatives worldwide (www.infineon.com).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

Data Sheet, V1.0, February 2010

SmartLEWIS

TM

RX+

TDA5235

Enhanced Sensitivity

Double-Configuration Receiver with

Digital Baseband Processing

Wireless Control

Never stop thinking.

TDA5235

Revision Number: 010

Revision History: 2010-02-19 V1.0

Previous Version: TDA5235_V0.1

Page Subjects (major changes since last revision)

Page 25 Update of Figure 9

Page 27 Update of Figure 10

Page 29 AFC limitation added

Page 31 AGC setting proposal added

Page 32 New Section 2.4.6.5 ADC added

Page 34 Additional information on RSSIPRX register inserted

Page 39 Signal and Noise Detector Procedure adapted

Page 43 x_CDRRI register recommendation changed

Page 47, 50, 54 Data Slicer Modes adapted; limitation added

Page 67 Update of Figure 41

Page 68 Update of Figure 42

Page 76 Additional hint on clock and data recovery algorithm of the user

software inserted

Page 82 PLDLEN limitation added

Page 84 Limitation for ISx readout and Burst-read function added

Page 86 Limitation for Burst-read function added

Page 105 Description of “Parallel Wake-up Search” adapted

Page 123 Additional hints added

Page 125 Adaption of Section 4.1

Page 128 New item C7 added

Page 136 f Comments added for items I6, I7, I8, I9, J11, J12

Page 136 Item J1 updated

Page 139 ff General test conditions noted for parameters K, L and M

Page 145 BOM components C7, C8, L1, R2 and R3 updated

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

Wirelesscontrol@infineon.com

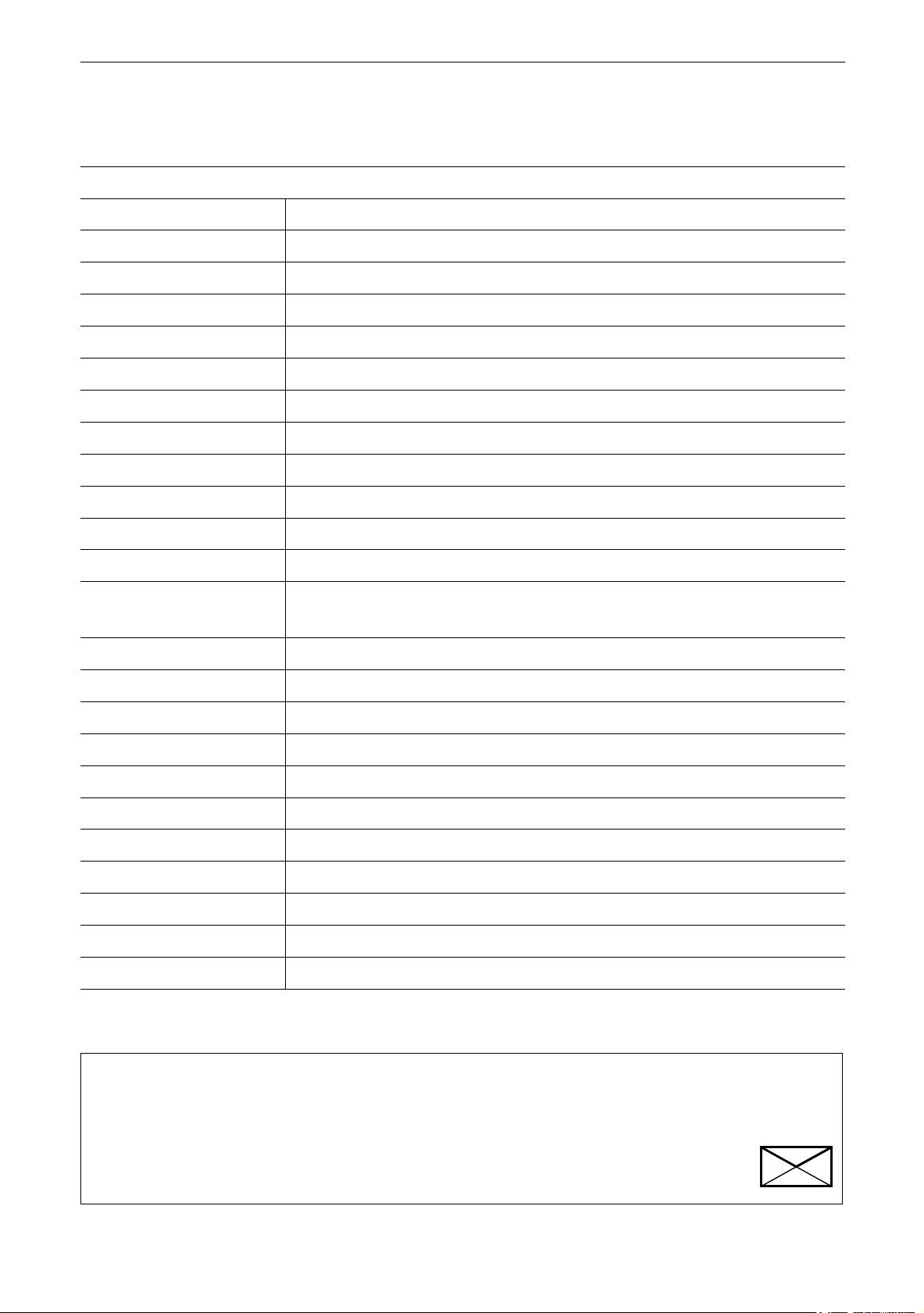

TDA5235

Table of Contents Page

Data Sheet 5 V1.0, 2010-02-19

1 Product Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.1 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.2 Pin Definition and Pin Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.4 Functional Block Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.4.1 Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.4.2 Block Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.4.3 RF/IF Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.4.4 Crystal Oscillator and Clock Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.4.5 Sigma-Delta Fractional-N PLL Block . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.4.5.1 PLL Dividers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.4.5.2 Digital Modulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.4.6 ASK and FSK Demodulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.4.6.1 ASK Demodulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.4.6.2 FSK Demodulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.4.6.3 Automatic Frequency Control Unit (AFC) . . . . . . . . . . . . . . . . . . . . . 28

2.4.6.4 Digital Automatic Gain Control Unit (AGC) . . . . . . . . . . . . . . . . . . . . 30

2.4.6.5 Analog to Digital Converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2.4.7 RSSI Peak Detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.4.8 Digital Baseband (DBB) Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.4.8.1 Data Filter and Signal Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.4.8.2 Encoding Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.4.8.3 Clock and Data Recovery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.4.8.4 Data Slicer and Line Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.4.8.5 Wake-Up Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.4.8.6 Frame Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

2.4.8.7 Message ID Scanning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.4.8.8 RUNIN, Synchronization Search Time and Inter-Frame Time . . . . . . 66

2.4.9 Power Supply Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

2.4.9.1 Supply Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

2.4.9.2 Chip Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

2.5 System Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

2.5.1 Interfacing to the TDA5235 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

2.5.1.1 Control Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

2.5.1.2 Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

2.5.2 Receive FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

2.5.3 Digital Output Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.5.4 Interrupt Generation Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86