没有合适的资源?快使用搜索试试~ 我知道了~

QDR SRAM与Spartan3 FPGA的接口设计

5 下载量 62 浏览量

2020-10-22

12:45:51

上传

评论

收藏 127KB PDF 举报

温馨提示

试读

3页

为了满足当前系统和处理器的生产量需求,更新的静态存储器应运而生。QDR SRAM就是由Cypress、Renesas、IDT、NEC和Samsung为高性能的网络系统应用而共同开发的一种具有创新体系结构的同步静态存储器。

资源推荐

资源详情

资源评论

QDR SRAM与与Spartan3 FPGA的接口设计的接口设计

为了满足当前系统和处理器的生产量需求,更新的静态存储器应运而生。QDR SRAM就是由Cypress、

Renesas、IDT、NEC和Samsung为高性能的网络系统应用而共同开发的一种具有创新体系结构的同步静态存储

器。

为了满足当前系统和处理器的生产量需求,更新的静态存储器应运而生。QDR SRAM就是由Cypress、Renesas、IDT、

NEC和Samsung为高性能的网络系统应用而共同开发的一种具有创新体系结构的同步静态存储器。

1 QDR SRAM的介绍及其性能描述

1.1 QDR的先进性

现有的大部分SRAM都是在PC时期针对高效传输PC型单精度输入输出数据而设计的。在大多数的网络应用中,SRAM和

记忆控制器之间的连续数据传输是必需的。在这些应用中,存储器的读和写操作之间要进行连续不断的变化。在这种情况下标

准的同步管道SRAM等单一的输入/输出装置就不能很好地满足要求。零总线变换SRAM就是一种优化了的SRAM类型。它在读

周期与写周期切换时不需要变换周期,从而使得总线利用率达到了100%。而对大多数的网络应用来说,零总线变换SRAM在

数据吞吐量方面的提高还远远不够。QDR的出现则进一步改进了SRAM结构。

QDR就是指四倍数据速率SRAM,它是静态存储器的一种,是专为应付带宽需求极大的应用而设计的体系结构。它在一

个

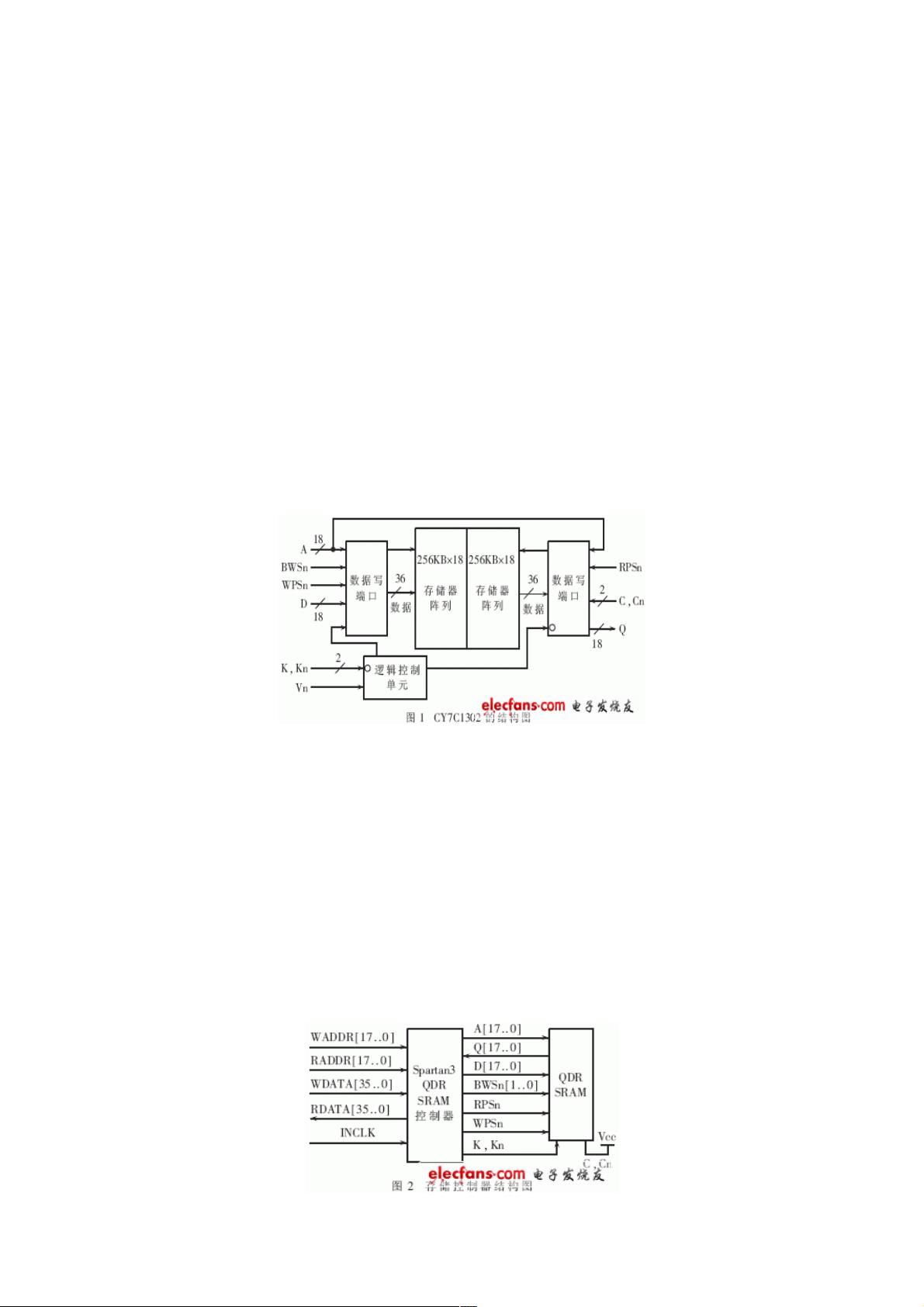

QDR又分为两字突发结构(CY7C1302)和四字突发结构(CY7C1304)两种。这两种结构的不同就在于每次读或写请求的传

输字数不同。下面就以CY7C1302为例来详细介绍QDR的工作原理及其与Spartan3系列FPGA的接口设计。CY7C1302是赛普

拉斯公司生产的一种QDR SRAM。图1示出了CY7C1302的结构图。图中虽然CY7C1302有了分别独立的读写端口,但是

1.2 QDR SRAM的输入状态描述

QDR SRAM有四个时钟:K,Kn,C和Cn。K和Kn是用来控制输入数据采样的,C和Cn则是用来控制SRAM数据输出

的。所有的数据操作都是在K的上升沿进行的。QDR SRAM有一个简单的控制结构。两个

一个时钟的上升沿可以使QDR SRAM在同一个时钟周期内实现对同一地址的读、写访问。这样QDR就会把写数据传输到

读端口以确保把有效的数据输出至数据总线。这样就保证了数据的一致性。

2 低成本解决方案

2.1 用Spartan3作为QDR的存储控制器

Spartan3系列FPGA是由Xilinx公司基于成功的Virtex-II FPGA架构而研发的性价比较高的一种产品。Spartan3器件有如下

特点:嵌入式18×18乘法器支持高性能DSP应用;片上数字时钟管理(DCM),无需外部时钟管理器件;分布式的存储器和SRL16

移位寄存器逻辑能够更高效执行DSP功能;18KB 块RAM,可以用作缓存或是高速缓存;数字片上终端能够消除对多个外部电阻

器的需求;8个独立的

该存储控制器的设计可以在深度扩展模式下实现对四个SRAM的控制。每个QDR SRAM会收到对各自的读写端口进行控

制的相互独立的控制信号,而对所有的SRAM来说,地址和数据端口是共用的。

资源评论

weixin_38665490

- 粉丝: 4

- 资源: 985

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功