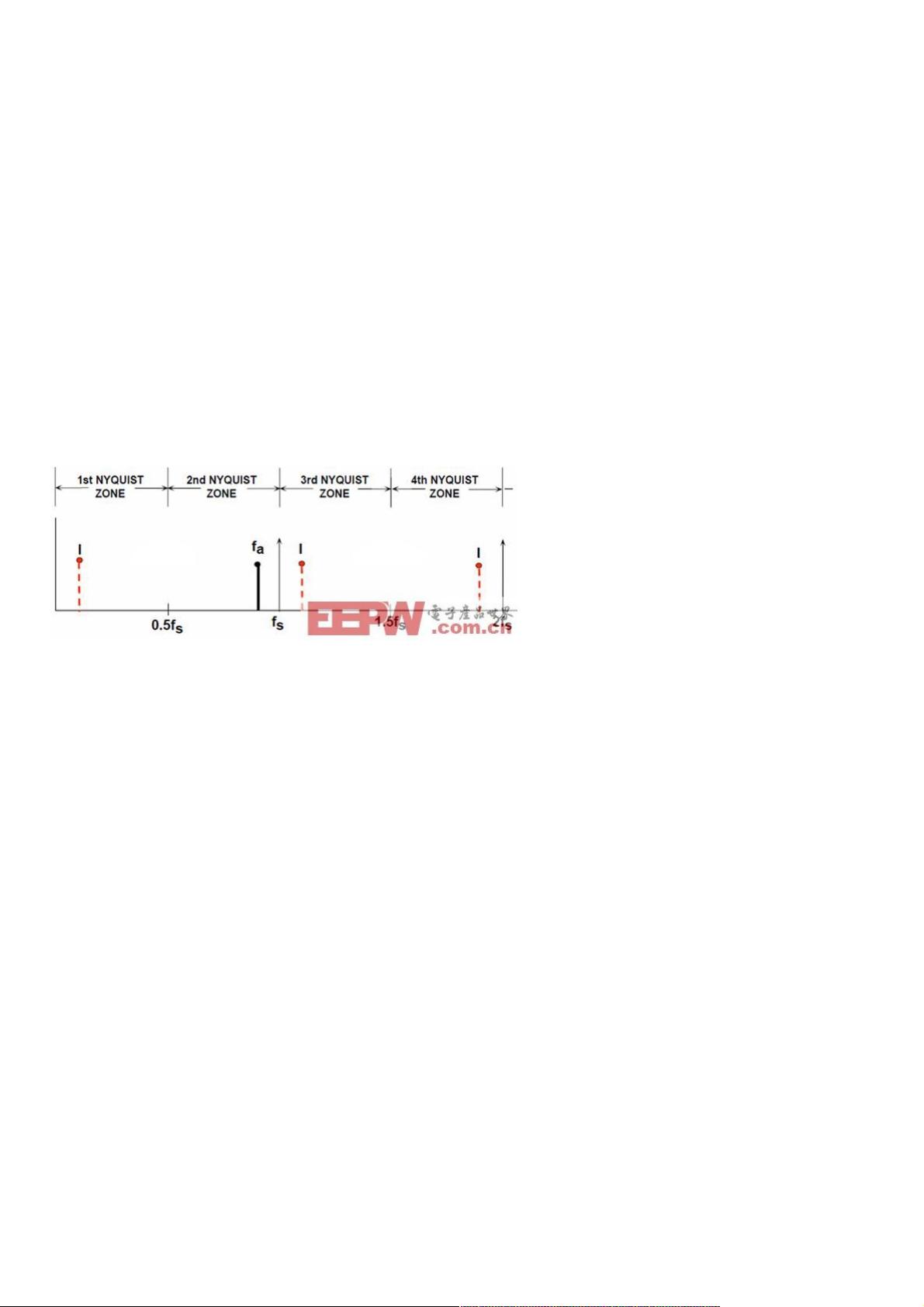

许多数字处理系统都会使用FPGA,原因是FPGA有大量的专用DSP以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA都要和高性能的ADC和DAC进行接口,比如e2v EV10AQ190低功耗四通道10-bit 1.25 GspsADC和EV12DS130A内建4/2:1 MUX的低功耗12-bit 3 Gsps DAC。 在现代数字信号处理系统中,FPGA(Field-Programmable Gate Array)因其丰富的数字信号处理单元(DSP slices)和Block RAM资源而被广泛应用。FPGA能够实现并行计算和流水线架构,使得处理速度得到大幅提升。而在这些系统中,高速ADC(Analog-to-Digital Converter)和DAC(Digital-to-Analog Converter)是不可或缺的关键组件,它们负责在模拟世界与数字世界之间建立桥梁。 以e2v的EV10AQ190为例,这是一个低功耗的四通道10-bit 1.25 GSps ADC,它提供了高效率的数据转换能力。另一个例子是EV12DS130A,一个内置4/2:1 MUX的低功耗12-bit 3 GSps DAC,它具有灵活的数字接口,适用于各种应用场景。这些高速转换器的高采样率使得系统能够处理GHz级别的信号。 奈奎斯特采样理论是理解ADC和DAC工作原理的基础。根据奈奎斯特准则,采样率必须至少是信号最高频率的两倍,以避免混叠现象。然而,在实际应用中,往往需要在接近或超过奈奎斯特区的情况下操作,这就需要通过预滤波器等手段来防止信号失真。例如,一个2.5 GHz采样率的ADC在接收3 GHz带宽信号时,高于1.25 GHz的频率成分会被混叠到较低频率,形成图像信号,需要通过合适的滤波策略进行处理。 对于DAC,情况则有所不同。在上奈奎斯特区,需要确保所需谐波的正确输出,而且在高频下,可能需要通过SINC补偿来抵消信号衰减。前端设计,包括输入组件、阻抗匹配和预滤波器的选择,对保证ADC和DAC性能至关重要。 在FPGA与高速ADC和DAC的接口设计中,通常会使用多路复用器以降低数据速率,例如e2v转换器的FS/4或FS/2配置,将数据分布在多个并行总线上。这些并行LVDS(Low Voltage Differential Signaling)接口可以提供低延迟和低辐射噪声,但同时也会占用大量FPGA的I/O资源。 在FPGA内部,处理这些高速数据流的方法多种多样,其中一种常见的做法是利用FFT(快速傅里叶变换)进行频谱分析。组合FFT结构,如使用4个128点的FFT流水线和1个4点FFT,可以构建出512点的FFT;而分离FFT则先进行数据重组,然后再进行处理。为了优化频谱泄漏,许多应用会在FFT之前采用加权叠接相加(WOLA)方法,如图所示,WOLA可以显著减少相邻信道间的干扰。 根据具体应用需求,对FFT结果进行后处理,可能是滤波、解码或其他信号处理算法。在处理大型FFT时,设计高效的算法是一项挑战,但也是确保整个系统性能的关键。 高速ADC和DAC与FPGA的配合使用是现代数字信号处理系统中的核心技术,涉及到了采样理论、预处理滤波、FPGA接口设计、FFT处理以及后处理等多个复杂环节,需要综合考虑系统性能、功耗和成本等因素,以实现最优的设计方案。

- 粉丝: 6

- 资源: 960

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功