没有合适的资源?快使用搜索试试~ 我知道了~

伴随着现代大规模集成电路制造工艺的快速发展,设计工程师必需直面芯片制造过程中可能产生的物理缺陷。现今流行的可测试性设计(DFT:DesignForTestability)应运而生,并为保证芯片的良品率担任着越来越重要的角色。 在DFT设计中,测试覆盖率及其测试效率是最重要的指标。一方面,理想的设计目标当然希望测试能够遍及整个芯片的逻辑,尽管理想值100%是不容易达到的;另一方面,测试效率亦非常重要,设计工程师总希望用最少的测试向量达到预期的测试覆盖率,来降低芯片的测试成本。 当然,DFT设计必须保证正常的逻辑功能为前提。不幸的是,功能设计总会忽略一些潜在的问题,导致最终的测试覆盖率往往

资源详情

资源评论

资源推荐

提高提高DFT设计测试覆盖率的一种有效方法设计测试覆盖率的一种有效方法

伴随着现代大规模集成电路制造工艺的快速发展,设计工程师必需直面芯片制造过程中可能产生的物理缺陷。现今流行的可测

试性设计(DFT:Design For Testability)应运而生,并为保证芯片的

伴随着现代大规模集成电路制造工艺的快速发展,设计工程师必需直面芯片制造过程中可能产生的物理缺陷。现今流行的

可测试性设计(DFT:Design For Testability)应运而生,并为保证芯片的良品率担任着越来越重要的角色。

在DFT设计中,测试覆盖率及其测试效率是最重要的指标。一方面,理想的设计目标当然希望测试能够遍及整个芯片的逻

辑,尽管理想值100%是不容易达到的;另一方面,测试效率亦非常重要,设计工程师总希望用最少的测试向量达到预期的测试

覆盖率,来降低芯片的测试成本。

当然,DFT设计必须保证正常的逻辑功能为前提。不幸的是,功能设计总会忽略一些潜在的问题,导致最终的测试覆盖率

往往不尽如人意。这种情况下,设计中有一些逻辑无论如何都不能被观测到或控制到,因此即使测试矢量的数量有很大的增

幅,也不能使结果改善很多。

在实际的DFT设计中,存在对测试覆盖率有较大损害的两种情况:一种存在于数字逻辑-模拟逻辑(包括存储器)输入-输出

处之阴影部分,另一种存在于特定的多芯片封装情况下未绑出的输入-输出焊垫处。二者的共同点在于:测试模式下部分逻辑

的不可控或不可观测。

设计背景

本文探讨的设计目标是一个来自意法半导体的数字音频信号处理芯片,要求对数字功能逻辑进行扫描链测试,覆盖率达到

98%以上。其功能逻辑中存在一些模拟模块,如锁相环、模数转换器和一些存储器单元等。更为重要的是,该芯片需要基于不

同的应用系统需要,不但需要单独封装形式,也需要多芯片共享同一封装。这样,在某些多芯片封装中,就有部分焊垫未引出

或接地。而测试的设计初衷是产生一组测试向量适用于所有封装形,就要求考虑最严格的封装下可用的管脚资源。

DFT设计有两个基本原则:可控制性和可观测性,即DFT设计要求所有输入逻辑是可控的和输出逻辑是可测的。显然,考

虑到本设计中的模拟模块接口和封装形式的资源有限性,不可控逻辑和不可观测逻辑对不小于98%的目标测试覆盖率给出了很

大的挑战。

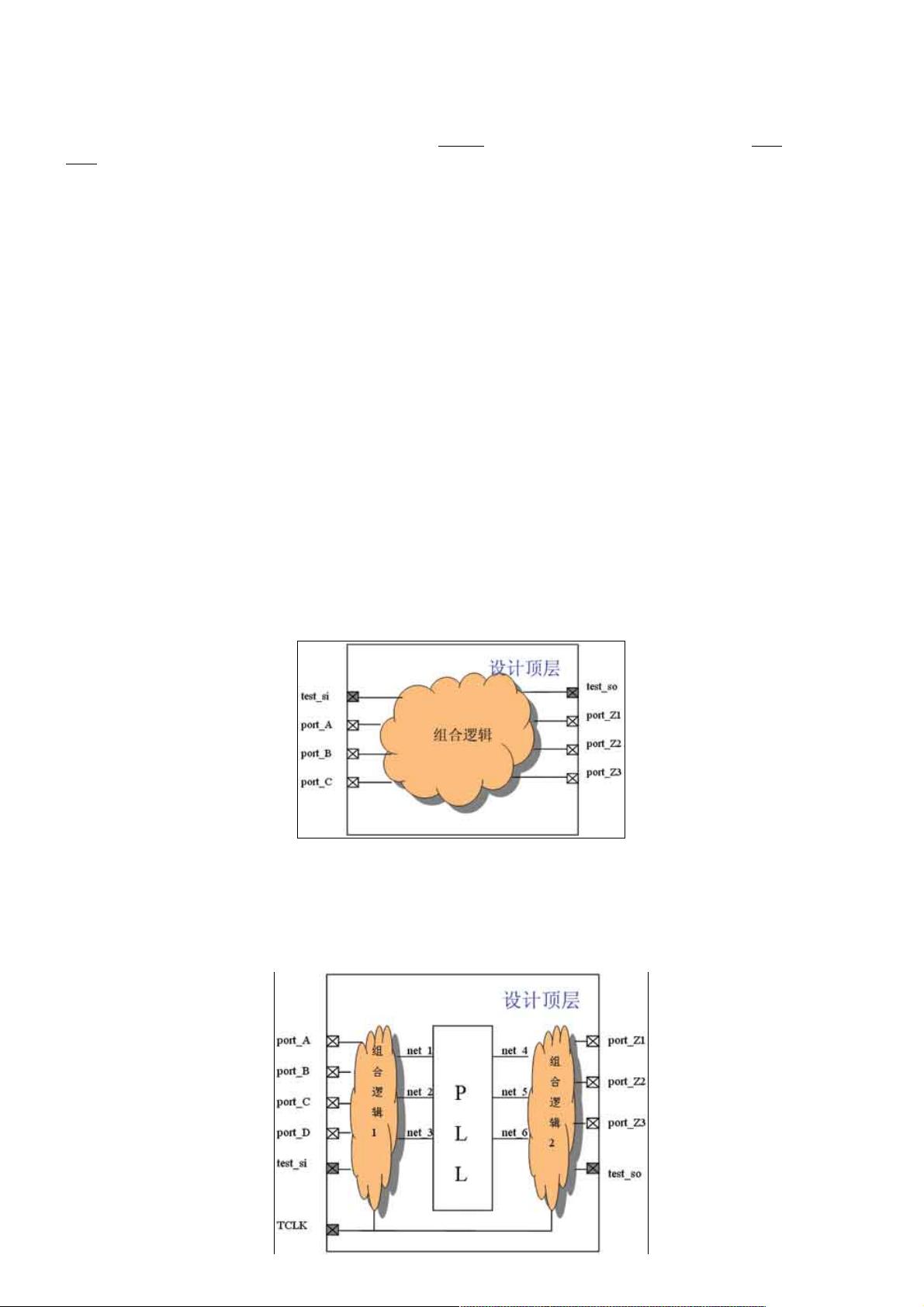

如图1所示,在某种芯片封装情况下,除信号test_si和test_so外,其余焊垫并未绑出(接地或悬空),从而造成信号

port_A、port_B、port_C和port_D的不可控,以及信号port_Z1、port_Z2和 port_Z3的不可观测(悬空)。导致很多相关逻辑不

能正常参于DFT测试,测试覆盖率受到较大的损害。

图1 封装造成的测试逻辑不可控和不可测

DFT设计的可控制性和可观测性是通过原始的管脚来实现的,事实上功能设计不可能专门为DFT保留足够多的管脚。如图

2所示的数字-模拟接口,由于PLL模块的存在,显然信号net_1、net_2和net_3上得到的测试结果不可直接观测(不可测),组合

逻辑1相应的测试覆盖率降低了;同时,由于PLL模块的存在,信号net_4、net_5和的net_6不能直接赋值(不可控),导致组合逻

辑 2的部分逻辑不能正常参于DFT测试,相应的测试覆盖率受到较大的损害。总的来说,芯片的测试覆盖率降低了。

weixin_38589316

- 粉丝: 6

- 资源: 900

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0