- 25 -

基于 FPGA 的 DDS 直接数字频率合成器设计与实现

赵翰林

(电子科技大学,四川 成都 610054)

【摘 要】直接数字频率合成器具有变频范围广、频率步进小、幅度和频率精度高、调谐方便等优点。对其进行了理论分

析,并采用 FPGA 技术实现了这样一个系统,该系统允许频率调谐、相位调谐,可以产生正弦、余弦信号,具有设计简单可靠、

调谐方便等优点。

【关键词】直接频率合成;可调谐;小步进;FPGA

【中图分类号】TN74 【文献标识码】A 【文章编号】1008-1151(2010)06-0025-03

(一)直接数字频率合成技术介绍

直接数字频率合成器(Direct Digital Synthesizer)

是从相位的概念出发直接合成所需波形的一种频率合成技

术。一个直接数字频率合成器由相位累加器、加法器、波形

存储 ROM、D/A 转换器和低通滤波器(LPF)构成。DDS 的原理

框图如图 1 所示:

图 1 DDS 的原理框图

其中 K 为频率控制字、P 为相位控制字、f

c

为参考时钟频

率,N 为相位累加器的字长,D 为 ROM 数据位及 D/A 转换器的

字长。相位累加器在时钟 f

c

的控制下以步长 K 作累加,输出

的 N 位二进制码与相位控制字 P 相加后作为波形 ROM 的地址,

对波形 ROM 进行寻址,波形 ROM 输出 D 位的幅度码 S(n)进

D/A 转换器变成阶梯波 S(t),再经过低通滤波器平滑后就可

以得到合成的信号波形。合成的信号波形形状取决于波形 ROM

中存放的幅度码,因此用 DDS 可以产生任意波形。这里我们

将用 DDS 实现正弦波的合成,并通过 FPGA 芯片实现其硬件电

路。

笔者主要进行 DDS 软件方面的设计,所以以下原理与仿

真以软件方面为主。

1.频率预置与调节电路

K 被称为频率控制字,也加相位增量。DDS 方程为:f

0

=f

c

×K/2

N

,f

0

为输出频率,f

c

为时钟频率。当 K=1 时,DDS 输出

最低频率(也即频率分辨率)为 f

c

/2

N

,而 DDS 的最大输出频

率由 Nyquist 采样定理决定,即 f

c

/2,也就是说 K 的最大值

为2

N-1

。因此,只要 N 足够大,DDS 可以得到很细的频率间隔。

实际中 DDS 的最高输出频率由允许输出的杂散水平决定,一般

取值为 f

0

≤40% f

c

。要改变 DDS 的输出频率,只要改变频率

控制字K即可。

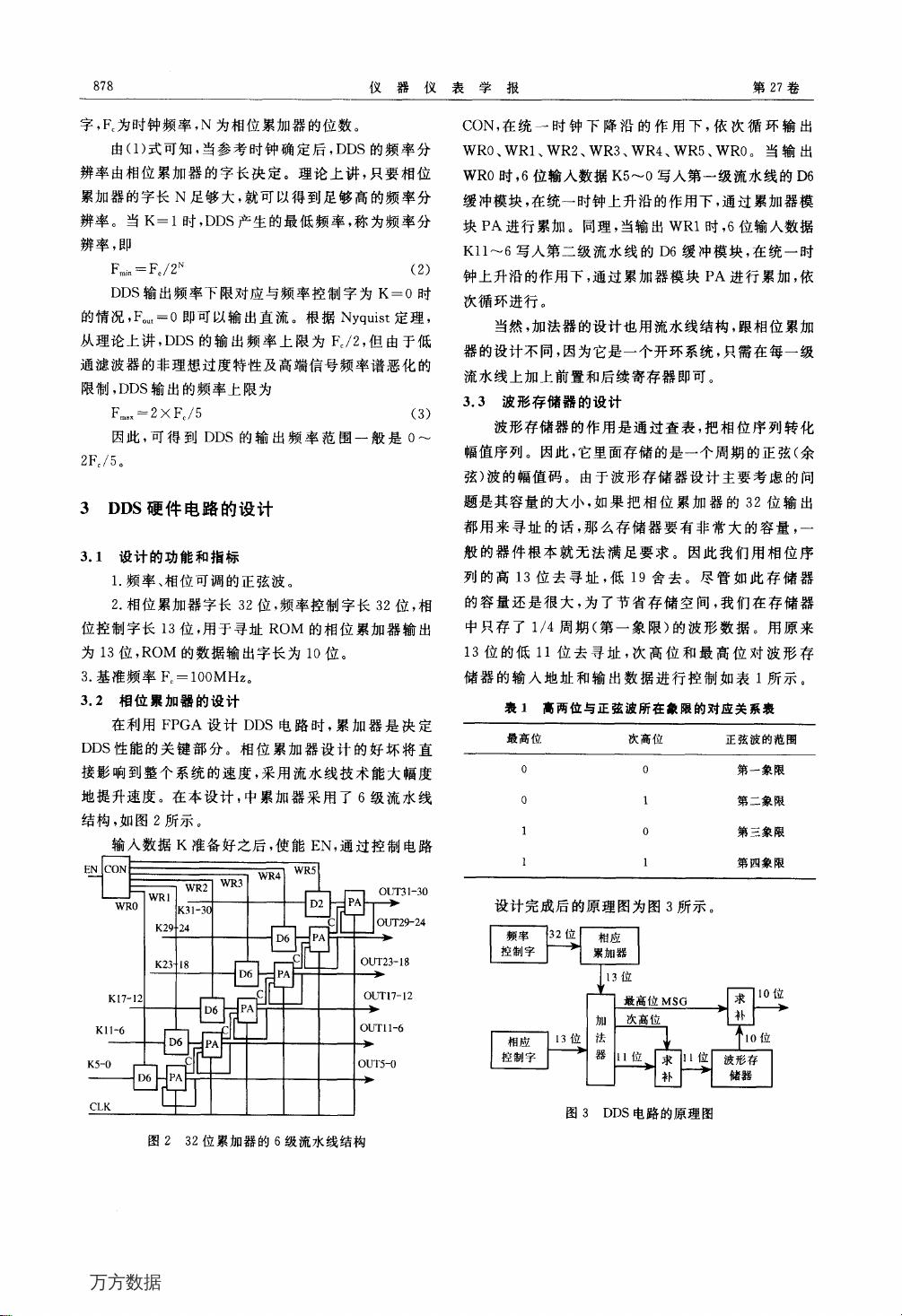

2.累加器(图 2)

图 2 累加器框图

相位累加器由 N 位加法器与寄存器级联构成。每来一个

时钟脉冲 f

c

,加法器将频率控制字 K 与寄存器输出累加相位

数据相加,再把相加后的结果送到寄存器的数据输入端。寄

存器将加法器在上一个时钟的作用后所产生的相位数据反馈

到加法器的输入端,以使加法器在下一个时钟的作用下继续

与频率控制字进行相加。这样,相位累加器在时钟的作用下,

进行相位累加。当累加器累加满量时就会产生一次溢出,完

成一个周期性动作。

3.控制相位的加法器

通过改变相位控制字 P 可以控制输出信号的相位参数。

令相位加法器的字长为 N,当相位控制字由 0 跃变到 P(P≠0)

时,波形存储器的输入为相位累加器的输出与相位控制字 P

之和,因而其输出的幅度编码相位会增加 P/2

N

,从而使最后

输出的信号产生相移。

4.波形存储

用相位累加器输出的数据作为波形存储器的取样地址,

进行波形的相位—幅值转换,即可在给定的时间上确定输出

的波形的抽样幅值。N 位的寻址 ROM有D位数据,则 2N 个样

值的幅值以 D 位二进制数值固话在 ROM 中,按照地址的不同

可以输出相应的相位的正弦信号幅值。

相位—幅度变换原理图如图 3 所示:

图 3 相位—幅度变换原理图

5.D/A 转换器

D/A 转换器的作用是把合成的正弦波数字量转换成模拟

量。正弦幅度量化序列 S(n)经 D/A 转换后变成了包络为正

2010 年第 6 期 大 众 科 技 No.6,2010

(总第 130 期) DA ZHONG KE JI (Cumulatively No.130)

【收稿日期】2010-03-20

【作者简介】赵翰林,男,四川广安人,电子科技大学在读硕士生,研究方向为电路与系统。