多功能数字钟电路

设计报告

班级:11 通 一

学号:201155110 2

姓名:李 兰

时间:2013

年

10

月

1 7

日

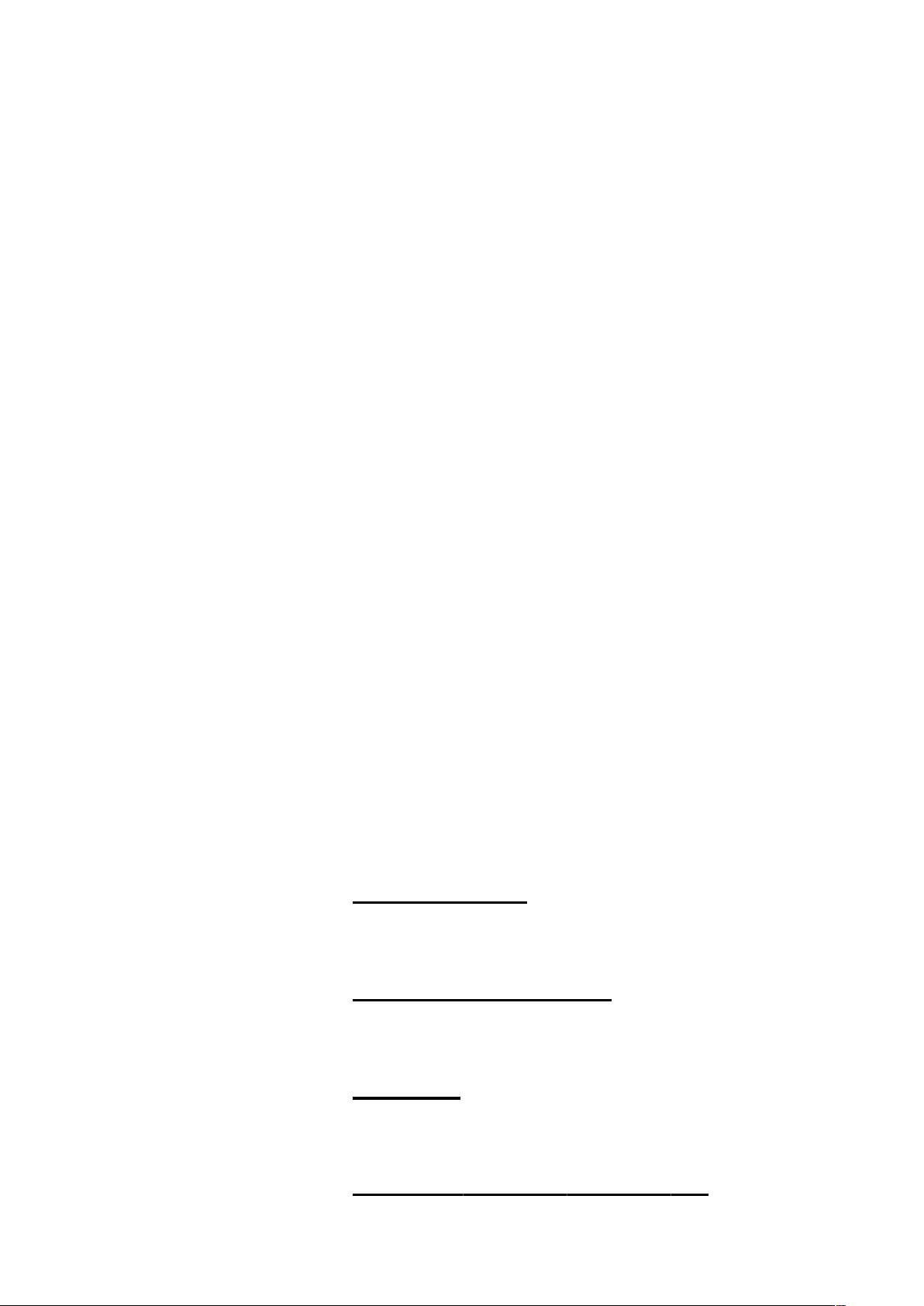

1 系统原理框图

图 1 系统原理图

2

时显示器 分显示器 秒显示器

时译码器 分译码器 秒译码器

时计数器 分计数器 秒计数器

校时电路

振荡器 分频器

定时控制

仿电台报时

整点报时

主体部分

扩展 部分

2 单元电路的设计

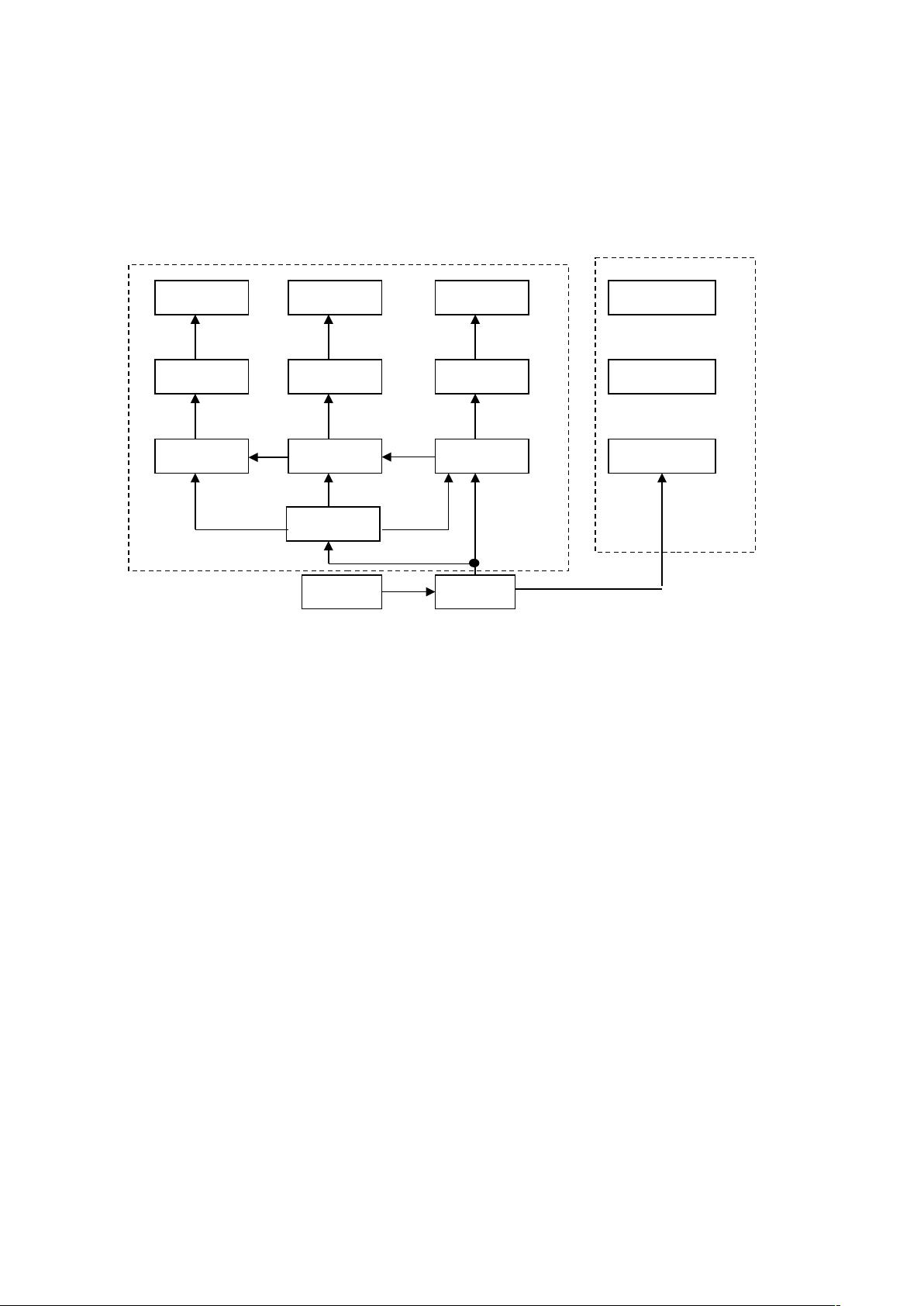

2.1 时间脉冲产生电路的设计

图 2 产生 1Hz

时间脉冲的电路

图

用 555 定时器接

成多谐振荡器

将设计图中

参数代入则

得到要求的

时基频率,

产生时间脉

冲。

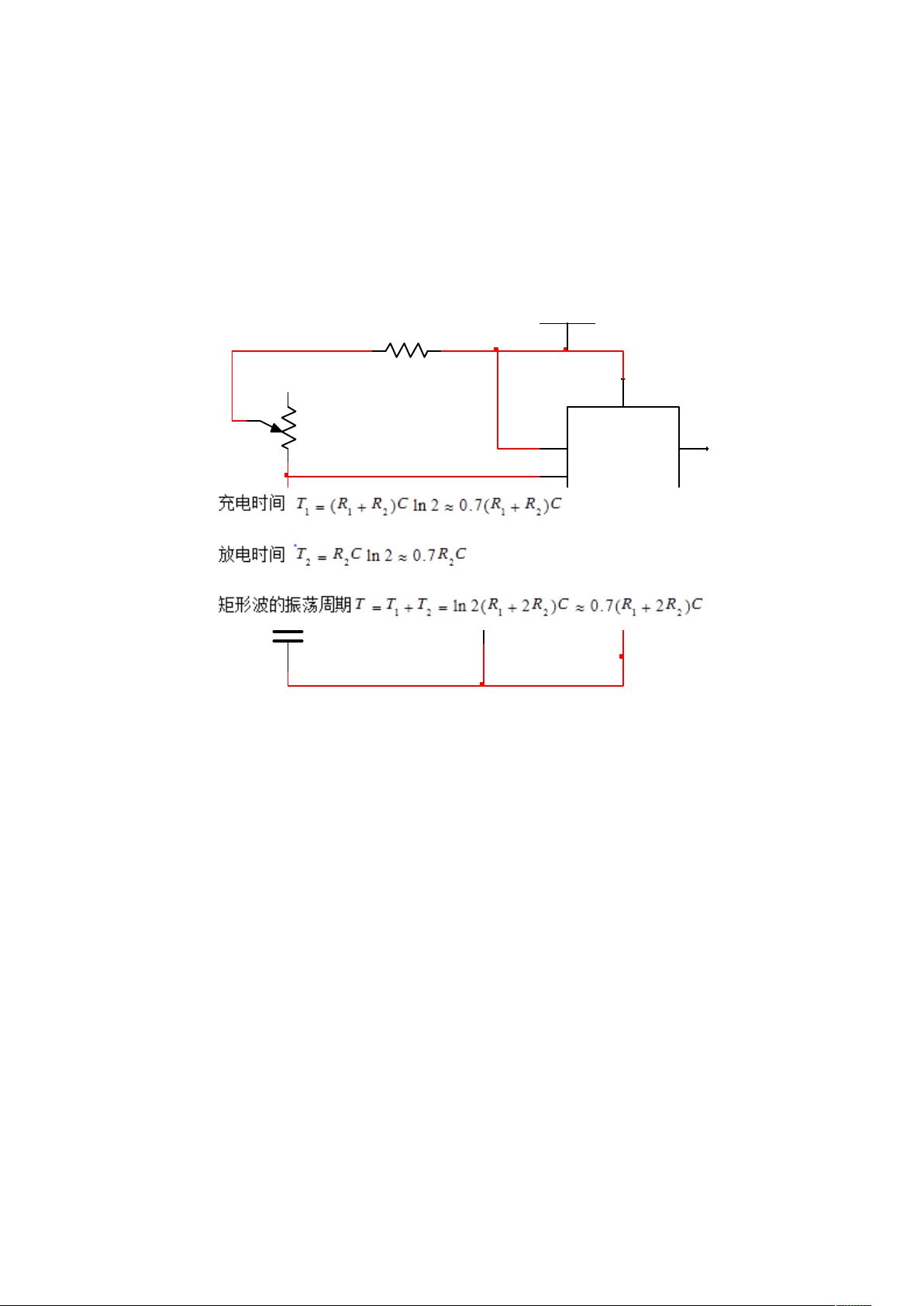

2.2 计数电路的设计

秒、分计数器为 60 进制计数器。12 小时计数器为 12 翻一计数器。

2.2.1 60 进制计数器的设计

“秒”计数器电路与“分”计数器电路都是 60 进制,它由一级 10 进制计数器和一级 6 进

制计数器连接构成。如图 3 所示由 74LS160 构成的 60 进 制 计 数 器 。 首 先 将 两 片

CC40161 设置成十进制加法计数器,将两片计数器并行进位则最大可实现 100 进制的

计数器。现要 60 进制的计数器,可利用“反馈清零”的方法实现。当计数器 输出为

“2QD2QC2QB2QA、1QDQCQBQA=0110、0000”即计数到 60 时,通过门电路产生

的低电平信号立即将两片 74160 同时置零,得到 60 进制。但是该门电路脉冲极短,数

码管中不出现“60”状态。

VCC

OUT

U4

555_TIMER_RATED

GND

DIS

RST

THR

CON

TRI

C1

10nF

C2

1uF

R1

4.8kΩ

R2

4.5kΩ

R3

500Ω

Key=A

50%

4

3

2

1

0

VCC

5V

VCC

3

图 3 60 进制计数器电路图

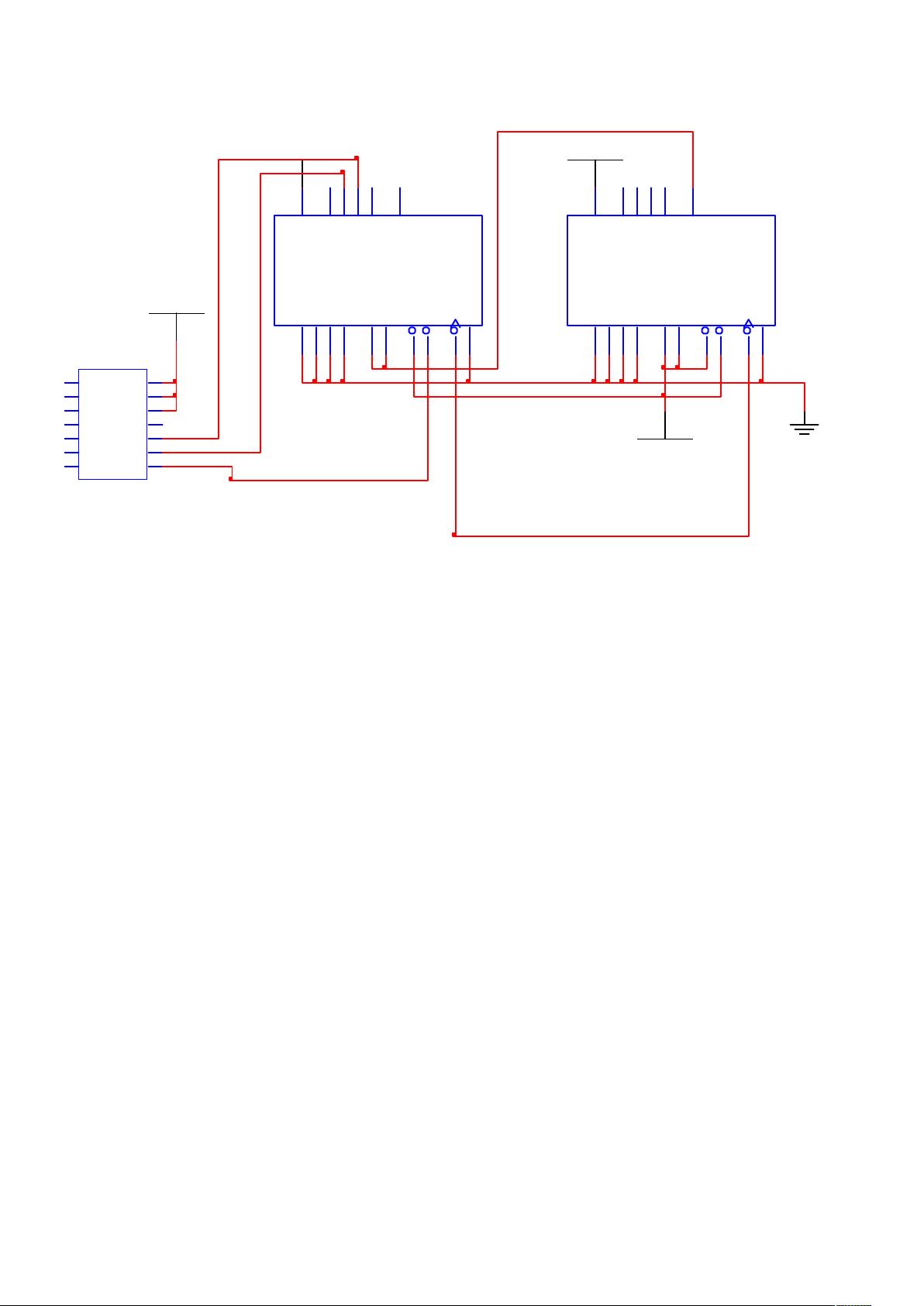

2.2.2 十二翻一计数器的设计

十二翻一计数器采用整体置数法,首先将两片 74160 接成百进制计数器。然后将电

路的 12 状态译码为 LD’=0 信号,同时加到两片 74160,在下一个计数脉冲到达时将

“01”状态态分别置入两片芯片,从而实现“12 翻 1”。

U7

74LS160D

QA

14

QB

13

QC

12

QD

11

RCO

15

A

3

B

4

C

5

D

6

ENP

7

ENT

10

~LOAD

9

~CLR

1

CLK

2

GND

8

VCC

16

U8

74LS160D

QA

14

QB

13

QC

12

QD

11

RCO

15

A

3

B

4

C

5

D

6

ENP

7

ENT

10

~LOAD

9

~CLR

1

CLK

2

GND

8

VCC

16

U9

74LS20D

1A

1B

NC

1C

1D

1Y

GND 2Y

2D

2C

NC1

2B

2A

VCC

VCC

4V

VCC

4V

8

VCCVCC

7

6

0

5

4

VCC

4V

VCC

VCC

4V

VCC

4