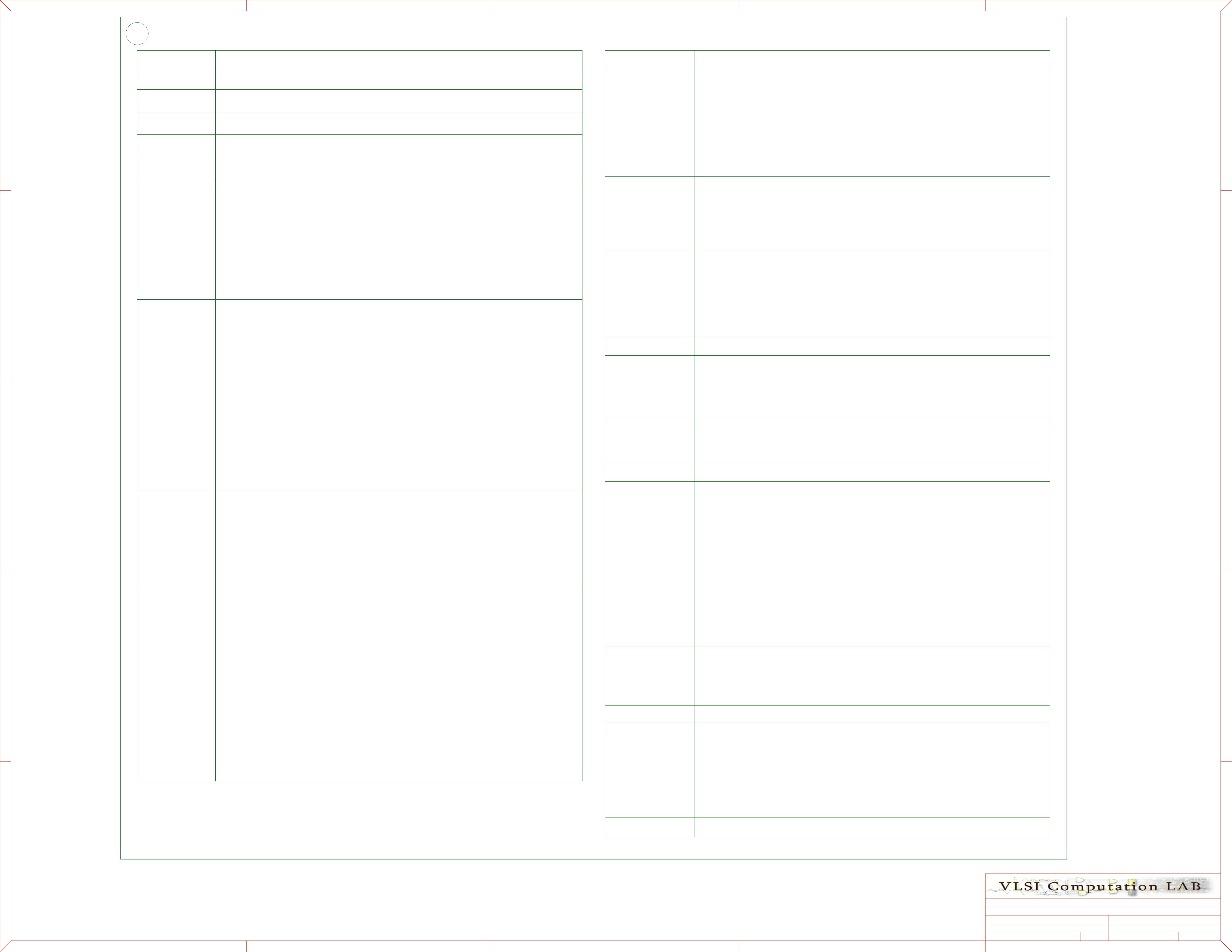

### 开源软件无线电的原理图解析 #### 一、概览 本文将深入解析一个开源软件无线电项目的原理图,该项目涉及的关键技术包括FPGA、DSP(数字信号处理)、AD(模数转换)、DA(数模转换)等核心组件。通过详细分析原理图中的各个组成部分及其功能,帮助读者理解软件无线电系统的工作机制以及各组件之间的交互。 #### 二、软件无线电基本概念 软件无线电(Software Defined Radio, SDR)是一种无线电通信系统设计方法,其特点是将传统上由硬件实现的功能(如调制/解调、滤波、编码/解码等)转移到软件层面来实现。这种灵活性使得同一个硬件平台能够支持多种无线通信标准和协议。 #### 三、关键组件分析 ##### 3.1 FPGA (Field-Programmable Gate Array) 在本项目中,采用的是Xilinx Virtex 5 SX50T FPGA作为核心处理器。FPGA作为一种可编程逻辑器件,能够根据需求灵活配置其内部的逻辑电路,非常适合用于实现复杂的数字信号处理算法。 - **功能**: 主要承担信号处理任务,如数字滤波、数据传输控制等。 - **配置**: 使用SPI接口进行配置,配置文件通过外部存储器读取。 - **数据路径**: 包括了从接收机到发射机的数据流处理过程,如解调、调制等。 ##### 3.2 DSP (Digital Signal Processing) 本项目中采用了多个DSP芯片来完成信号处理任务,例如ADC(模拟-数字转换器)、DAC(数字-模拟转换器)等。 - **ADC**: 使用了TI的ADC5682,这是一款12位的高速ADC,采样率高达500 MS/s,适合处理高频信号。 - **DAC**: 采用了TI的DAC5682,同样是12位的高速DAC,采样率也是500 MS/s,用于将数字信号转换为模拟信号。 ##### 3.3 AD (Analog-to-Digital Converter) 和 DA (Digital-to-Analog Converter) - **ADC**: TI的ADC5682,采样率500 MS/s,12位分辨率。 - **DAC**: TI的DAC5682,同样具备500 MS/s的采样率,12位分辨率。 ##### 3.4 其他关键组件 - **滤波器**: 设计采用了7阶切比雪夫低通滤波器,截止频率为140 MHz,带宽为120 MHz,纹波为0.5 dB。 - **时钟管理**: 使用了AD9516时钟发生器,为整个系统提供精确的时钟信号。 - **电源管理**: 提供了+5.2V和-5.2V电源,满足不同部件的需求。 - **存储器**: 包括Micron的DDR2 SDRAM(MT16HTF25664H–2GB)和Samsung的QDR-II SRAM(K7R323684C-EC250),用于数据缓存和程序存储。 #### 四、系统架构与数据流 - **输入**: RF信号通过前端射频模块接收后,经过ADC转换成数字信号。 - **处理**: 数字信号被送入FPGA进行初步处理,如下变频、滤波等。 - **存储**: 处理后的数据可以暂时存储在外部SDRAM中。 - **输出**: 经过处理后的数据再通过DAC转换回模拟信号,并通过射频模块发射出去。 #### 五、信号链路分析 - **模拟前端**: 包括RF Input、放大器、滤波器等,负责接收并预处理射频信号。 - **数字后端**: 主要由FPGA组成,负责信号的进一步处理,如数字滤波、解调等。 - **接口与控制**: SPI用于配置FPGA和其他外围设备;UART Lite用于与外部控制器进行通信。 #### 六、总结 本开源软件无线电项目通过精心设计的硬件平台实现了灵活的无线通信功能。FPGA作为核心处理器,承担了大部分的信号处理任务;ADC和DAC则确保了模拟信号与数字信号之间的高效转换;而各种滤波器和时钟管理芯片则保证了信号的高质量传输。通过对这些关键组件和技术的深入了解,可以更好地把握软件无线电系统的整体架构和技术细节。

剩余42页未读,继续阅读

hmbbc2015-06-11还行,看看,了解一下,谢谢

hmbbc2015-06-11还行,看看,了解一下,谢谢

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功