LogiCORE IP Video to

SDI TX Bridge v1.0

Product Guide for Vivado

Design Suite

PG178 October 2, 2013

Video to SDI TX Bridge v1.0 www.xilinx.com 2

PG178 October 2, 2013

Table of Contents

IP Facts

Chapter 1: Overview

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Licensing and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 2: Product Specification

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Interface Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Chapter 4: Customizing and Generating the Core

Vivado Integrated Design Environment (IDE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Output Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Chapter 5: Constraining the Core

Required Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Clock Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Clock Placement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Banking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Transceiver Placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

I/O Standard and Placement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Send Feedback

Video to SDI TX Bridge v1.0 www.xilinx.com 3

PG178 October 2, 2013

Chapter 6: Simulation

Chapter 7: Synthesis and Implementation

Chapter 8: Test Bench

Directory and File Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Appendix A: Verification, Compliance, and Interoperability

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Hardware Testing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Interoperability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Appendix C: Additional Resources

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Notice of Disclaimer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Send Feedback

Video to SDI TX Bridge v1.0 www.xilinx.com 4

PG178 October 2, 2013 Product Specification

Introduction

The LogiCORE IP Video to SDI TX Bridge

connects the video output of the AXI4-Stream

to Video Output core to the SDI transmitter

input of the SMPTE SDI core. The input is Video

data with explicit synchronization signals. The

output is an SDI virtual interface with one to

four 10-bit data streams and embedded

synchronization.

Features

• Embeds synchronization signals into the

SDI data stream.

• Creates and embeds line numbers into the

SDI data stream.

• Generates clock enables for SDI-SDI and

3G-SDI level B modes.

• Supports YCbCr data format at 10-bits per

component.

• Supports SD-SDI, HD-SDI, 3G-SDI Level A,

and 3G-SDI Level B.

• Re-orders sequential video data to parallel

data in 3G Level B.

• Supports interlaced and progressive line

standards.

IP Facts

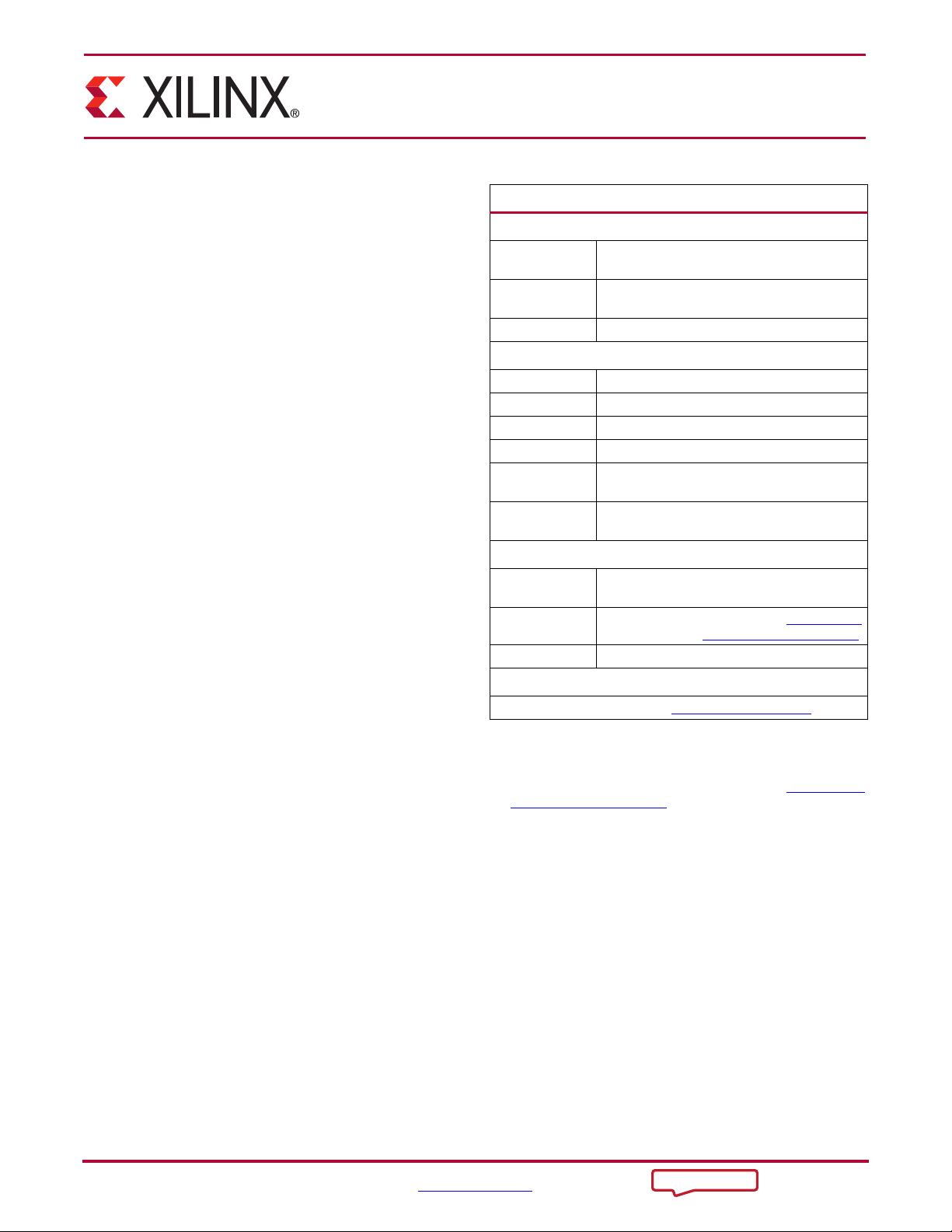

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

Zynq®-7000, Artix®-7, Virtex®-7, Kintex®-7

Supported User

Interfaces

N/A

Resources See Ta ble 2 - 1.

Provided with Core

Design Files Verilog Source Code

Example Design Not Provided

Test Bench Verilog

Constraints File XDC

Simulation

Model

Verilog Source Code

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry

Vivado® Design Suite

IP Integrator

Simulation

For support simulators, see the X

ilinx Design

Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx @ www.xilinx.com/support

Notes:

1. For a complete list of supported devices, see Vivado IP

catalog.

2. For the supported versions of the tools, see the Xilinx Design

Tools: Release Notes Guide.

Send Feedback

Video to SDI TX Bridge v1.0 www.xilinx.com 5

PG178 October 2, 2013

Chapter 1

Overview

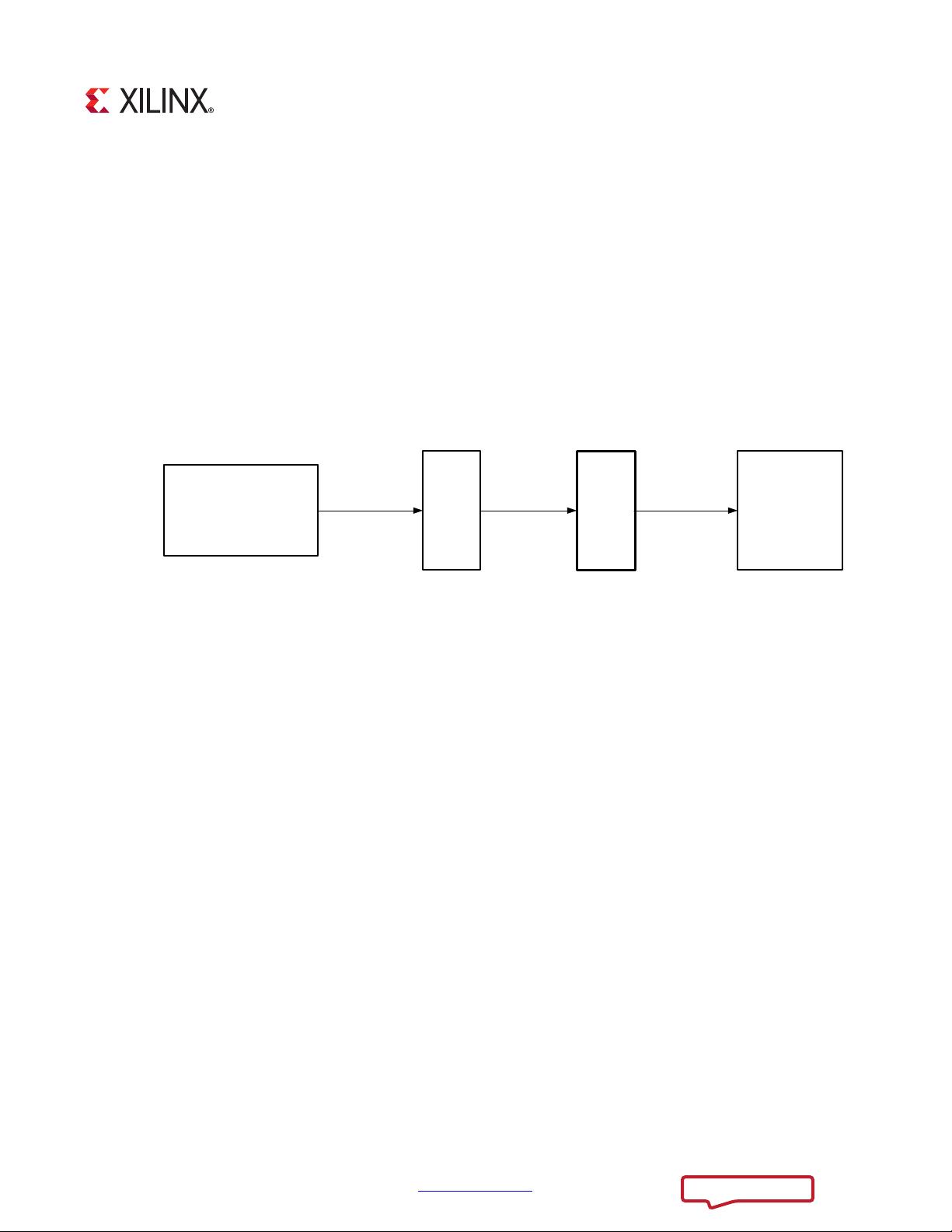

Broadcast video is commonly transmitted through SDI. Xilinx video processing cores use

the AXI4-Stream protocol to transfer video between cores. The Video to SDI TX Bridge, in

concert with the SMPTE SD/HD/3G-SDI core (SMPTE SDI) and AXI4-Stream to Video Out

core, enables video processed with the Xilinx video cores to be transmitted via SDI.

Figure 1-1 shows the path for AXI4-Stream video processing to SDI TX.

The Video to SDI TX Bridge converts video with a single data stream and explicit

synchronization (horizontal blank, vertical blank, and field identification) to an SDI virtual

interface with multiple data streams and embedded synchronization.

The Video to SDI TX Bridge consists of two main functions: Data Formatter, and Sync and

Line Number Embedder. Figure 1-2 shows these functions and the main inputs and outputs

of the core.

X-Ref Target - Figure 1-1

Figure 1-1: Path from AXI4-Stream Video Processing to SDI

9LGHR3URFHVVLQJ

9LGHRWR6',7;

%ULGJH

$;,6WUHDPWR

9LGHR2XW

6037(

6',

7;

$;,6WUHDP 9LGHR 6',1DWLYH

;

Send Feedback