没有合适的资源?快使用搜索试试~ 我知道了~

datasheet for csr 57e687cg.pdf

需积分: 48 4 下载量 63 浏览量

2021-01-28

14:53:11

上传

评论

收藏 1.15MB PDF 举报

温馨提示

试读

104页

csr 57e687cg 蓝牙芯片资料

资源详情

资源评论

资源推荐

Features

_äìÉ`çêÉ

∆

RJjìäíáãÉÇá~=bñíÉêå~ä

■

Fully qualified Bluetooth v2.1 + EDR specification

system

■

Best-in-class Bluetooth radio with 8dBm transmit

power and -90dBm receive sensitivity

■

64MIPS Kalimba DSP coprocessor

■

16-bit internal stereo codec: 95dB SNR for DAC

■

Low-power 1.5V operation, 1.8V to 3.6V I/O

■

Integrated 1.5V and 1.8V linear regulators

■

Integrated switch-mode regulator

■

Integrated battery charger

■

USB, I²C and UART with dual-port bypass mode

to 4Mbits/s

■

Supports up to 32Mb of external flash memory

(8Mb typical requirement)

■

Multi-configurable I²S, PCM or SPDIF interface

■

Enhanced audibility and noise cancellation

■

8 x 8 x 1.2mm, 0.5mm pitch 169-ball TFBGA

■

Support for IEEE 802.11 coexistence

■

Green (RoHS compliant and no antimony or

halogenated flame retardants)

Fully Qualified Single-chip

Bluetooth

®

v2.1 + EDR System

Production Information

BC57E687C

Issue 4

General Description

The _äìÉ`çêÉ

∆

RJjìäíáãÉÇá~=bñíÉêå~ä is a product from

CSR's Connectivity Centre. It is a single-chip radio and

baseband IC for Bluetooth 2.4GHz systems.

BlueCore5‑Multimedia External interfaces up to 32Mb

of external flash memory. When used with the CSR

Bluetooth stack, it provides a fully compliant Bluetooth

v2.1 + EDR specification system for data and voice.

BlueCore5‑Multimedia External contains the Kalimba

DSP coprocessor with double the MIPS of

BlueCore3‑Multimedia External, supporting enhanced

audio applications.

BlueCore5‑Multimedia External is designed to reduce

the number of external components required which

ensures production costs are minimised. The device

incorporates auto-calibration and BIST routines to

simplify development, type approval and production

test.

Applications

■

High-quality stereo wireless headsets

■

High-quality mono headsets

■

Hands-free car kits

■

Wireless speakers

■

VoIP handsets

■

Analogue and USB multimedia dongles

■

Bluetooth automotive wireless gateways

To improve the performance of both Bluetooth and

802.11 b/g co-located systems, dedicated hardware

has been implemented to support coexistence

features including support for CSR's Unity coexistence

scheme.

For radio performance over temperature and

additional performance information refer to the

BlueCore

®

5‑Multimedia External Performance

Specification

.

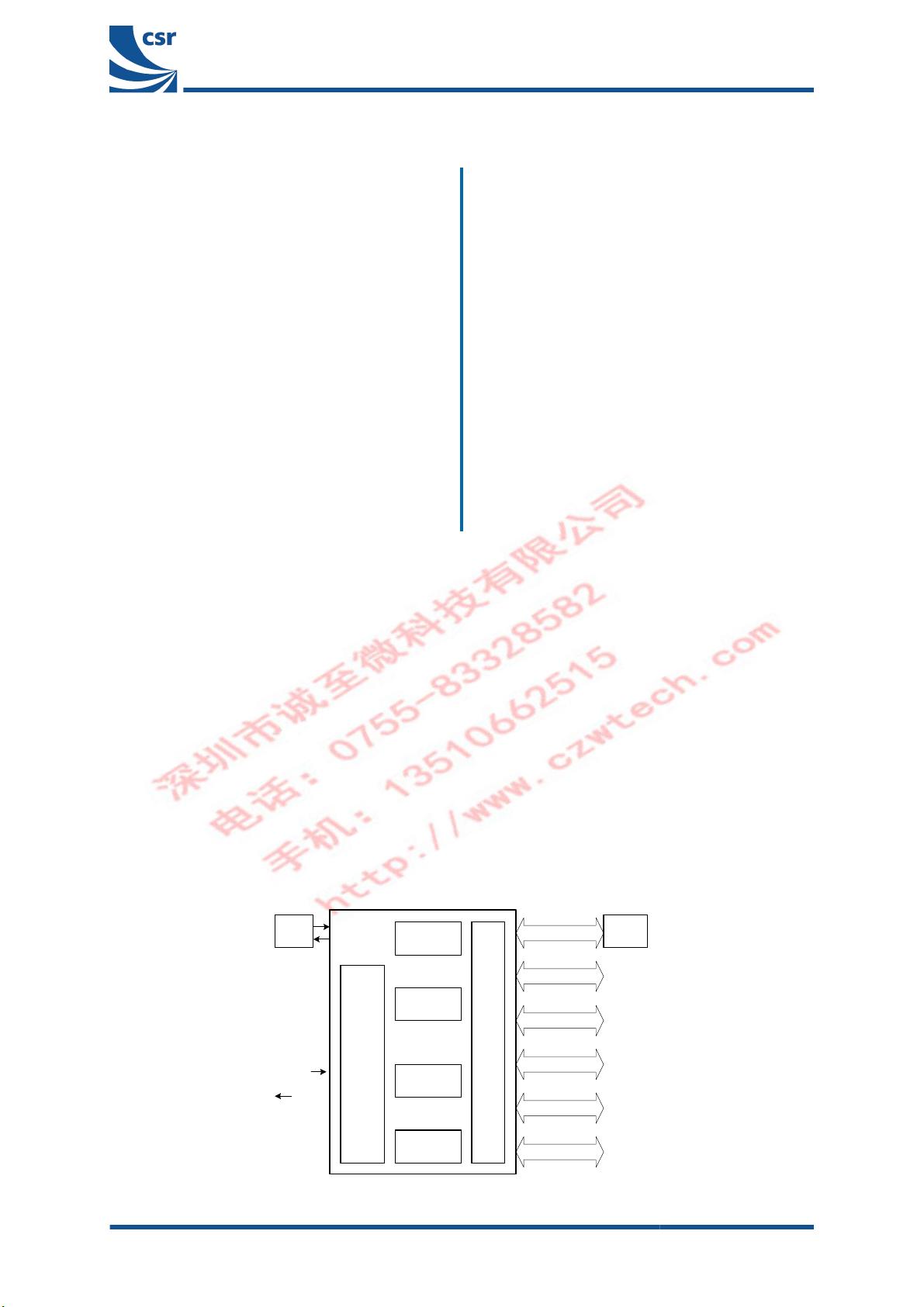

2.4

GHz

Radio

I/O

RF IN

RF OUT

Flash

RAM

Baseband

DSP

MCU

Kalimba

DSP

XTAL

External Memory

UART/USB

PIO

Audio In/Out

PCM/I

2

S/SPDIF

SPI

CS-121064-DSP4

Production Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2006 - 2010

Page 1 of 104

_äìÉ`çêÉRJjìäíáãÉÇá~=bñíÉêå~ä=E_`RTbSUT`F Data Sheet

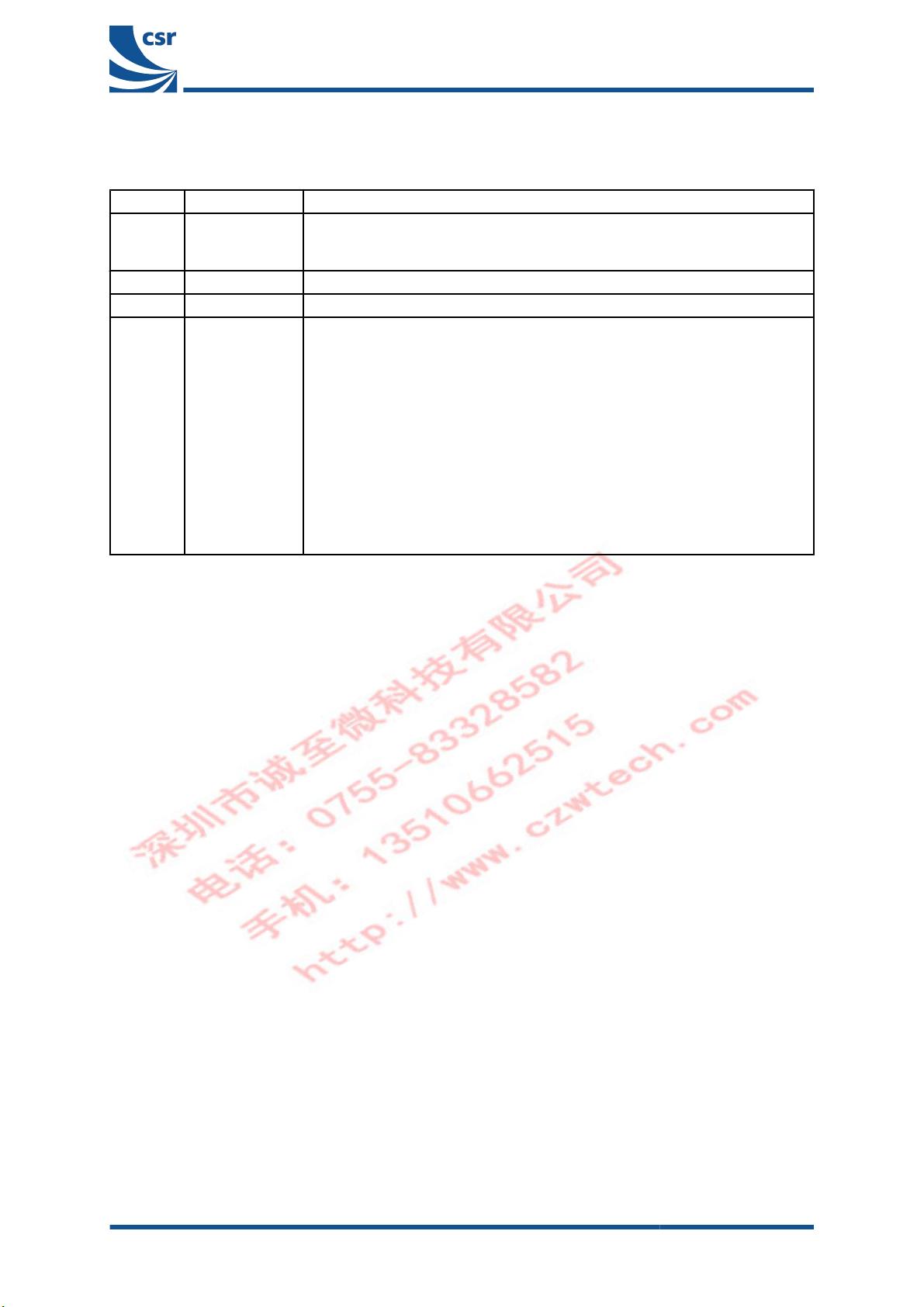

Document History

Revision Date Change Reason

Issue 1 10 JUL 08 Original publication of document as BlueCore5-Multimedia External changed to

revision C silicon.

Data sheet replaces revision B silicon, document number CS-101568-DSP.

Issue 2 15 JUL 08 USB interface updated

Issue 3 08 MAY 09 Internal release only.

Issue 4 09 FEB 10 SPI interface updated.

High-voltage linear regulator description updated.

Electrical Characteristics updates:

■

Correction of the units for the stereo codec ADC mic mode impedance

■

Reworded output current parameter in all linear regulator electrical

characterisation tables to remove ambiguity

■

ESD precautions section moved to Electrical Characteristics

Tape dimensions added.

Status Information updated.

Power Consumption conditions updated.

Various editorial updates.

If you have any comments about this document, email comments@csr.com giving

number, title and section with your feedback.

Document History

CS-121064-DSP4

Production Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2006 - 2010

Page 2 of 104

_äìÉ`çêÉRJjìäíáãÉÇá~=bñíÉêå~ä=E_`RTbSUT`F Data Sheet

Status Information

The status of this Data Sheet is Production Information.

CSR Product Data Sheets progress according to the following format:

Advance Information

Information for designers concerning CSR product in development. All values specified are the target values of the

design. Minimum and maximum values specified are only given as guidance to the final specification limits and must

not be considered as the final values.

All detailed specifications including pinouts and electrical specifications may be changed by CSR without notice.

Pre-production Information

Pinout and mechanical dimension specifications finalised. All values specified are the target values of the design.

Minimum and maximum values specified are only given as guidance to the final specification limits and must not be

considered as the final values.

All electrical specifications may be changed by CSR without notice.

Production Information

Final Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.

Production Data Sheets supersede all previous document versions.

Life Support Policy and Use in Safety-critical Applications

CSR's products are not authorised for use in life-support or safety-critical applications. Use in such applications is

done at the sole discretion of the customer. CSR will not warrant the use of its devices in such applications.

CSR Green Semiconductor Products and RoHS Compliance

BlueCore5‑Multimedia External devices meet the requirements of Directive 2002/95/EC of the European Parliament

and of the Council on the Restriction of Hazardous Substance (RoHS).

BlueCore5‑Multimedia External devices are also free from halogenated or antimony trioxide-based flame retardants

and other hazardous chemicals. For more information, see CSR's

Environmental Compliance Statement for CSR

Green Semiconductor Products

.

Trademarks, Patents and Licences

Unless otherwise stated, words and logos marked with

™

or

®

are trademarks registered or owned by CSR plc or its

affiliates. Bluetooth

®

and the Bluetooth

®

logos are trademarks owned by Bluetooth

®

SIG, Inc. and licensed to

CSR. Other products, services and names used in this document may have been trademarked by their respective

owners.

The publication of this information does not imply that any license is granted under any patent or other rights owned

by CSR plc and/or its affiliates.

CSR reserves the right to make technical changes to its products as part of its development programme.

While every care has been taken to ensure the accuracy of the contents of this document, CSR cannot accept

responsibility for any errors.

Refer to www.csrsupport.com for compliance and conformance to standards information.

No statements or representations in this document are to be construed as advertising, marketing, or offering for sale

in the United States imported covered products subject to the Cease and Desist Order issued by the U.S.

International Trade Commission in its Investigation No. 337-TA-602. Such products include SiRFstarIII chips that

operate with SiRF software that supports SiRFInstantFix, and/or SiRFLoc servers, or contains SyncFreeNav

functionality.

Status Information

CS-121064-DSP4

Production Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2006 - 2010

Page 3 of 104

_äìÉ`çêÉRJjìäíáãÉÇá~=bñíÉêå~ä=E_`RTbSUT`F Data Sheet

Contents

1 Device Details ............................................................................................................................................... 10

2 Functional Block Diagram ............................................................................................................................ 11

3 Package Information ..................................................................................................................................... 12

3.1 Pinout Diagram .................................................................................................................................... 12

3.2 Device Terminal Functions .................................................................................................................. 13

3.3 Package Dimensions ........................................................................................................................... 21

3.4 PCB Design and Assembly Considerations ......................................................................................... 22

3.5 Typical Solder Reflow Profile ............................................................................................................... 22

4 Bluetooth Modem .......................................................................................................................................... 23

4.1 RF Ports ............................................................................................................................................... 23

4.1.1 RF_N and RF_P ..................................................................................................................... 23

4.2 RF Receiver ......................................................................................................................................... 23

4.2.1 Low Noise Amplifier ............................................................................................................... 23

4.2.2 RSSI Analogue to Digital Converter ....................................................................................... 23

4.3 RF Transmitter ..................................................................................................................................... 23

4.3.1 IQ Modulator .......................................................................................................................... 23

4.3.2 Power Amplifier ...................................................................................................................... 24

4.3.3 Transmit RF Power Control for Class 1 Applications (TX_PWR) ........................................... 24

4.4 Bluetooth Radio Synthesiser ............................................................................................................... 25

4.5 Baseband ............................................................................................................................................. 25

4.5.1 Burst Mode Controller ............................................................................................................ 25

4.5.2 Physical Layer Hardware Engine ........................................................................................... 25

4.6 Basic Rate Modem .............................................................................................................................. 25

4.7 Enhanced Data Rate Modem .............................................................................................................. 25

5 Clock Generation .......................................................................................................................................... 27

5.1 Clock Architecture ................................................................................................................................ 27

5.2 Input Frequencies and PS Key Settings .............................................................................................. 27

5.3 External Reference Clock .................................................................................................................... 28

5.3.1 Input (XTAL_IN) ..................................................................................................................... 28

5.3.2 XTAL_IN Impedance in External Mode .................................................................................. 28

5.3.3 Clock Start-up Delay ....................................................................................................

.......... 28

5.3.4 Clock Timing Accuracy ........................................................................................................... 28

5.4 Crystal Oscillator (XTAL_IN, XTAL_OUT) ........................................................................................... 29

5.4.1 Load Capacitance .................................................................................................................. 30

5.4.2 Frequency Trim ...................................................................................................................... 30

5.4.3 Transconductance Driver Model ............................................................................................ 31

5.4.4 Negative Resistance Model ................................................................................................... 31

5.4.5 Crystal PS Key Settings ......................................................................................................... 31

6 Bluetooth Stack Microcontroller .................................................................................................................... 32

6.1 Programmable I/O Ports, PIO and AIO ................................................................................................ 32

6.2 TCXO Enable OR Function ................................................................................................................. 32

6.3 WLAN Coexistence Interface ............................................................................................................... 33

7 Kalimba DSP ................................................................................................................................................ 34

8 Memory Interface and Management ............................................................................................................. 35

8.1 Memory Management Unit .................................................................................................................. 35

8.2 System RAM ........................................................................................................................................ 35

8.3 Kalimba DSP RAM .............................................................................................................................. 35

8.4 External Memory Driver ....................................................................................................................... 35

8.5 External Flash Memory (32Mb) ........................................................................................................... 35

8.6 Off-chip Program Memory ................................................................................................................... 35

Contents

CS-121064-DSP4

Production Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2006 - 2010

Page 4 of 104

_äìÉ`çêÉRJjìäíáãÉÇá~=bñíÉêå~ä=E_`RTbSUT`F Data Sheet

8.6.1 Minimum Flash Specification ................................................................................................. 36

8.6.2 Common Flash Interface ........................................................................................................ 36

8.6.3 Virtual Machine Requirements ............................................................................................... 37

8.6.4 Memory Timing ...................................................................................................................... 38

9 Serial Interfaces ............................................................................................................................................ 40

9.1 UART Interface .................................................................................................................................... 40

9.1.1 UART Configuration While Reset is Active ............................................................................ 41

9.1.2 UART Bypass Mode ............................................................................................................... 42

9.1.3 Current Consumption in UART Bypass Mode ........................................................................ 42

9.2 USB Interface ...................................................................................................................................... 42

9.3 Programming and Debug Interface ...................................................................................................... 43

9.3.1 Instruction Cycle ..................................................................................................................... 43

9.3.2 Multi-slave Operation ............................................................................................................. 43

9.4 I²C Interface ......................................................................................................................................... 43

9.4.1 Software I²C Interface ............................................................................................................ 43

9.4.2 Bit-serialiser Interface ............................................................................................................ 44

10 Audio Interface .............................................................................................................................................. 45

10.1 Audio Input and Output ........................................................................................................................ 45

10.2 Stereo Audio Codec Interface .............................................................................................................. 45

10.2.1 Stereo Audio Codec Block Diagram ....................................................................................... 46

10.2.2 Stereo Codec Set-up .............................................................................................................. 46

10.2.3 ADC ........................................................................................................................................ 47

10.2.4 ADC Sample Rate Selection .................................................................................................. 47

10.2.5 ADC Digital Gain .................................................................................................................... 47

10.2.6 ADC Analogue Gain ............................................................................................................... 47

10.2.7 DAC ........................................................................................................................................ 48

10.2.8 DAC Sample Rate Selection .................................................................................................. 48

10.2.9 DAC Digital Gain .................................................................................................................... 48

10.2.10 DAC Analogue Gain ............................................................................................................... 49

10.2.11 IEC 60958 Interface ............................................................................................................... 49

10.2.12 Microphone Input ................................................................................................................... 50

10.2.13 Line Input ............................................................................................................................... 53

10.2.14 Output Stage .......................................................................................................................... 54

10.2.15 Mono Operation ..................................................................................................................... 55

10.2.16 Side Tone ............................................................................................................................... 55

10.2.17 Integrated Digital Filter ........................................................................................................... 55

10.3 PCM Interface ...................................................................................................................................... 56

10.3.1 PCM Interface Master/Slave .................................................................................................. 56

10.3.2 Long Frame Sync ................................................................................................................... 57

10.3.3 Short Frame Sync .................................................................................................................. 57

10.3.4 Multi-slot Operation ................................................................................................................ 58

10.3.5 GCI Interface .......................................................................................................................... 58

10.3.6 Slots and Sample Formats ..................................................................................................... 59

10.3.7 Additional Features ................................................................................................................ 59

10.3.8 PCM Timing Information ........................................................................................................ 60

10.3.9 PCM_CLK and PCM_SYNC Generation ................................................................................ 63

10.3.10 PCM Configuration ................................................................................................................. 63

10.4 Digital Audio Interface (I²S) .................................................................................................................. 65

11 Power Control and Regulation ...................................................................................................................... 70

11.1 Power Sequencing ............................................................................................................................... 70

11.2 External Voltage Source ...................................................................................................................... 71

11.3 Switch-mode Regulator ....................................................................................................................... 71

11.4 High-voltage Linear Regulator ............................................................................................................. 71

11.5 Low-voltage Linear Regulator .............................................................................................................. 71

Contents

CS-121064-DSP4

Production Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2006 - 2010

Page 5 of 104

_äìÉ`çêÉRJjìäíáãÉÇá~=bñíÉêå~ä=E_`RTbSUT`F Data Sheet

剩余103页未读,继续阅读

Michael_Tse

- 粉丝: 1

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0