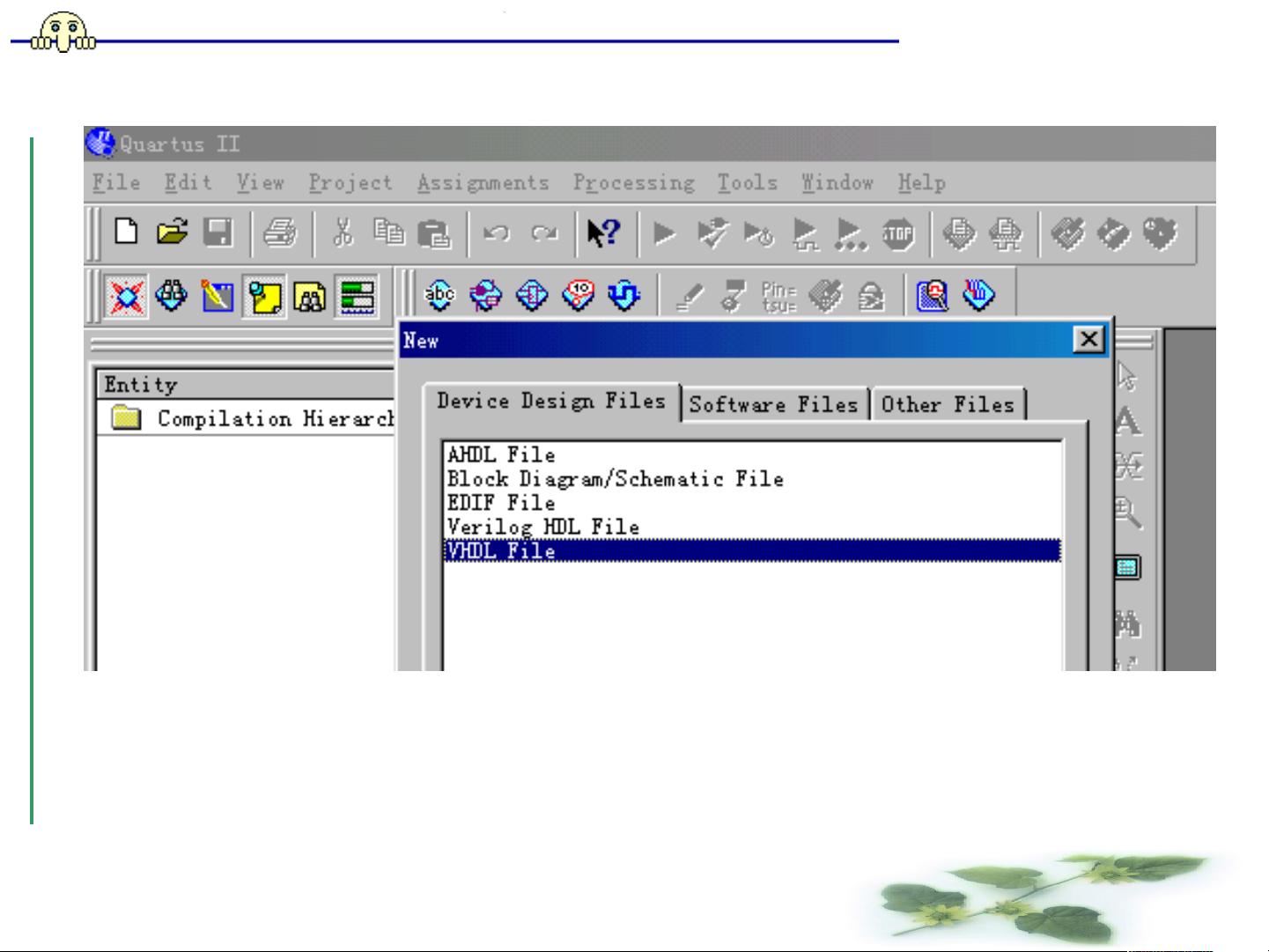

Quartus II 设计向导是Altera公司提供的一个用于FPGA(Field-Programmable Gate Array)设计的集成开发环境。本章主要讲解如何利用Quartus II进行设计流程,特别是针对频率计的设计和优化。 2.1 频率计的VHDL设计 在VHDL设计中,频率计是一个常见的数字系统,用于测量输入信号的频率。VHDL是一种硬件描述语言,用于描述数字系统的结构和行为。在创建频率计的VHDL设计时,首先要建立工作库目录,例如在D:\ftest,确保设计文件的有序存放。每个设计项目应被视为一个独立的工程,并在不同的文件夹中保存,以保持组织清晰。 2.1.1 创建工程和编辑设计文件 创建新的工程文件夹后,使用Quartus II的文本编辑器来编写和保存设计文件。在文件菜单中选择“New”,然后在“Device Design Files”中选择VHDL语言。例如,我们可以创建一个名为CNT1的计数器模块,该模块由以下代码实现: ```vhdl LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT1 IS PORT ( CLOCK : IN STD_LOGIC; ACLR : IN STD_LOGIC; CLK_EN : IN STD_LOGIC; Q : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); END CNT1; ARCHITECTURE behav OF CNT1 IS SIGNAL CQI : STD_LOGIC_VECTOR(31 DOWNTO 0); BEGIN PROCESS(CLOCK, ACLR, CLK_EN) BEGIN IF ACLR = '1' THEN CQI <= (OTHERS=>'0'); ELSIF CLOCK'EVENT AND CLOCK = '1' THEN IF CLK_EN = '1' THEN CQI <= CQI + 1; END IF; END IF; END PROCESS; Q <= CQI; END behav; ``` 2.2 使用宏功能块设计频率计 宏功能块是预先定义的功能模块,可以简化设计过程。在频率计的设计中,可能需要利用Quartus II提供的宏功能来构建特定部分,例如计数器或比较器,以提高设计效率。 2.3 和2.4 嵌入式系统块ESB的应用 嵌入式系统块(Embedded System Blocks, ESB)是Quartus II提供的一种硬件资源,允许设计师快速集成常见的数字系统组件,如定时器、计数器等。在频率计设计中,可能需要使用ESB来构建复杂的时序控制逻辑。 2.5 时序驱动式优化编译方法 在Quartus II中,设计编译过程会进行时序优化,以提高电路的速度性能。时序驱动式优化是指在满足设计约束的前提下,调整逻辑门的连接和时序,以缩短关键路径,提升系统速度。 2.6 频率计结构原理 频率计通常包括计数器、时序控制器和显示接口等部分。计数器用于累计输入信号的周期,时序控制器管理计数过程,而显示接口则负责将测量结果转化为可读格式。 2.7 Quartus II优化特性 Quartus II提供了多种优化特性,如逻辑综合、面积优化、速度优化等,帮助设计师优化FPGA配置,减少资源占用,提高运行速度。此外,还包括约束设置,以确保设计满足时序要求。 Quartus II设计向导为用户提供了详尽的指导,涵盖了从创建工程、编写VHDL代码到利用宏功能块和嵌入式系统块,以及利用时序驱动式优化和Quartus II的各种优化特性的整个设计流程,旨在帮助用户高效地完成复杂数字系统的FPGA实现。

剩余63页未读,继续阅读

- 粉丝: 2

- 资源: 9

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功