没有合适的资源?快使用搜索试试~ 我知道了~

EDA技术实验教案(全加器。十进制频率计。数字秒表。。。}

需积分: 10 21 下载量 67 浏览量

2011-06-05

03:41:02

上传

评论

收藏 625KB DOC 举报

温馨提示

试读

27页

EDA技术实验教案 实验一 1位全加器原理图输入设计 实验五 4位十进制频率计VHDL文本输入设计 实验七 数字秒表VHDL文本输入设计 实验八 交通灯信号控制器VHDL文本输入设计

资源推荐

资源详情

资源评论

EDA 技术实验教案

实验一 1 位全加器原理图输入设计

一、实验目的

1、 熟悉 MAX+plusII 软件的基本使用方法。

2、 熟悉 GW48-ES EDA 实验开发系统的基本使用方法。

3、 了解原理图输入设计方法。

二、实验内容

设计并调试好一个 1 位二进制全加器,并用 GW48-ES EDA 实验开发系

统(拟采用的实验芯片的型号为 EPF10K20TC144-4 或 EP1K30TC144-3)进

行系统仿真、硬件验证。设计 1 位二进制全加器时要求先用基本门电路设计一

个 1 位二进制半加器,再由基本门电路和 1 位二进制半加器构成 1 位二进制全

加器。

三、实验条件

1、开发条件:MAX+plusII

2、实验设备:GW48-ES EDA 实验开发系统、联想电脑

3、拟用芯片:EPF10K20TC144-4 或 EP1K30TC144-3

四、实验设计

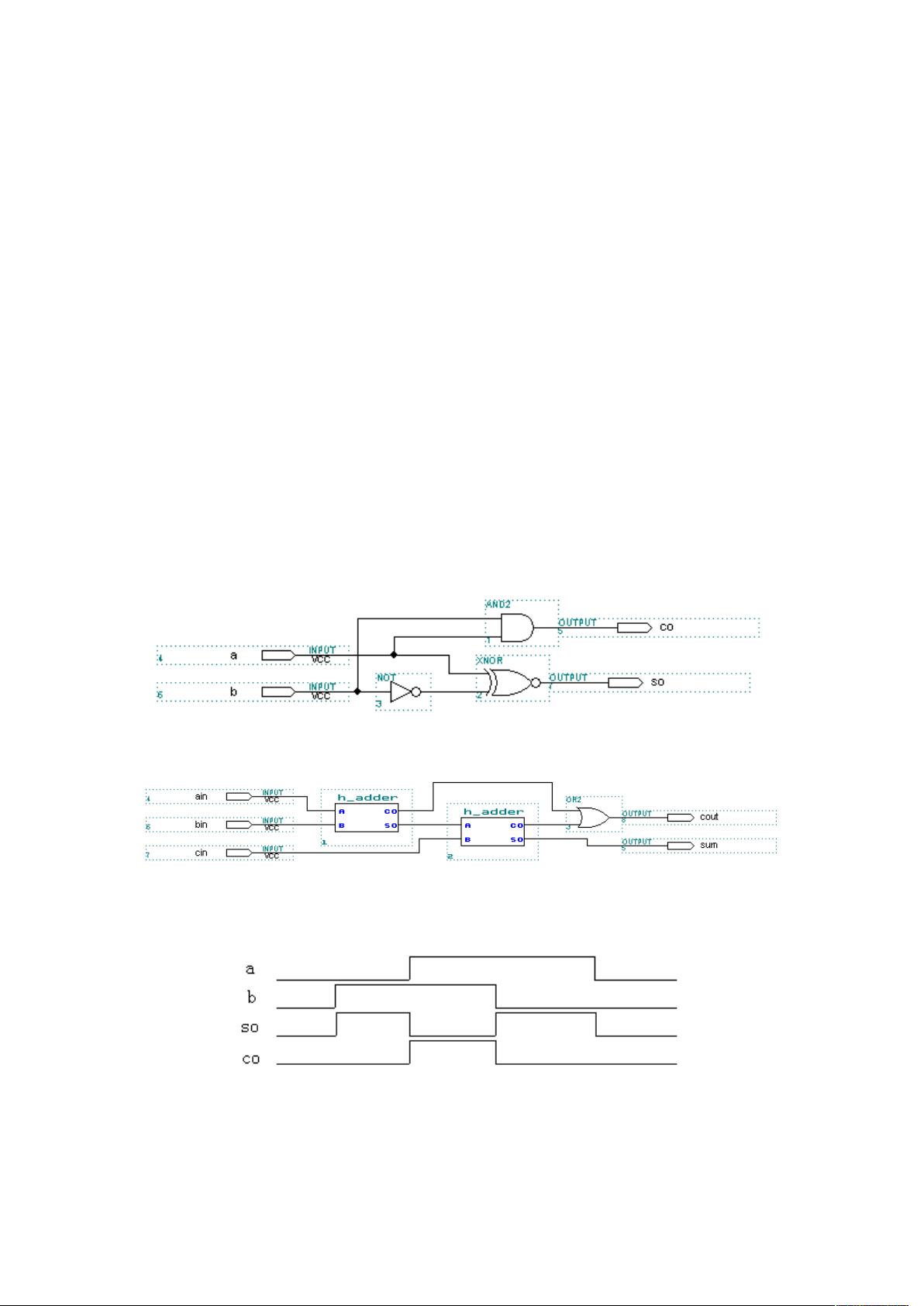

半加器(h_adder.gdf)

全加器(f_adder.gdf)

实验结果

半加器仿真波形

半加器引脚锁定

实验芯片:EPF10K20TC144-4 选用模式:模式 5

设计实体 I/O 标识 I/O 来源/去向 结构图上的信号名 芯片引脚号

a

键 1

PIO0 8

b

键 2

PIO1 9

so

二极管 D1

PIO8 20

co

二极管 D2

PIO9 21

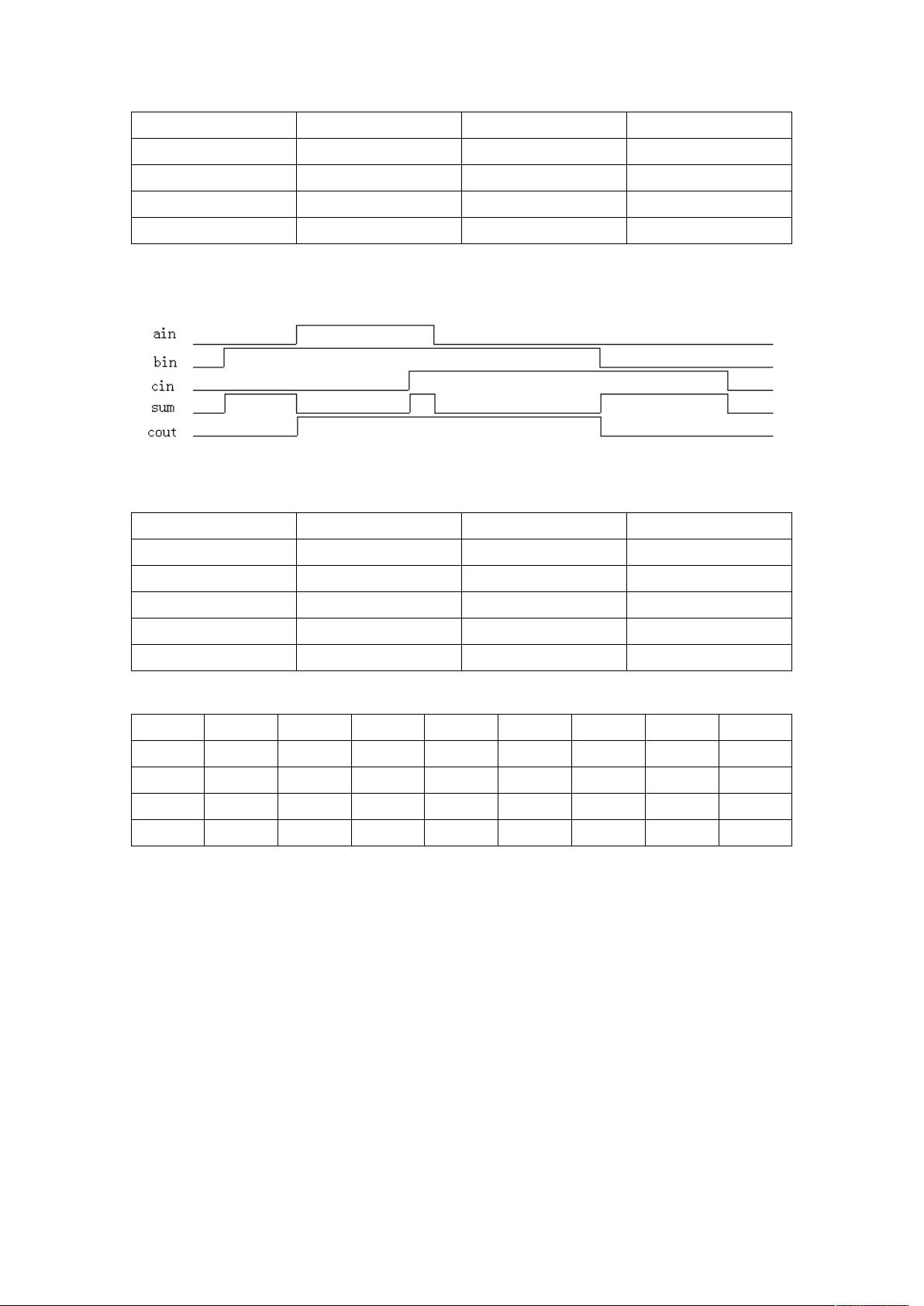

全加器仿真波形

全加器引脚锁定

实验芯片:EPF10K20TC144-4 选用模式:模式 5

设计实体 I/O 标识 I/O 来源/去向 结构图上的信号名 芯片引脚号

ain

键 1

PIO0 8

bin

键 2

PIO1 9

cin

键 3

PIO2 10

sum

二极管 D1

PIO8 20

cout

二极管 D2

PIO9 21

全加器真值表

ain

0 1 0 1 0 1 0 1

bin

0 0 1 1 0 0 1 1

cin

0 0 0 0 1 1 1 1

sum

0 1 1 0 1 0 0 1

cout

0 0 0 1 0 1 1 1

实验二 1 位全加器 VHDL 文本输入设计

一、实验目的

1、熟悉 MAX+plusII 软件的基本使用方法。

2、熟悉 GW48-ES EDA 实验开发系统的基本使用方法。

3、了解 VHDL 文本输入设计方法。

二、实验内容

设计并调试好一个 1 位二进制全加器,并用 GW48-ES EDA 实验开发系

统(拟采用的实验芯片的型号为 EPF10K20TC144-4 或 EP1K30TC144-3)进

行系统仿真、硬件验证。设计 1 位二进制全加器时要求先设计一个或门和一个

1 位二进制半加器,再由或门和 1 位二进制半加器构成 1 位二进制全加器。

三、实验条件

1、开发条件:MAX+plusII

2、实验设备:GW48-ES EDA 实验开发系统、联想电脑

3、拟用芯片:EPF10K20TC144-4 或 EP1K30TC144-3

四、实验设计

--或门逻辑描述(or2a.vhd)

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC );

END ENTITY or2a;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE one;

--半加器描述(h_adder.vhd)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder is

BEGIN

so <= NOT(a XOR (NOT b)) ;

co <= a AND b ;

END ARCHITECTURE fh1;

--1 位二进制全加器顶层设计描述(f_adder.vhd)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT (ain, bin, cin : IN STD_LOGIC;

Cout, sum : OUT STD_LOGIC );

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS

COMPONENT h_adder

PORT ( a, b : IN STD_LOGIC;

Co, so : OUT STD_LOGIC);

END COMPONENT ;

COMPONENT or2a

PORT (a, b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d, e, f : STD_LOGIC;

BEGIN

u1 : h_adder PORT MAP(a=>ain, b=>bin,

co=>d, so=>e);

u2 : h_adder PORT MAP(a=>e, b=>cin,

co=>f, so=>sum);

u3 : or2a PORT MAP(a=>d, b=>f, c=>cout);

END ARCHITECTURE fd1 ;

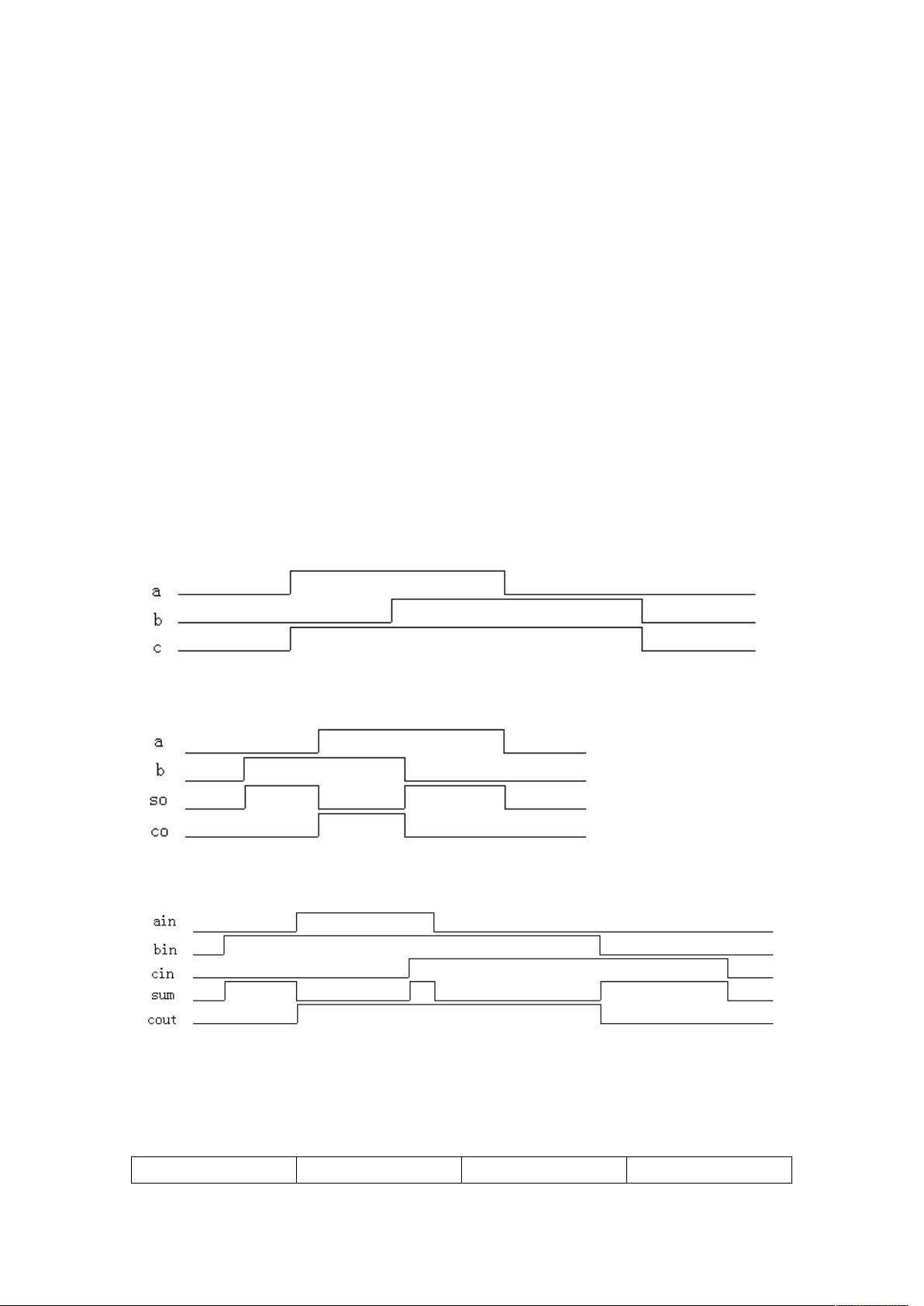

或门仿真波形

半加器仿真波形

全加器仿真波形

全加器引脚锁定

实验芯片:EPF10K20TC144-4 选用模式:模式 5

设计实体 I/O 标识 I/O 来源/去向 结构图上的信号名 芯片引脚号

剩余26页未读,继续阅读

资源评论

雕风塑影

- 粉丝: 109

- 资源: 12

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功