没有合适的资源?快使用搜索试试~ 我知道了~

Advance Information AR0144AT Developer Guide1/4−Inch CMOS Digita...

需积分: 49 51 下载量 2 浏览量

2020-04-07

08:59:57

上传

评论

收藏 487KB PDF 举报

温馨提示

试读

44页

ar0144开发手册(不包含register),含有dvp协议介绍,写的较为清晰可以参考,Advance Information AR0144AT Developer Guide1/4−Inch CMOS Digital Image Sensor

资源推荐

资源详情

资源评论

© Semiconductor Components Industries, LLC, 2016

October, 2017 − Rev. P0

1 Publication Order Number:

AND9663/D

AND9669

Advance Information

AR0144AT Developer Guide

1/4−Inch CMOS Digital Image Sensor

INTRODUCTION

This Developer Guide provides detailed descriptions and

usage guidelines for various features of the AR0144AT

Global Shutter Sensor. Also provided are guidelines for

optimal settings for various use cases. For detailed electrical

and timing specifications or register descriptions, refer to

the AR0144AT Data Sheet and the AR0144AT Register

Reference documents (AND9541/D), respectively.

OPTIMAL SETTING GUIDELINES

The AR0144AT Global Shutter Sensor has many built-in

features and is capable of many resolutions and frame rates.

Guidelines for setting resolution and frame rate are provided

in this section. Detailed settings for the many features are

provided throughout the remainder of this Developer Guide.

The AR0144AT includes the ON Semiconductor Register

Wizard tool which can be used to create appropriate settings.

RESOLUTION

The ON Semiconductor AR0144AT sensor is capable of

a maximum resolution of 1280 x 800 at up to 60 fps, or it may

be configured to run 720p at 66 fps. Registers y_addr_start,

x_addr_start, y_addr_end, and x_addr_end are used to

specify the image window. The minimum value for

x_addr_start is 0 and the maximum value for x_addr_end is

1279. The minimum y_addr_start and maximum

y_addr_end are 0 and 799, respectively.

FRAME RATE

Achieving the desired frame rate at the proper resolution

is a balancing act between row timing and the number of

rows in the image. Integration time and the pixel clock

frequency are additional factors. The minimum line length

is 1488 pixel clocks which enables a frame rate of 60 fps.

BLANKING CONTROL

Horizontal blanking and vertical blanking times are

controlled by the LINE_LENGTH_PCK and

FRAME_LENGTH_LINES registers, respectively.

The actual imager timing is described in the Frame Time

section of this Developer Guide.

This document contains information on a product under development.

ON Semiconductor reserves the right to change or discontinue this

product without notice.

This document, and the information contained herein, is CONFIDENTIAL AND

PROPRIETARY and the property of Semiconductor Components Industries,

LLC., dba ON Semiconductor. It shall not be used, published, disclosed or

disseminated outside of the Company, in whole or in part, without the written

permission of ON Semiconductor. Reverse engineering of any or all of the

information contained herein is strictly prohibited.

E 2017, SCILLC. All Rights Reserved.

APPLICATION NOTE

www.onsemi.com

AND9669

CONFIDENTIAL AND PROPRIETARY

NOT FOR PUBLIC RELEASE

www.onsemi.com

2

Table of Contents

Introduction 1............................................................................................

Optimal Setting Guidelines . 1...............................................................................

Resolution . 1.............................................................................................

Frame Rate 1............................................................................................

Blanking Control 1........................................................................................

Output Data Format 3.....................................................................................

Exposure . 5..............................................................................................

Real−Time Context Switching 6.............................................................................

Switching Contexts . 8.....................................................................................

Features 8...............................................................................................

Grid Feature 24...........................................................................................

Embedded Data and Statistics Within Image . 32...............................................................

Compression . 40..........................................................................................

Two−Wire Serial Interface CRC. 40..........................................................................

Reading the Sensor Fuse ID 43.............................................................................

AND9669

CONFIDENTIAL AND PROPRIETARY

NOT FOR PUBLIC RELEASE

www.onsemi.com

3

OUTPUT DATA FORMAT

The AR0144AT image data is read out in a progressive

scan. Valid image data is surrounded by horizontal and

vertical blanking (see Figure 1). The amount of horizontal

row time (in clocks) is programmable through R0x300C.

The amount of vertical frame time (in rows) is

programmable through R0x300A. Line_Valid (LV) is HIGH

during the shaded region of Figure 1. Optional embedded

register setup information and histogram statistic

information are available in the first two and the last two

rows of image data.

Figure 1. Spatial Illustration of Image Readout

00 00 00 .................. 00 00 00

00 00 00 .................. 00 00 00

00 00 00 .................. 00 00 00

00 00 00 .................. 00 00 00

00 00 00 .................. 00 00 00

00 00 00 .................. 00 00 00

00 00 00 .................. 00 00 00

00 00 00 .................. 00 00 00

00 00 00 ..................................... 00 00 00

00 00 00 ..................................... 00 00 00

00 00 00 ..................................... 00 00 00

00 00 00 ..................................... 00 00 00

VALID IMAGE

HORIZONTAL

BLANKING

VERTICAL BLANKING

VERTICAL/HORIZONTAL

BLANKING

Pm−1,0 Pm−1,1.....................................Pm−1,n−1 Pm−1,n

Pm,0 Pm,1.....................................Pm,n−1 Pm,n

P0,0 P0,1 P0,2.....................................P0,n−1 P0,n

P1,0 P1,1 P1,2.....................................P1,n−1 P1,n

READOUT SEQUENCE

Typically, the readout window is set to a region including

only active pixels. The user has the option of reading out

dark regions of the array, but if this is done, consideration

must be given to how the sensor reads the dark regions for

its own purposes.

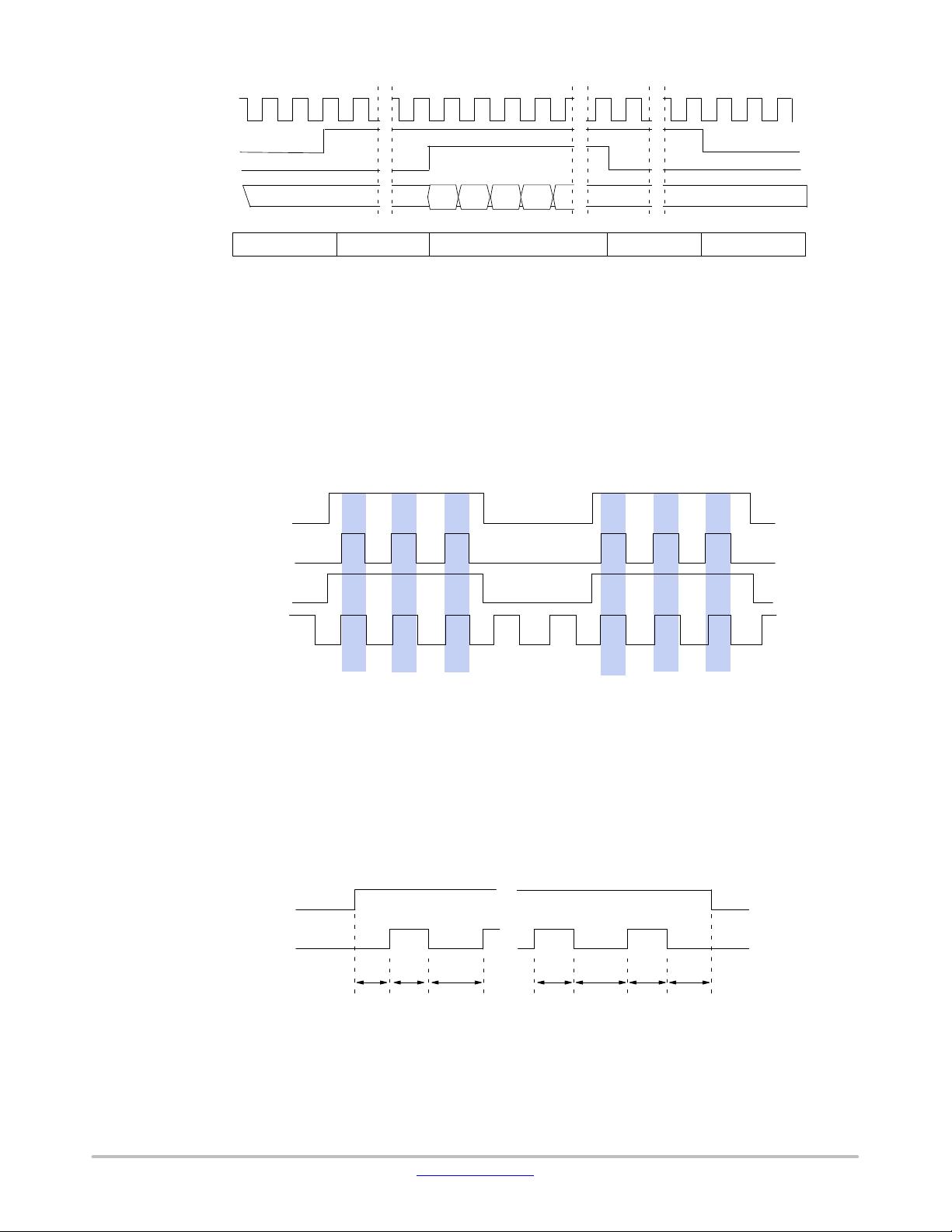

PARALLEL OUTPUT DATA TIMING

The output images are divided into frames, which are

further divided into lines. By default, the sensor produces

800 rows of 1280 columns each. The FV and LV signals

indicate the boundaries between frames and lines,

respectively. PIXCLK can be used as a clock to latch the

data. One 12−bit pixel datum is launched on the DOUT pins

for each falling edge of PIXCLK. The launch edge of

PIXCLK may be set in register R0x3028. When both FV and

LV are asserted, the pixel is valid. PIXCLK cycles that occur

when FV is deasserted are called vertical blanking. PIXCLK

cycles that occur when only LV is deasserted are called

horizontal blanking.

To enable the parallel output pins, set R0x301A[7] = 1,

and set R0x301A[12] = 1 to disable the MIPI serializer. The

parallel input pins (i.e. TRIGGER, STANDBY, etc) may be

enabled by setting R0x301A[8] = 1. Only one output

interface should be enabled at a time.

AND9669

CONFIDENTIAL AND PROPRIETARY

NOT FOR PUBLIC RELEASE

www.onsemi.com

4

PIXCLK

FV

LV

D

OUT[11:0]

Vertical Blanking Horiz Blanking Valid Image Data Horiz Blanking Vertical Blanking

Figure 2. Default Pixel Output Timing

P0

P1 P2 P3

Pn

LV and FV

The timing of the FV and LV outputs is closely related to

the row time and the frame time. FV will be asserted for an

integral number of row times, which will normally be equal

to the height of the output image.

LV will be asserted during the valid pixels of each row.

The leading edge of LV will be offset from the leading edge

of FV by 6 PIXCLKs. Normally, LV will only be asserted if

FV is asserted; this is configurable as described below.

LV Format Options

The default situation (R0x306E[1:0] = 0x0) is for LV to

be de−asserted when FV is de−asserted. By setting

R0x306E[1:0]= 0x1, a continuous LV signal will be output.

The formats for reading out three lines and two vertical

blanking lines are shown in Figure 3.

Figure 3. LV Format Options

Default

Continuous LV

FV

LV

FV

LV

The timing of an entire frame is shown below in Figure 4:

“Line Timing and FRAME_VALID/ LINE_VALID

Signals”. For detailed timing diagrams and switching

parameters, refer to the AR0144AT data sheet.

Frame Time

The pixel clock (PIXCLK) represents the time needed to

sample one pixel from the array. The sensor outputs data at

the maximum rate of one pixel per PIXCLK. One row time

(t

ROW

) is the period from the first pixel output in a row to the

first pixel output in the next row. The row time and frame

time are defined by equations in Table 1.

P1 A Q A Q A P2

Number of master clocks

FRAME_VALID

LINE_VALID

...

...

...

Figure 4. Line Timing and FRAME_VALID/LINE_VALID Signals

AND9669

CONFIDENTIAL AND PROPRIETARY

NOT FOR PUBLIC RELEASE

www.onsemi.com

5

Table 1. FRAME TIME (EXAMPLE BASED ON 1280 X 800, 60 FRAMES PER SECOND)

Parameter Name Equation

Default Timing at 74.25 MHz

(CIT = 2000 rows)

A Active data time Context A: R0x3008 − R0x3004 + 1

Context B: R0x308E − R0x308A + 1

1280 pixel clocks = 17.23 ms

P1 Frame start blanking 6 (fixed)

6 pixel clocks = 0.08 ms

P2 Frame end blanking 6 (fixed)

6 pixel clocks = 0.08 ms

Q Horizontal blanking R0x300C − A

208 pixel clocks = 2.79 ms

A+Q Row Time (t

ROW

) R0x300C

1488 pixel clocks = 20.04 ms

V Vertical blanking

Context A: [(R0x300A+5 − (R0x3006 − R0x3002 + 1)) × (A + Q)]

Context B: [(R0x300A+5 − (R0x3090 − R0x308C + 1)) × (A + Q)]

47616 pixel clocks = 641.29 ms

Nrows × (A

+ Q)

Frame valid time

Context A: ((R0x3006-R0x3002+1) × (A+Q))-Q+P1+P2

Context B: ((R0x3090-R0x308C+1) × (A+Q))-Q+P1+P2

1,190,204 pixel clocks =

16.03 ms

F Total frame time V + (Nrows × (A + Q)) 1,237,820 pixel clocks =

16.67 ms

NOTE: R0x3004 = R0x308A=0

R0x3008 = R0x308E=1279

R0x3002 = R0x308C=0

R0x3006 = R0x3090=799

R0x300A = 827

Sensor timing is shown in terms of pixel clock cycles (see

Figure 2: “Default Pixel Output Timing,” on page 4). The

recommended maximum pixel clock frequency is

74.25 MHz. The vertical blanking and the total frame time

equations assume that the integration time (coarse

integration time) is less than the number of active lines plus

the blanking lines:

Coarse Integration Time t Window Height ) Vertical Blanking

(eq. 1)

If this is not the case, the number of integration lines must

be used instead to determine the frame time, (see Table 2).

In this example, it is assumed that the coarse integration time

control is programmed with 2000 rows and the fine shutter

width total is zero.

For Master mode, if the integration time registers exceed

the total readout time, then the vertical blanking time is

internally extended automatically to adjust for the additional

integration time required. This extended value is not written

back to the frame_length_lines register. The

frame_length_lines register can be used to adjust

frame-to−frame readout time. This register does not affect

the exposure time but it may extend the readout time.

Table 2. FRAME TIME: LONG INTEGRATION TIME

Parameter Name

Equation

(Number of Pixel Clock Cycles)

Default Timing at 74.25 MHz

F’

Total frame time (long integration time)

Context A: (R0x3012 × (A + Q)) + P1 + P2

Context B: (R0x3016 × (A + Q)) + P1 + P2

2,976,012 pixel clocks = 40.08 ms

EXPOSURE

Total integration time is the result of

coarse_integration_time and fine_integration_time

registers plus offset, and depends also on whether manual or

automatic exposure is selected.

Given:

• CIT = R0x3012, Coarse_integration_time (number of

lines of integration)

• FIT = R0x3014 fine_integration_time (number of

pixels of integration)

• LLPCK = R0x300C

• t

clk

= Total Integration Time (unit in clocks)

• T= Total Integration Time (unit in seconds)

The actual total integration time

is defined as:

1. For CIT = 0

t

clk

+ 18 ) FIT

(eq. 2)

Constraint for FIT:

FIT ≤ LLPCK – 550

T + t

clk

ńPixelClkFreq

(eq. 3)

2. CIT > = 0

t

clk

+ T(coarse) ) T(fine)

(eq. 4)

T(coarse) + CIT * LLPCK * 673

(eq. 5)

剩余43页未读,继续阅读

资源评论

Eliot_shao

- 粉丝: 544

- 资源: 16

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功