没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

loginid=jiangkejun@cmdc.chinamobile.com,time=2022-03-17 19:11:18,ip=120.229.34.168,doctitle=MT7981 Application Note-V1.5_20220310.pdf,company=

MT7981B HW Application Note

(Keywords: SCH, PCB, power, thermal, flash)

© 2008 - 2022 MediaTek Technology Corp.

This document contains information that is proprietary to MediaTek Corporation.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly

prohibited.

Specifications are subject to change without notice.

MediaTek Inc. (Jhubei office)

5F, No.5, Tai-Yuen 1st St.

Jhubei City, Hsinchu County 302

Taiwan, ROC

Tel +886-3-560-0868

Fax +886-3-560-0818

http://www.mediatek.com

Document No.: MT7981Application Note

Version: 1.5

Release date: 2022-03-10

Kept by: DCC

Return time: 5 years

loginid=jiangkejun@cmdc.chinamobile.com,time=2022-03-17 19:11:18,ip=120.229.34.168,doctitle=MT7981 Application Note-V1.5_20220310.pdf,company=

MT7981B HW Application Note

Table of Contents

MT7981B MediaTek proprietary and confidential Page 2 of 76

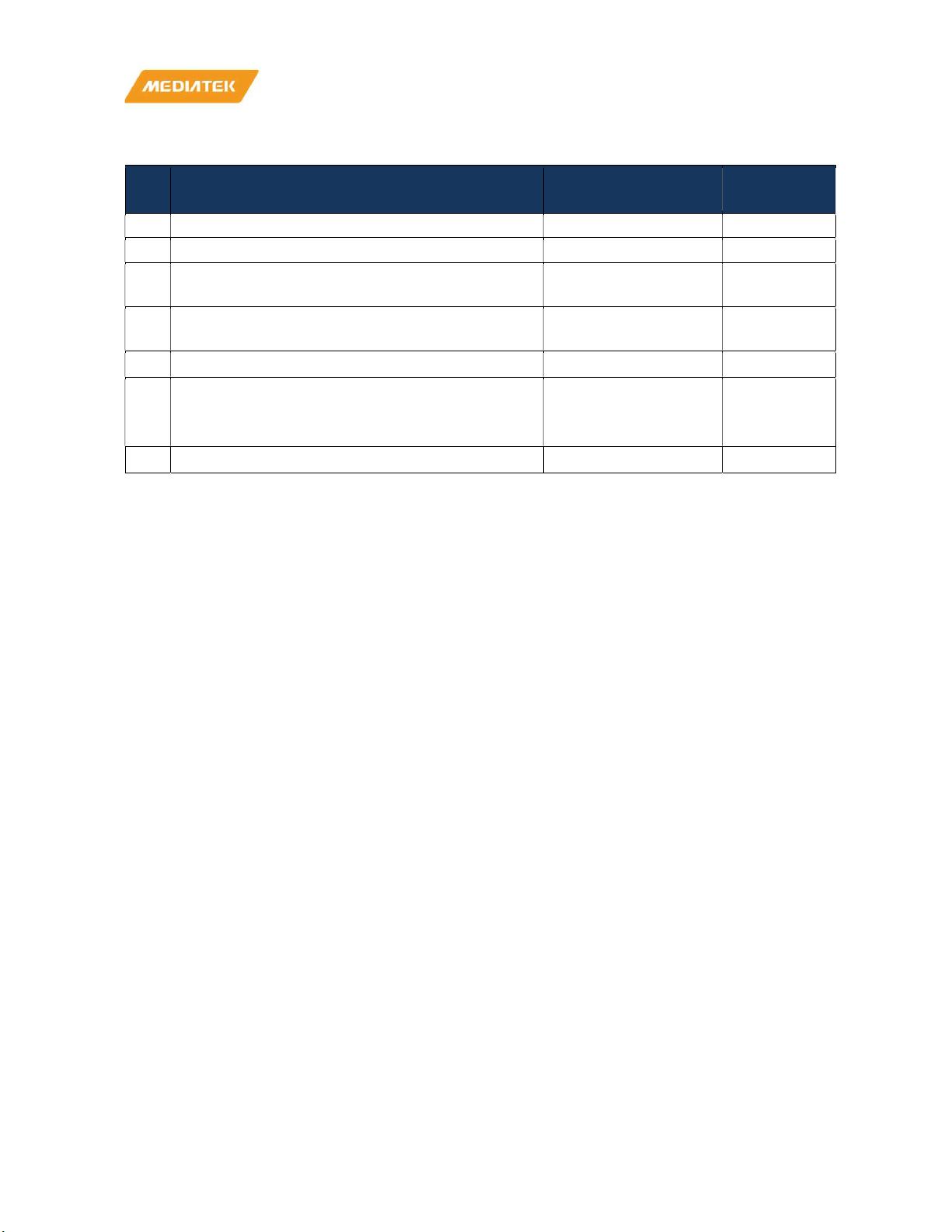

1 Document Revision History

No.

Description Edited

by

Date of

Approval

1.0

Initial Draft

Kim Su

2021/1

1

/

5

1.1

Update

MT7981B

thermal characteris

ti

c

Randy Chou

2021/11/30

1.2

Update section 4.2.4 DDR layout constraint

U

pdate

section 4.2.6

SGMII 0/1 design notice

Randy Chou

2021/12/20

1.3

Update section 4.1 & 4.2 SCH/PCB design

U

pdate section 4.2.4 DDR layout

constraint

Randy Chou

2022/1/19

1

.4

Update section 5. PHY test command Jason Chiang 2022/2/22

1.5

[Remove]p.38 WF0 to WF4, each port’s chip

AIQ out to A die (MT7976) trace length

should be kept the same

(< 1.5mm)

Kim Su

2022/3/10

loginid=jiangkejun@cmdc.chinamobile.com,time=2022-03-17 19:11:18,ip=120.229.34.168,doctitle=MT7981 Application Note-V1.5_20220310.pdf,company=

MT7981B HW Application Note

Table of Contents

MT7981B MediaTek proprietary and confidential Page 3 of 76

Table of Contents

1 Document Revision History .............................................................................................................. 2

List of Tables ......................................................................................................................................... 6

2 Important Notice ................................................................................................................................. 7

3 Product Requirement Document (PRD) ........................................................................................... 8

4 Hardware Design Kit (HDK) ............................................................................................................... 9

4.1 Schematic ................................................................................................................................ 9

4.1.1 16bit DDR3 DRAM .............................................................................................. 9

4.1.2 USB2/3 design .................................................................................................. 10

4.1.3 Power cap list .................................................................................................... 11

4.1.4 MT7981B+MT7976C Power Plan ..................................................................... 14

4.1.5 MT7981B power on sequence .......................................................................... 15

4.1.6 Reset ................................................................................................................. 15

4.1.7 GPIO definition .................................................................................................. 16

4.1.8 Strapping option ................................................................................................ 17

4.1.9 JTAG ................................................................................................................. 18

4.1.10 TSAUX .............................................................................................................. 19

4.1.11 PLL .................................................................................................................... 19

4.1.12 CKSQ ................................................................................................................ 19

4.1.13 AFE Control Signal ............................................................................................ 20

4.1.14 AFE power Cap ................................................................................................. 20

4.1.15 AFE AIQ design guideline ................................................................................. 21

4.1.16 WIFI RX desense by SGMII interference design notice .................................... 22

4.1.17 VQPS ................................................................................................................ 23

4.2 PCB Layout ........................................................................................................................... 24

4.2.1 4L PCB stack-up ............................................................................................... 24

4.2.2 MT7981B RFB ................................................................................................... 24

4.2.3 MT7981B reflow profile ..................................................................................... 25

4.2.4 DDR PCB guidelines ......................................................................................... 26

4.2.5 USB2/3 .............................................................................................................. 27

4.2.6 HSGMII layout noitce ........................................................................................ 28

4.2.7 Ethernet 10/100/1Gbps TX ............................................................................... 30

4.2.8 Buck/LDO design .............................................................................................. 31

4.2.9 WiFi iPAiLNA ..................................................................................................... 36

4.2.10 AIQ trace length control (don’t need to impedance control).............................. 38

4.2.11 AFE WRI trace design guide ............................................................................. 39

4.2.12 PA AVDD33 power De-cap placement. ............................................................ 40

4.2.13 GND connection. ............................................................................................... 41

4.2.14 MT7976 thermal via........................................................................................... 42

4.2.15 MT7976 Xtal trace ............................................................................................. 43

4.2.16 MT7976 Power Trace Routing Rule .................................................................. 44

loginid=jiangkejun@cmdc.chinamobile.com,time=2022-03-17 19:11:18,ip=120.229.34.168,doctitle=MT7981 Application Note-V1.5_20220310.pdf,company=

MT7981B HW Application Note

Table of Contents

MT7981B MediaTek proprietary and confidential Page 4 of 76

4.2.17 MT7976 5G PA Power Trace Routing Rule ...................................................... 45

4.2.18 MT7976 1.8V Power Trace Routing Rule ......................................................... 46

4.2.19 MT7976 Band-gap pin isolate ........................................................................... 47

4.2.20 Shielding frame ................................................................................................. 48

4.2.21 Crystal ............................................................................................................... 48

4.2.22

Co-CLK design .................................................................................................. 49

4.2.23 Flash Interface ................................................................................................... 49

4.3 MT7981B & MT7976 Thermal Characteristics ...................................................................... 51

5 PHY test commands ........................................................................................................................ 52

5.1 MT7531 Ethernet PHY test commands ................................................................................. 52

5.1.1 1000-TX mode command ....................................................................................... 52

5.1.2 100-TX mode command ........................................................................................... 53

5.1.3 10-T mode command ............................................................................................... 53

5.2 USB3 TX compliance test SOP ............................................................................................. 55

5.2.1

U3 TX Compliance Test Item

................................................................................. 55

5.3 USB 2.0 TX compliance test SOP ......................................................................................... 56

5.3.1

USB 2.0 background information

............................................

錯誤

!

尚未定義書籤。

5.3.2

Software programming Enable xHCI USB 2.0 toolkits (Please check Software Engineer)

............................................................................................

錯誤

!

尚未定義書籤。

5.3.3

What parameters to xHCI eye-pattern quality

.........................

錯誤

!

尚未定義書籤。

5.3.4

Eye-pattern parameter

..........................................................

錯誤

!

尚未定義書籤。

5.3.5

USBIF compliance Test

......................................................................................... 57

5.4 SGMII TX electrical and Eye mask test SOP and Command ............................................... 57

5.4.1 Test Item ................................................................................................................... 57

5.4.2 Test Equipment ........................................................................................................ 58

5.4.3 Test Environment Setup ........................................................................................... 58

5.4.4 Test Command ..........................................................................

錯誤

!

尚未定義書籤。

5.4.5 Test Procedure (TX Timing) ..................................................................................... 61

5.4.6 Test Procedure (TX Eye Mask) ................................................................................ 65

5.4.7 TX Electrical Timing Spec ........................................................................................ 68

6 MT7981 Qualified Vendor List (QVL) Table ................................................................................... 72

6.1 Introduction ............................................................................................................................ 72

6.2 Crystal ................................................................................................................................... 72

6.3 Serial NOR Flash memory (3.3V only) .................................................................................. 73

6.4 SFNI Flash (3.3V only) .......................................................................................................... 73

6.5 SPIM-NAND Flash (3.3V only) .............................................................................................. 74

6.6 eMMC Flash Memory (3.3V only) ......................................................................................... 75

7 Disclaimer ......................................................................................................................................... 76

loginid=jiangkejun@cmdc.chinamobile.com,time=2022-03-17 19:11:18,ip=120.229.34.168,doctitle=MT7981 Application Note-V1.5_20220310.pdf,company=

MT7981B HW Application Note

Table of Contents

MT7981B MediaTek proprietary and confidential Page 5 of 76

Table of Figures

FIG 4-1 : THE DRAM REFERENCE REGISTERS .......................................................................................................... 9

FIG 4-2 : THE CAPACITORS OF DRAM VREF .......................................................................................................... 10

FIG 4-3 : USB2_1/USB3 ......................................................................................................................................... 10

FIG 4-4 : U3+HSGMII POWER CAPS....................................................................................................................... 12

FIG 4-5 : DRAM CONTROLLER AND DRAM POWER CAP ....................................................................................... 13

FIG 4-6 : VCCK POWER CAPS ................................................................................................................................. 13

FIG 4-7 : MT7981B + MT7976C POWER PLAN (EXAMPLE).................................................................................... 14

FIG 4-8 : MT7981B POWER ON SEQUENCE .......................................................................................................... 15

FIG 4-9 : RESET CIRCUIT ........................................................................................................................................ 15

FIG 4-10 : MT7981B STRAPPING OPTION ............................................................................................................. 17

FIG 4-11 : MT7981B JTAG ..................................................................................................................................... 18

FIG 4-12 : TXAUS FOR THERMAL SENSOR ............................................................................................................. 19

FIG 4-13 : PLLGP_TP/TN (INTERNAL DEBUG PINS) ............................................................................................... 19

FIG 4-14 : TOP_CLK/HB0/HB0_B SIGNAL DESIGN ................................................................................................. 20

FIG 4-15 : AFE POWER CAP ................................................................................................................................... 20

FIG 4-16 : AIQ DESIGN GUIDELINE ........................................................................................................................ 21

FIG 4-17 : SOLUTION FOR WIFI RX DESENSE BY SGMII INTERFERENCE ................................................................ 22

FIG 4-18 : VQPS PIN SHOULD BE CONNECTED TO GND ........................................................................................ 23

FIG 4-19 : MT7981B RFB TOP VIEW ...................................................................................................................... 24

FIG 4-20 : MT7981B REFLOW PROFILE ................................................................................................................. 25

FIG 4-21 : DDR SOC AND DRAM POWER CAP PLACEMENT .................................................................................. 26

FIG 4-22 : USB3.0/USB2.0 LAYOUT NOTICE .......................................................................................................... 27

FIG 4-23 : MT7981 HSGMII LAYOUT GUIDELINE ................................................................................................... 29

FIG 4-24 : THE SHIELDING LINE EXAMPLE OF ETHERNET LAYOUT ........................................................................ 30

FIG 4-25 : THE POWER DEIGN OF MT7981B. ........................................................................................................ 31

FIG 4-26 : THE VCCK CORE FEEDBACK PIN LAYOUT GUIDELINES. ......................................................................... 32

FIG 4-27 : MT7976 RF TRACE LAYOUT GUIDELINE ................................................................................................ 36

FIG 4-28 : IPA/ILNA RF MATCHING ....................................................................................................................... 37

FIG 4-29 : THE G-BAND/A BAND A DIE AIQ LAYOUT ............................................................................................ 38

FIG 4-30 : WF0 HB0/HB0_B IS CLK KEEP OTHER SIGNAL AWAY .......................................................................... 39

FIG 4-31 : PA AVDD33 POWER DE-CAP PLACEMEN ............................................................................................. 40

FIG 4-32 : GND CONNECTION .............................................................................................................................. 41

FIG 4-33 : THERMAL VIA ...................................................................................................................................... 42

FIG 4-34 : MT7976 XTAL TRACE ........................................................................................................................... 43

FIG 4-35 : MT7976 POWER TRACE ROUTING RULE ............................................................................................. 44

FIG 4-36 : MT7976 5G PA POWER TRACE ROUTING RULE .................................................................................... 45

FIG 4-37 : MT7976 1.8V POWER TRACE ROUTING RULE ...................................................................................... 46

FIG 4-38 : MT7976 BAND-GAP PIN ISOLATE ........................................................................................................ 47

FIG 4-39 : SHIELDING FRAME ............................................................................................................................... 48

FIG 4-40 : CRYSTAL LAYOUT GUIDELINES ............................................................................................................. 48

FIG 4-41 : OSC GUIDELINES ................................................................................................................................... 49

FIG 4-42 : SPI FLASH LAYOUT GUIDELINES............................................................................................................ 49

FIG 4-43 : EMMC NAND SCH/PCB DEIGN.............................................................................................................. 50

FIG 5-1 : SGMII TX ELECTRICAL TEST ENVIRONMENT SETUP DIAGRAM ............................................................... 58

剩余75页未读,继续阅读

资源评论

CookieAndCat

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功