没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

SH1106

132 X 64 Dot Matrix OLED/PLED

Preliminary Segment/Common Driver with Controller

1 V0.2

Features

Support maximum 132 X 64 dot matrix panel

Embedded 132 X 64 bits SRAM

Operating voltage:

- Logic voltage supply: V

DD1 = 1.65V - 3.5V

- DC-DC voltage supply: V

DD2 = 3.0V – 4.2V

- OLED Operating voltage supply:

External V

PP supply = 6.4V - 13.0V

Internal V

PP generator = 6.4V - 9.0V

Maximum segment output current: 200μA

Maximum common sink current: 27mA

8-bit 6800-series parallel interface, 8-bit 8080-series

parallel interface, 3-wire & 4-wire serial peripheral

interface, 400KHz fast I

2

C bus interface

Programmable frame frequency and multiplexing ratio

Row re-mapping and column re-mapping (ADC)

Vertical scrolling

On-chip oscillator

Programmable Internal charge pump circuit output

256-step contrast control on monochrome passive OLED

panel

Low power consumption

- Sleep mode: <5μA

- VDD1=0V,VDD2=3.0V – 4.2V: <5μA

- VDD1,2=0V,VPP=3.0V – 4.2V: <5μA

Wide range of operating temperatures: -40 to +85°C

Available in COG form, thickness: 300μm

General Description

SH1106 is a single-chip CMOS OLED/PLED driver with controller for organic/polymer light emitting diode dot-matrix graphic

display system. SH1106 consists of 132 segments, 64 commons that can support a maximum display resolution of 132 X 64. It

is designed for Common Cathode type OLED panel.

SH1106 embeds with contrast control, display RAM oscillator and efficient DC-DC converter, which reduces the number of

external components and power consumption. SH1106 is suitable for a wide range of compact portable applications, such as

sub-display of mobile phone, calculator and MP3 player, etc.

SH1106

2 V0.2

Block Diagram

Display data latch

132 X 64-dots

Display Data RAM

line address decoder

I/O buffer circuit

Output status

selector circuit

Column address decoder

8-bit column address counter

8-bit column address counter

Page Address

Register

Display Timing

Generator Circuit

CL

Line counter

Initial display line register

VBREF

Segment driver Common driver

Shift register

Power supply

circuit

IREF

VCOMH

VCL

VSL

VDD1

VSS

SEG0 SEG131 COM0 COM63

VDD2

Bus Holder Command Decoder Bus Holder Oscillator

I/O Buffer

CLS

(SI/SDA) (SCL)

D7 D6 D5 D4 D3 D2 D1 D0

Microprocessor Interface

RES

IM2

(R/W)

(E)

IM1

WRRDA0CS

(SA0)

Charge Pump

C1N

VPP

C1P

C2N

C2P

IM0

SH1106

3 V0.2

Pad Description

Power Supply

Symbol I/O Description

VDD1 Supply Power supply input: 1.65 - 3.5V

VDD2 Supply

3.0 – 4.2V power supply pad for Power supply for charge pump circuit.

This pin can be disconnected or connect to V

DD1 when VPP is supplied externally

VSS Supply Ground.

VSL Supply

This is a segment voltage reference pad.

This pad should be connected to V

SS externally.

VCL Supply

This is a common voltage reference pad.

This pad should be connected to V

SS externally.

OLED Driver Supplies

Symbol I/O Description

IREF O

This is a segment current reference pad. A resistor should be connected between this pad and

V

SS. Set the current at 10μA.

VCOMH O

This is a pad for the voltage output high level for common signals.

A capacitor should be connected between this pad and V

SS.

VBREF NC

This is an internal voltage reference pad for booster circuit.

Keep floating.

VPP P

OLED panel power supply. Generated by internal charge pump.

Connect to capacitor. It could be supplied externally.

C1N,

C1P

P

Connect to charge pump capacitor.

These pins are not used and should be disconnedted when Vpp is supplied externally.

C2P,

C2N

P

Connect to charge pump capacitor.

These pins are not used and should be disconnedted when Vpp is supplied externally.

SH1106

4 V0.2

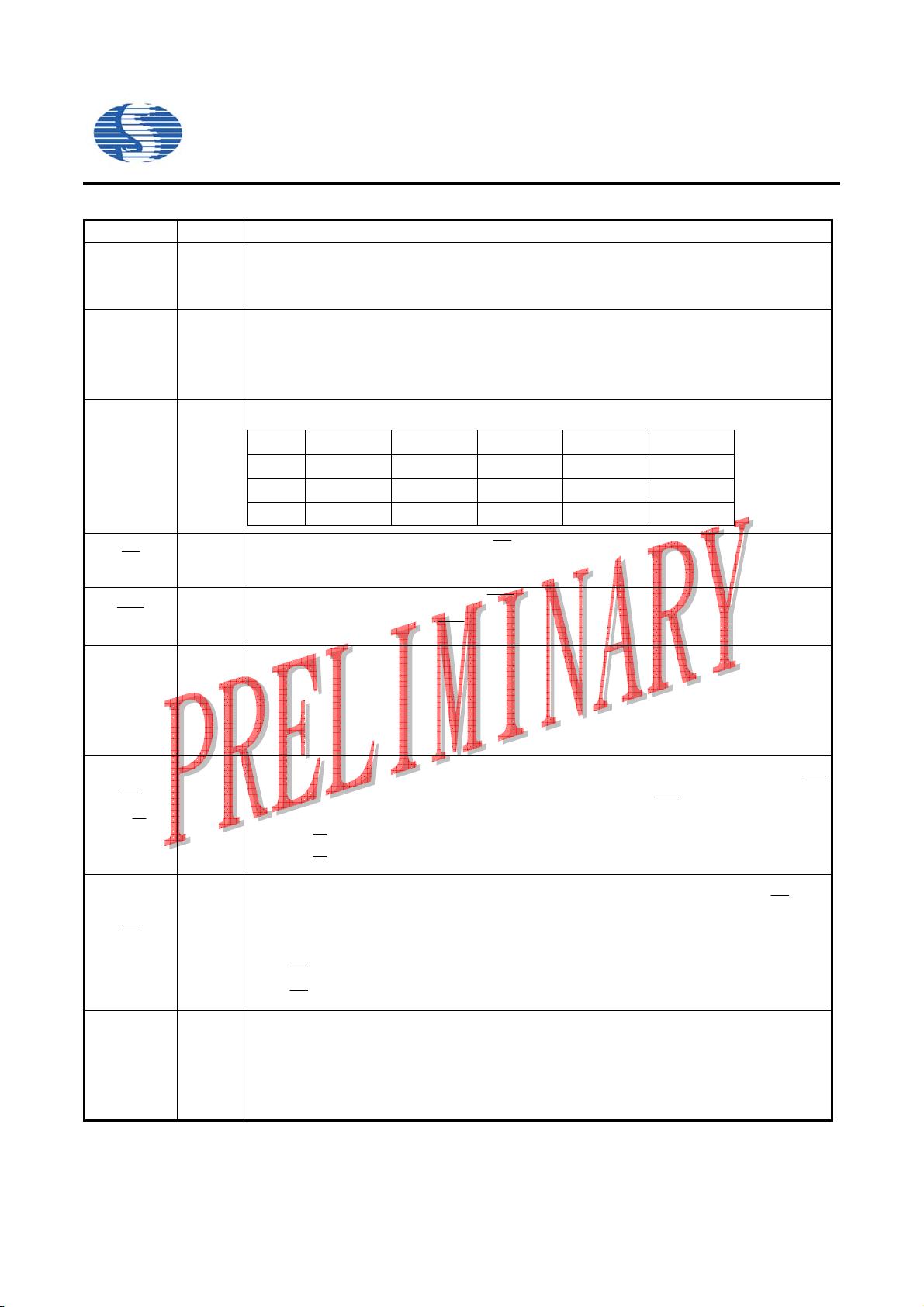

System Bus Connection Pads

Symbol I/O Description

CL I/O

This pad is the system clock input. When internal clock is enabled, this pad should be

Left open. The internal clock is output from this pad. When internal oscillator is disabled, this pad

receives display clock signal from external clock source.

CLS I

This is the internal clock enable pad.

CLS = “H”: Internal oscillator circuit is enabled.

CLS = “L”: Internal oscillator circuit is disabled (requires external input).

When CLS = “L”, an external clock source must be connected to the CL pad for normal operation.

IM0

IM1

IM2

I

These are the MPU interface mode select pads.

8080 I

2

C 6800 4-wire SPI 3-wire SPI

IM0 0 0 0 0 1

IM1 1 1 0 0 0

IM2 1 0 1 0 0

CS

I

This pad is the chip select input. When

CS = “L”, then the chip select becomes active,

and data/command I/O is enabled.

RES

I

This is a reset signal input pad. When

RES is set to “L”, the settings are initialized. The reset

operation is performed by the

RES signal level.

A0 I

This is the Data/Command control pad that determines whether the data bits are data or a

command.

A0 = “H”: the inputs at D0 to D7 are treated as display data.

A0 = “L”: the inputs at D0 to D7 are transferred to the command registers.

In I

2

C interface, this pad serves as SA0 to distinguish the different address of OLED driver.

WR

(

WR / )

I

This is a MPU interface input pad.

When connected to an 8080 MPU, this is active LOW. This pad connects to the 8080 MPU

WR

signal. The signals on the data bus are latched at the rising edge of the

WR signal.

When connected to a 6800 Series MPU: This is the read/write control signal input terminal.

When

WR / = “H”: Read.

When

WR / = “L”: Write.

RD

(E)

I

This is a MPU interface input pad.

When connected to an 8080 series MPU, it is active LOW. This pad is connected to the

RD

signal

of the 8080 series MPU, and the data bus is in an output status when this signal is “L”.

When connected to a 6800 series MPU , this is active HIGH. This is used as an enable clock

input of the 6800 series MPU.

When

RD

= “H”: Enable.

When

RD

= “L”: Disable.

D0 - D7

(SCL)

(SI/SDA)

I/O

I

I/O

This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus.

When the serial interface is selected, then D0 serves as the serial clock input pad (SCL) and D1

serves as the serial data input pad (SI). At this time, D2 to D7 are set to high impedance.

When the I

2

C interface is selected, then D0 serves as the serial clock input pad (SCL) and D1

serves as the serial data input pad (SDAI). At this time, D2 to D7 are set to high impedance.

SH1106

5 V0.2

OLED Drive Pads

Symbol I/O Description

COM0,2,

- 60, 62

O These pads are even Common signal output for OLED display.

COM1,3

- 61,63

O These pads are odd Common signal output for OLED display.

SEG0 - 131 O These pads are Segment signal output for OLED display.

Test Pads

Symbol I/O Description

TEST1-3 I Test pad, internal pull low, no connection for user.

Dummy - These pads are not used. Keep floating.

剩余48页未读,继续阅读

资源评论

guibaodear2023-09-19中文在哪里?

guibaodear2023-09-19中文在哪里?

派大唾沫星子~

- 粉丝: 1

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功