CYIV-52001-3.3

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

Cyclone IV 器件手册,

卷2

2011 年 11 月

Subscribe

ISO

9001:2008

Registered

1. Cyclone IV 收发器体系结构

在低成本的 FPGA 中,Cyclone

®

IV GX 器件内嵌多达八个全双工收发器,运行在 600

Mbps 到 3.125 Gbps 的串行数据速率上。表1-1列出了 Cyclone IV GX 收发器通道所

支持的串行协议信息。

您可以通过 ALTGX MegaWizard ™ Plug-In Manager 来实现这些协议。此外,ALTGX

MegaWizard ™ Plug-In Manager 也提供了高度灵活的 Basic 功能代码,以实现支持下面

串行数据速率的专用串行协议

:

■ 600 Mbps 到 2.5 Gbps,适用于 F324 以及更小封装中的器件

■ 600 Mbps 到 3.125 Gbps,适用于 F484 以及更大封装中的器件

欲了解关于使用 ALTGX 宏功能对收发器进行例化时的可用端口的详细说明信息,请参

考第 1-85 页中的 “ 收发器顶层端口列表 ”。

f 欲了解关于运行在 ≥2.97 Gbps 数据速率下的 Cyclone IV 收发器的详细信息,请参考

Cyclone IV Device Family Pin Connection Guidelines

。

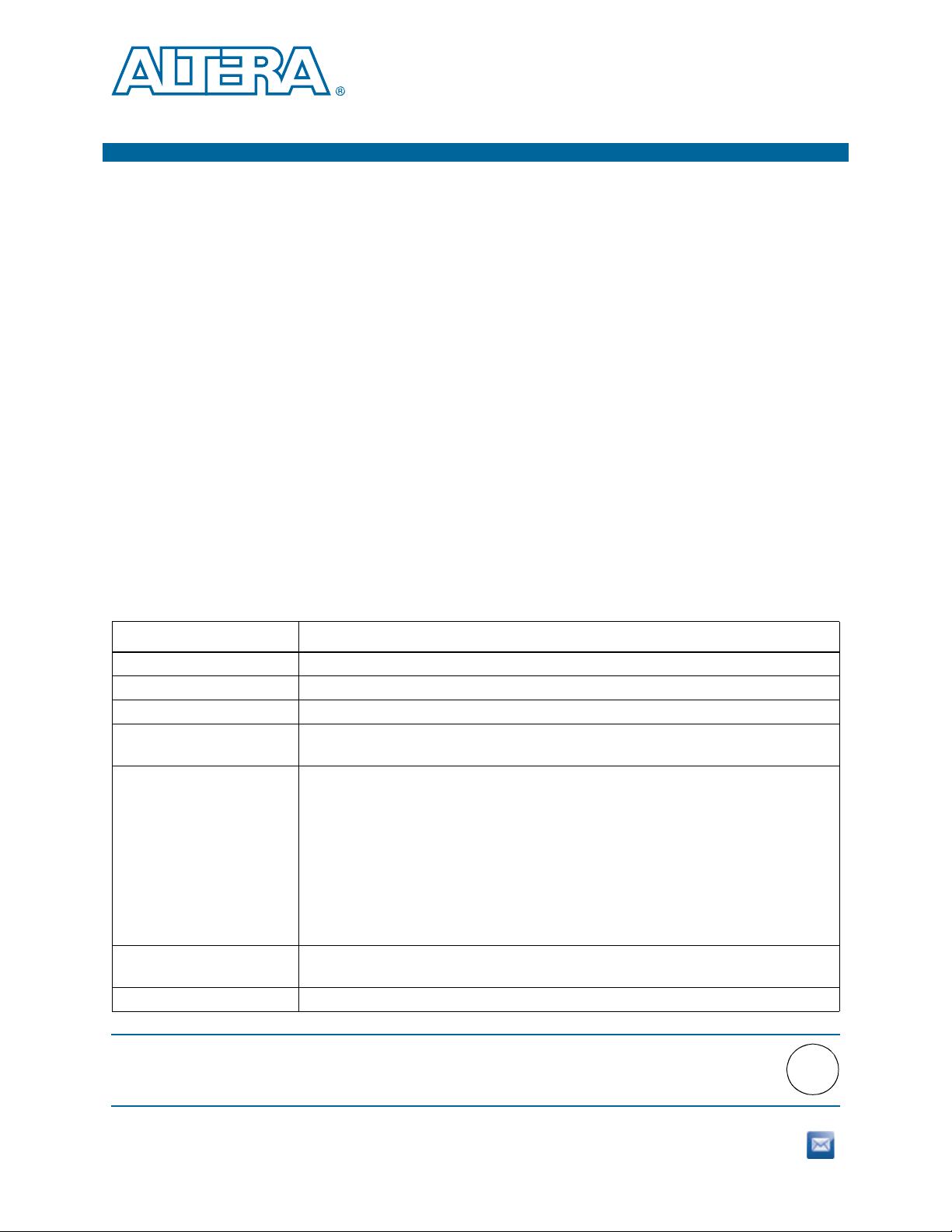

表 1-1. Cyclone IV GX 收发器通道所支持的串行协议 — 初步

协议 数据速率 (Gbps)

F324 以及更小

的器件封装

F484 以及更大

的器件封装

PCI Express

®

(PCIe

®

)

(1)

2.5

vv

千兆以太网 (GbE)

1.25

vv

通用公共无线接口 (CPRI)

0.6144、1.2288、 2.4576 和

3.072

v

(2)

v

OBSAI

0.768、1.536 和 3.072 v

(2)

v

XAUI

3.125 —

v

串行数字接口 (SDI)

HD-SDI 支持 1.485 和 1.4835

3G-SDI 支持 2.97 和 2.967

—

v

Serial RapidIO

®

(SRIO)

1.25、2.5 和 3.125 —

v

串行高级技术附件 (SATA)

(3)

1.5 和 3.0 —

v

V-by-one

(3)

3.0 —

v

显示端口

(3)

1.62 和 2.7 —

v

表1-1注释:

(1) 提供了兼容 PIPE(PCI Express 物理接口 ) 的接口,支持 Gen1 ×1、×2 和 ×4 初始通道宽度配置。当实现 ×1 或 ×2 接口时,

收发器模块中的其它通道可用于实现其它协议。

(2) 仅支持高达 2.5 Gbps 的数据速率。

(3) 协议规范的兼容性还是一个待定属性。

November 2011

CYIV-52001-3.3