没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Fast Fourier

Transform v9.0

LogiCORE IP Product Guide

Vivado Design Suite

PG109 October 4, 2017

Fast Fourier Transform v9.0 www.xilinx.com 2

PG109 October 4, 2017

Table of Contents

IP Facts

Chapter 1: Overview

Licensing and Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Chapter 2: Product Specification

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 3: Designing with the Core

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Event Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

AXI4-Stream Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

System Generator for DSP Graphical User Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Chapter 5: C Model

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Unpacking and Model Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Software Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

FFT C Model Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

C Model Example Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Compiling with the FFT C Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

FFT MATLAB Software MEX Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Send Feedback

Fast Fourier Transform v9.0 www.xilinx.com 3

PG109 October 4, 2017

MEX Function Example Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Modeling Multichannel FFTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Dependent Libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Chapter 6: Test Bench

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Appendix A: Migrating and Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

AXI4-Stream Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Appendix C: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Documentation Navigator and Design Hubs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Send Feedback

Fast Fourier Transform v9.0 www.xilinx.com 4

PG109 October 4, 2017 Product Specification

Introduction

The Xilinx® LogiCORE™ IP Fast Fourier

Transform (FFT) core implements the

Cooley-Tukey FFT algorithm, a computationally

efficient method for calculating the Discrete

Fourier Transform (DFT).

Features

• Forward and inverse complex FFT, run time

configurable

• Transform sizes N = 2

m

, m = 3 – 16

• Data sample precision b

x

= 8 – 34

• Phase factor precision b

w

= 8 – 34

• Arithmetic types:

°

Unscaled (full-precision) fixed-point

°

Scaled fixed-point

°

Block floating-point

• Fixed-point or floating-point interface

• Rounding or truncation after the butterfly

• Block RAM or Distributed RAM for data and

phase-factor storage

• Optional run time configurable transform

point size

• Run time configurable scaling schedule for

scaled fixed-point cores

• Bit/digit reversed or natural output order

• Optional cyclic prefix insertion for digital

communications systems

• Four architectures offer a trade-off between

core size and transform time

• Bit accurate C model and MEX function for

system modeling available for download

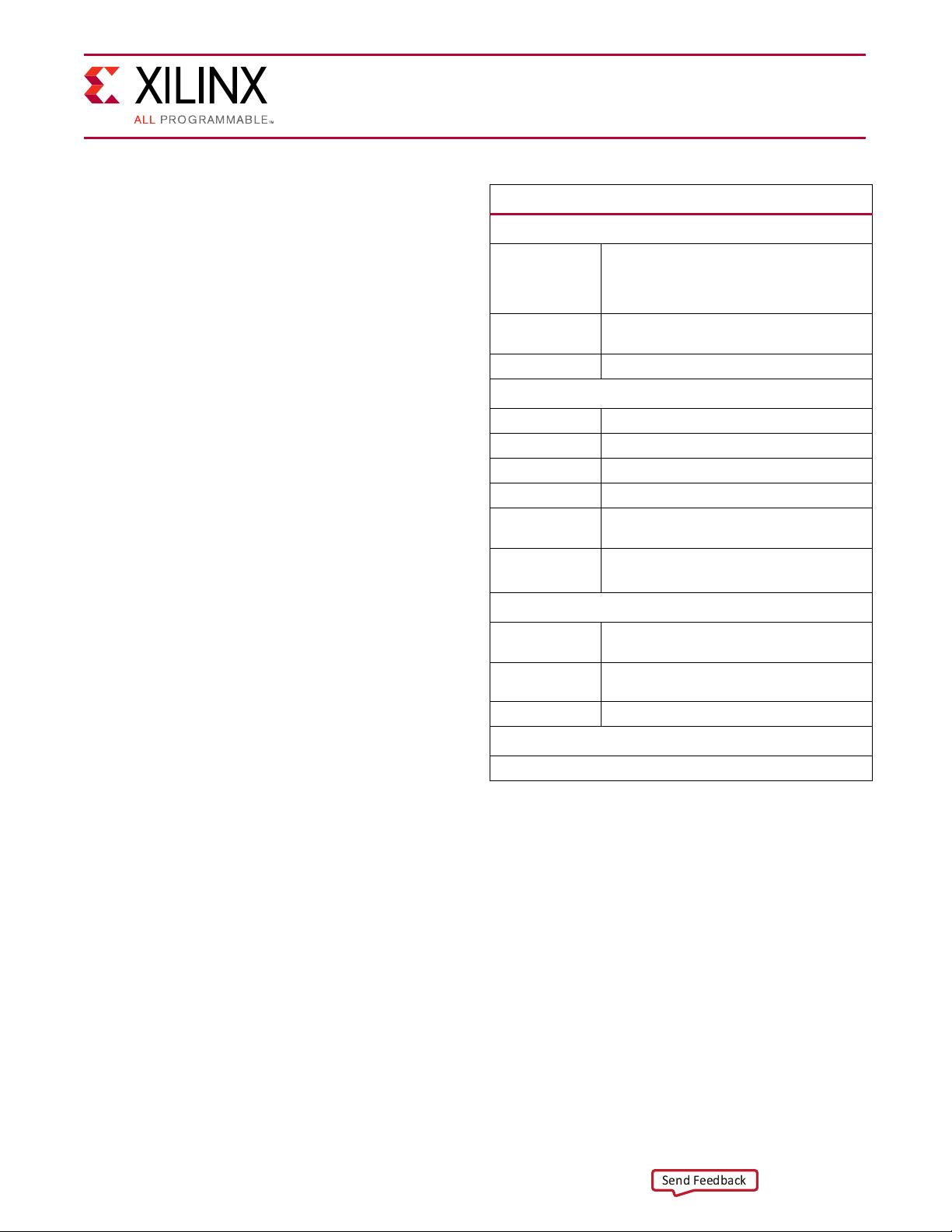

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

UltraScale+™ Families

UltraScale™ Architecture

Zynq®-7000 All Programmable SoC

7 Series

Supported User

Interfaces

AXI4-Stream

Resources Performance and Resource Utilization web page

Provided with Core

Design Files Encrypted RTL

Example Design Not Provided

Test Bench VHDL

Constraints File Not Provided

Simulation

Model

Encrypted VHDL

C Model

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry

Vivado® Design Suite

System Generator for DSP

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete listing of supported devices, see the Vivado IP

catalog.

2. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

Send Feedback

Fast Fourier Transform v9.0 www.xilinx.com 5

PG109 October 4, 2017

Chapter 1

Overview

The FFT core computes an N-point forward DFT or inverse DFT (IDFT) where N can be 2

m

,

m = 3–16.

For fixed-point inputs, the input data is a vector of N complex values represented as dual

b

x

-bit twos-complement numbers, that is, b

x

bits for each of the real and imaginary

components of the data sample, where b

x

is in the range 8 to 34 bits inclusive. Similarly, the

phase factors b

w

can be 8 to 34 bits wide.

For single-precision floating-point inputs, the input data is a vector of N complex values

represented as dual 32-bit floating-point numbers with the phase factors represented as

24- or 25-bit fixed-point numbers.

All memory is on-chip using either block RAM or distributed RAM. The N element output

vector is represented using b

y

bits for each of the real and imaginary components of the

output data. Input data is presented in natural order and the output data can be in either

natural or bit/digit reversed order. The complex nature of data input and output is intrinsic

to the FFT algorithm, not the implementation.

Three arithmetic options are available for computing the FFT:

• Full-precision unscaled arithmetic

• Scaled fixed-point, where you provide the scaling schedule

• Block floating-point (run time adjusted scaling)

The point size N, the choice of forward or inverse transform, the scaling schedule and the

cyclic prefix length are run time configurable. Transform type (forward or inverse), scaling

schedule and cyclic prefix length can be changed on a frame-by-frame basis. Changing the

point size resets the core.

Four architecture options are available: Pipelined Streaming I/O, Radix-4 Burst I/O, Radix-2

Burst I/O, and Radix-2 Lite Burst I/O. For detailed information about each architecture, see

Architecture Options.

Send Feedback

剩余98页未读,继续阅读

资源评论

prisoner123

- 粉丝: 2

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功