I

2

C-Master Core

Specification

Author: Richard Herveille

rherveille@opencores.org

Rev. 0.7

June 26, 2002

This page has been intentionally left blank

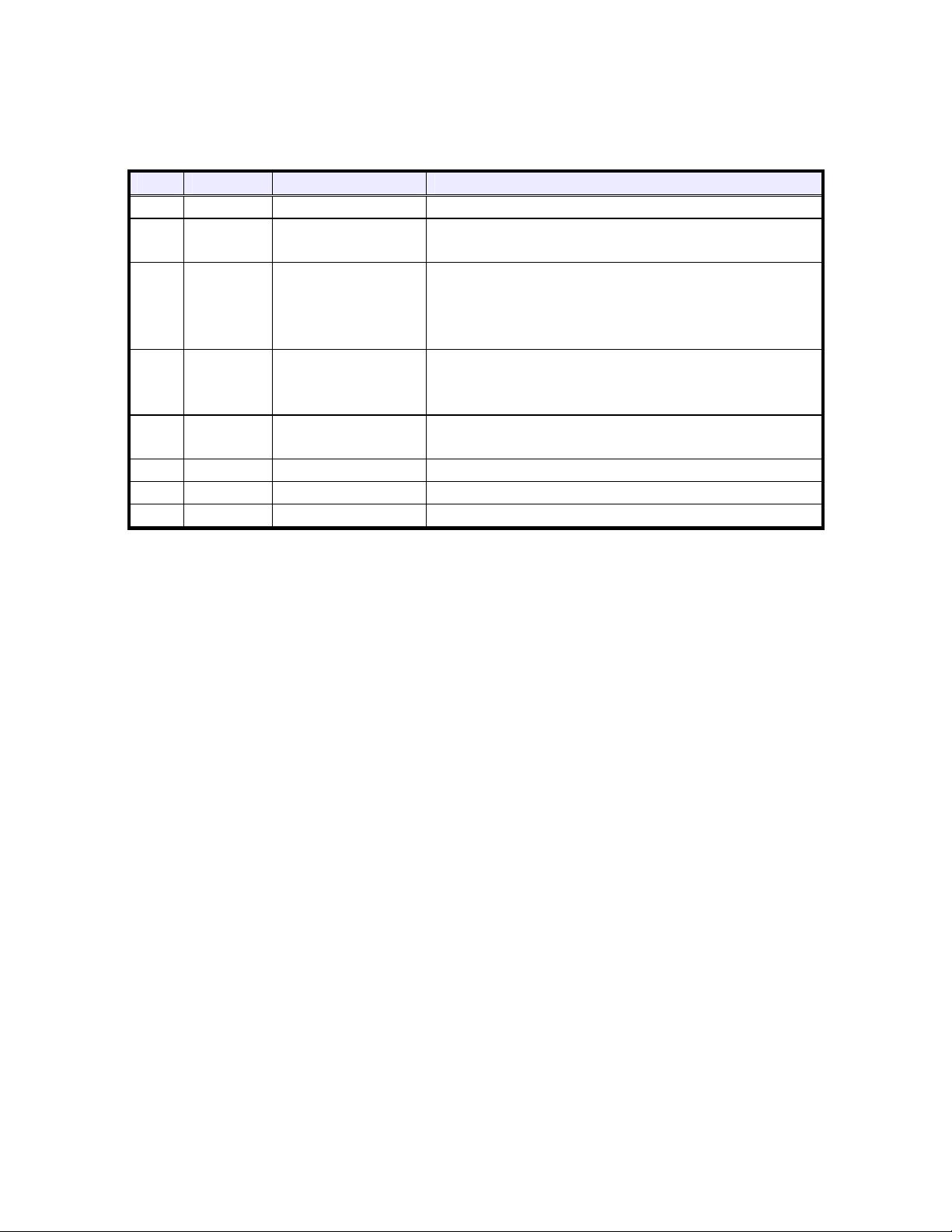

Revision History

Rev. Date Author Description

0.1 17/02/01 Richard Herveille First draft release

0.2 01/03/01 Richard Herveille Some cleaning up throughout the document

Added ‘Programming Examples’ section

0.3 Richard Herveille Added some comments after core-changes

- added BUSY bit (status register)

- changed I2C IO for ASIC support

- added comment for FGPA IO

0.4 10/19/01 Richard Herveille Changed core’s databus size to 8bit.

Changed documentation to reflect changes.

Changed port names to new naming convention.

0.5 18/02/02 Richard Herveille Changed table headers.

Added OpenCores logo.

0.5a 05/02/02 Richard Herveille Reviewed entire document.

0.6 21/03/02 Richard Herveille Added Appendix A, Synthesis Results

0.7 25/06/02 Richard Herveille Changed Prescale Register formula

OpenCores I

2

C-Master core 6/26/2002

www.opencores.org Rev 0.7 Preliminary 1 of 15

1

Introduction

I2C is a two-wire, bi-directional serial bus that provides a simple and efficient method of

data exchange between devices. It is most suitable for applications requiring occasional

communication over a short distance between many devices.

The interface defines 3 transmission speeds:

- normal: 100Kbps

- fast: 400Kbps

- high speed: 3.5Mbps

Only 100Kbps and 400Kbps modes are supported directly.

The I2C standard is a true multi-master bus including collision detection and arbitration

that prevents data corruption if two or more masters attempt to control the bus

simultaneously. This core, however, supports only single master operations, in which the

core is the master.

FEATURES

• Software programmable clock frequency

• Software programmable acknowledge bit

• Interrupt driven data-transfers

• Start/Stop/Repeated Start/Acknowledge generation

• Supports Clock Stretching/Wait state generation

• Single Master Operation

• Operates from a wide range of input clock frequencies

• Static synchronous design

• Fully synthesizable

OpenCores I

2

C-Master core 6/26/2002

www.opencores.org Rev 0.7 Preliminary 2 of 15

2

IO ports

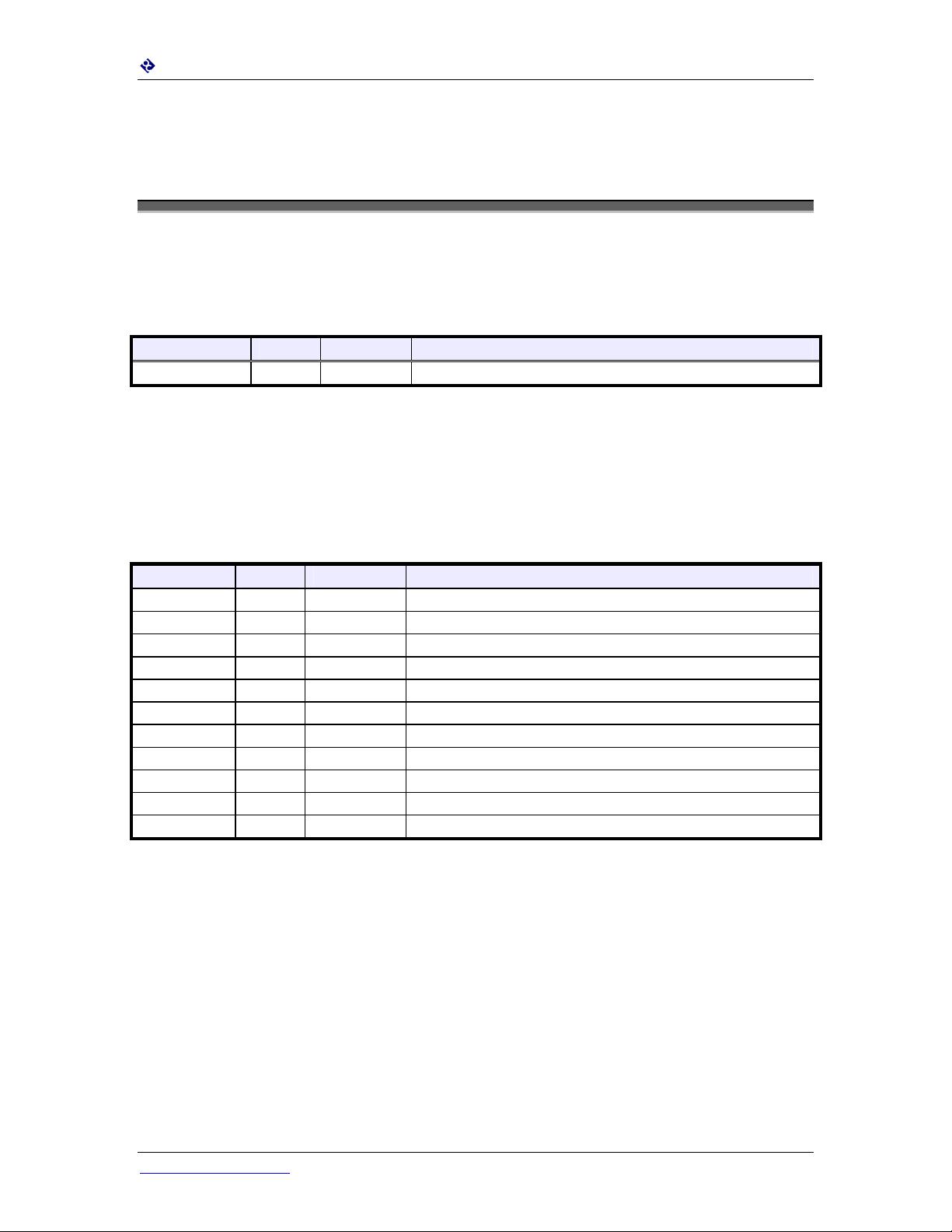

2.1 Core Parameters

Parameter Type Default Description

ARST_LVL Bit 1’b0 Asynchronous reset level

2.1.1 ARST_LVL

The asynchronous reset level can be set to either active high (1’b1) or active low (1’b0).

2.2 WISHBONE interface signals

Port Width Direction Description

wb_clk_i 1 Input Master clock

wb_rst_i 1 Input Synchronous reset, active high

arst_i 1 Input Asynchronous reset

wb_adr_i 3 Input Lower address bits

wb_dat_i 8 Input Data towards the core

wb_dat_o 8 Output Data from the core

wb_we_i 1 Input Write enable input

wb_stb_i 1 Input Strobe signal/Core select input

wb_cyc_i 1 Input Valid bus cycle input

wb_ack_o 1 Output Bus cycle acknowledge output

wb_inta_o 1 Output Interrupt signal output

arst_i is not a WISHBONE compatible signal. It is provided for FPGA implementations.

Using [arst_i] instead of [wb_rst_i] can result in lower cell-usage and higher

performance, because most FPGAs provide a dedicated asynchronous reset path. Use

either [arst_i] or [wb_rst_i].

- 1

- 2

前往页