没有合适的资源?快使用搜索试试~ 我知道了~

AT91RM9200中文手册(修正版)

需积分: 9 16 下载量 201 浏览量

2012-04-02

16:58:38

上传

评论

收藏 4.58MB PDF 举报

温馨提示

试读

638页

AT91RM9200中文手册(修正版) AT91RM9200中文手册(修正版)AT91RM9200中文手册(修正版)AT91RM9200中文手册(修正版)

资源推荐

资源详情

资源评论

1

特性

• 融合了 ARM920T

™

ARM

®

Thumb

®

处理器

– 工作于 180 MHz 时性能高达 200 MIPS,存储器管理单元

– 16-K 字节的数据缓存, 16-K 字节的指令缓存,写缓冲器

– 含有调试信道的内部仿真器

– 中等规模的嵌入式宏单元结构 ( 仅针对 256 BGA 封装 )

• 低功耗:VDDCORE 电流为 30.4 mA 待机模式电流为 3.1 mA

• 附加的嵌入式存储器

–SRAM为 16K ; ROM 为 128K

• 外部总线接口 (EBI)

– 支持 SDRAM,静态存储器, Burst Flash,无缝连接的 CompactFlash

®

,

SmartMedia

™

及 NAND Flash

• 提高性能而使用的系统外设:

– 增强的时钟发生器与电源管理控制器

– 两个有双 PLL 的片上振荡器

– 低速的时钟操作模式与软件功耗优化能力

– 四个可编程的外部时钟信号

– 包括周期性中断、看门狗及第二计数器的系统定时器

– 有报警中断的实时时钟

– 调试单元、两线 UART 并支持调试信道

– 有 8 个优先级的高级中断控制器,独立的可屏蔽中断源,伪中断保护

– 7 个外部中断源及 1 个快速中断源

– 有 122 个可编程 I/O 口线的四个 32 位 PIO 控制器,各线均有输入变化中断及开漏能力

–20通道的外设数据控制器 (DMA)

• 10/100 Base-T 型以太网卡接口

– 独立的媒体接口 (MII) 或简化的独立媒体接口 (RMII)

– 对于接收与发送有集成的 28 字节 FIFO 及专用的 DMA 通道

• USB 2.0 全速 (12 M 比特 / 秒 ) 主机双端口

– 双片上收发器 (208 引脚 PQFP 封装中仅为一个 )

– 集成的 FIFO 及专用的 DMA 通道

• USB 2.0 全速 (12 M 比特 / 秒 ) 器件端口

– 片上收发器, 2-K 字节可配置的集成 FIFO

• 多媒体卡接口 (MCI)

– 自动协议控制及快速自动数据传输

– 与 MMC 及 SD 存储器卡兼容,支持两个 SD 存储器

• 3 个同步串行控制器 (SSC)

– 每个接收器与发送器有独立的时钟及帧同步信号

– 支持 I

2

S 模拟接口,时分复用

–32比特的高速数据流传输能力

• 4 个通用同步 / 异步接收 / 发送器 (USART)

– 支持 ISO7816 T0/T1 智能卡

– 硬软件握手

– 支持 RS485 及高达 115 Kbps 的 IrDA 总线

–USART1为全调制解调控制线

• 主机 / 从机串行外设接口 (SPI)

–8~ 16 位可编程数据长度,可连接 4 个外设

• 两个 3 通道 16 位定时 / 计数器 (TC)

– 3 个外部时钟输入,每条通道有 2 个多功能 I/O 引脚

– 双 PWM 产生器,捕获 / 波形模式,上加 / 下减计数能力

• 两线接口 (TWI)

– 主机模式支持,所有两线 Atmel EEPROM 支持

• 所有数字引脚的 IEEE 1149.1 JTAG 边界扫描

• 电源供应

– VDDCORE, VDDOSC 及 VDDPLL 电压为:1.65V ~ 1.95V

–VDDIOP (外设 I/O) 及 VDDIOM ( 存储器 I/O) 电压为:1.65V ~ 3.6V

• 提供了 208 引脚 PQFP 及 256 球状 BGA 两种封装

基于 ARM920T

™

的微控制器

AT91RM9200

本文是英文数据手册的中文翻

译,其目的是方 便中国用户的

阅读。它无法自动跟随原稿的

更新,同 时也可能存在翻译上

的错误。读者应该以英文原稿

为参考以获得更准确的信息。

Rev. 1768B-ATARM–07-Jun-05

采用5级流水线和超

标量计算(预测和乱

序等),使MIPS超过

了时钟频率

既可以做USB主

机、也可以做USB

设备

应该是硬件握手,

都有RTS/CTS

2

AT91RM9200

1768B–ATARM–07-Jun-05

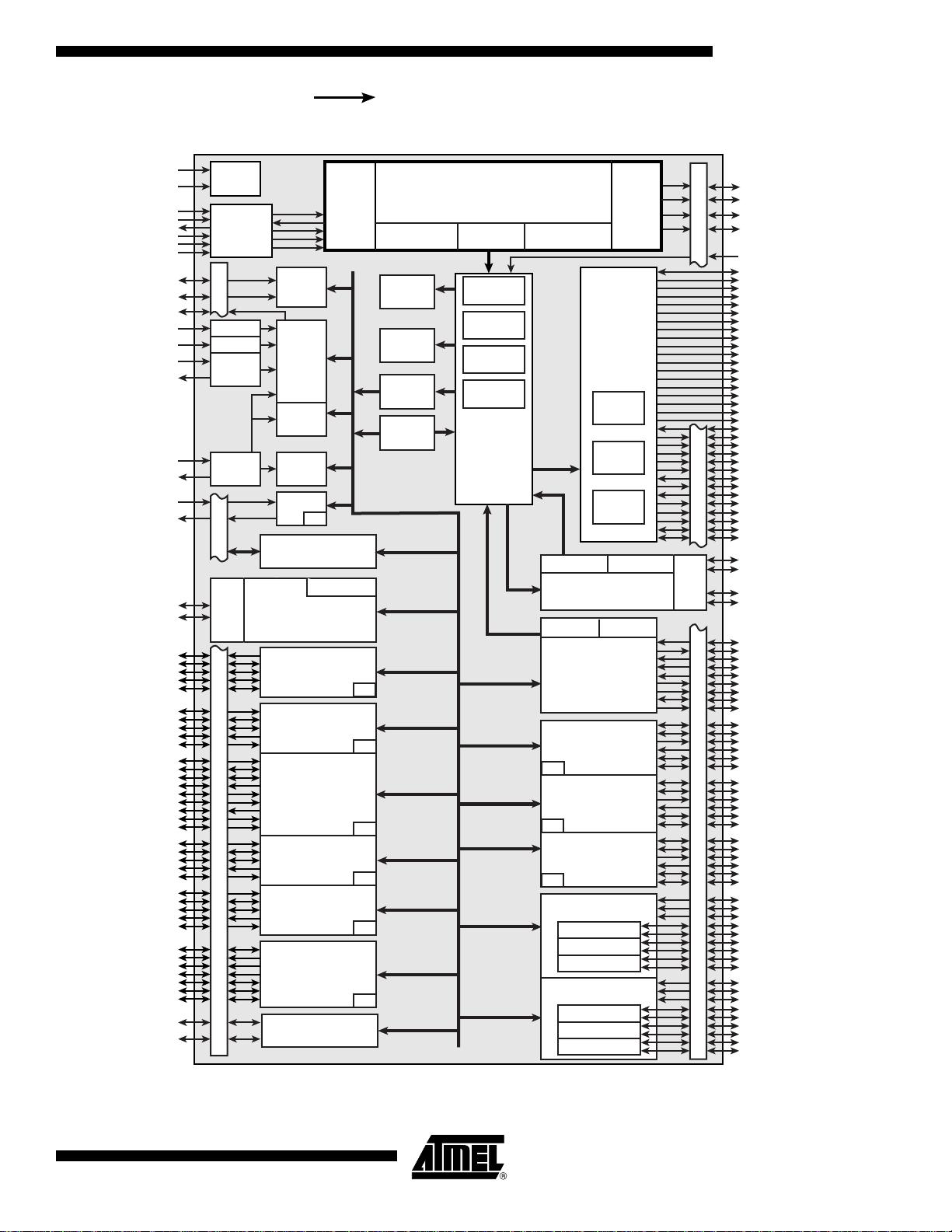

说明 AT91RM9200是完全围绕ARM920T ARM Thumb处理器构建的系统。它 有丰富的系统与应用外

设及标准的接口,从而为低功耗、低成本、高性能的计算机宽范围应用提供一个单片解决方案。

AT91RM9200包括一个高速片上SRAM工作区及一个低等待时间的外部总线接口(EBI),以 完成

应用所要求的片外存储器和 内部存储器映射外设配置的无缝连接。 EBI 有同步 DRAM

(SDRAM)、 Burst Flash 及静态存储器的控制器,并设 计了专用电路以方便与 SmartMedia、

CompactFlash 及 NAND Flash 连接。

高级中断控制器 (AIC) 通过多向量 ,中断源优先级划分及缩短中断处理传输时间来提高

ARM920T 处理器的中断处理性能。

外设数据控制器 (PDC) 向所有的串行外设提供 DMA 通道,使其与片内或片外存储器传输数据

时不用经过处理器。这就 减少了传输连续数据流时处理器的开销。包含双指针的 PDC 控制器极

大的简化了 AT91RM9200 的缓冲器链接。

并行 I/O (PIO) 控制器与作为通用数据的 I/O 复用外设输入 / 输 出口线,以最大程度上适应器件

的配置。每条口线上包含有一个输入变化中断、开漏能力及可编程上拉电阻。

电源管理控制器 (PMC) 通过软件控制有选择的使能 / 禁用处理器及各种外设来使系统的功耗保

持最低。它用一个增强的时钟产生器来提供包括慢时钟 (32 kHz) 在内的选定时钟信号,以随时

优化功耗与性能。

AT91RM9200 集成了许多标准接口,包括 USB 2.0 全速主机和设备端口及与多数外设和在网络

层广泛使用的 10/100 Base-T 以太网媒体访问控制器 (MAC)。此外,它还提供一系列符合工业

标准的外设,可在音频、电信、 Flash 卡红外线及智能卡中使用。

为完善性能,AT91RM9200 集成了包括 JTAG-ICE、专门

UART 调试通道 (DBGU) 及嵌入式的

实时追踪的一系列的调试功能。这些功能使得开发、调试所有的应用特别是受实时性限制的应

用成为可能。

Peripheral DMA

Controller

3

AT91RM9200

1768B–ATARM–07-Jun-05

方框图 实箭头 ()表示由主机到从机

Figure 1. AT91RM9200 方框图

ARM920T Core

JTAG

Scan

ICE

AIC

Fast SRAM

16K bytes

PIO

PLLB

PLLA

OSC

PMC

System

Timer

OSC RTC

EBI

PIOA/PIOB/PIOC/PIOD

Controller

DBGU

MCI

USART0

USART1

USART2

USART3

SPI

SSC0

SSC1

SSC2

Timer Counter

TC0

TC1

TC2

Timer Counter

TC3

TC4

TC5

TWI

PIO

PIO

D0-D15

A0/NBS0

A1/NBS2/NWR2

A2-A15/A18-A22

A16/BA0

A17/BA1

NCS0/BFCS

NCS1/SDCS

NCS3/SMCS

NRD/NOE/CFOE

NWR0/NWE/CFWE

NWR1/NBS1/CFIOR

NWR3/NBS3/CFIOW

SDCK

SDCKE

RAS-CAS

SDWE

SDA10

BFRDY/SMOE

BFCK

BFAVD

BFBAA/SMWE

BFOE

BFWE

A23-A24

NWAIT

NCS5/CFCE1

D16-D31

TF0

TK0

TD0

RD0

RK0

RF0

TF1

TK1

TD1

RD1

RK1

RF1

TF2

TK2

TD2

RD2

RK2

RF2

TCLK0

TCLK1

TCLK2

TIOA0

TIOB0

TIOA1

TIOB1

TIOA2

TIOB2

TCLK3

TCLK4

TCLK5

TIOA3

TIOB3

TIOA4

TIOB4

TIOA5

TIOB5

TWD

TWCK

JTAGSEL

TDI

TDO

TMS

TCK

NTRST

FIQ

IRQ0-IRQ6

PCK0-PCK3

PLLRCB

PLLRCA

XIN

XOUT

XIN32

XOUT32

DDM

DDP

MCCK

MCCDA

MCDA0-MCDA3

MCCDB

RXD0

TXD0

SCK0

RTS0

CTS0

RXD1

TXD1

SCK1

RTS1

CTS1

DSR1

DTR1

DCD1

RI1

RXD2

TXD2

SCK2

RTS2

CTS2

RXD3

TXD3

SCK3

RTS3

CTS3

NPCS0

NPCS1

NPCS2

NPCS3

MISO

MOSI

SPCK

MCDB0-MCDB3

HDMA

HDPB

HDPA

HDMB

DRXD

DTXD

Ethernet MAC 10/100

ETXCK-ERXCK-EREFCK

ETXEN-ETXER

ECRS-ECOL

ERXER-ERXDV

ERX0-ERX3

ETX0-ETX3

EMDC

SDRAM

Controller

Burst

Flash

Controller

Static

Memory

Controller

PIO

Instruction Cache

16K bytes

Data Cache

16K bytes

MMU

EMDIO

DMA FIFO

DMA FIFO

USB Host

FIFO

USB Device

Transceiver

PIO

PIO PIO

Reset

and

Test

TST0-TST1

NRST

APB

Fast ROM

128K bytes

BMS

NCS2

A25/CFRNW

NCS4/CFCS

Misalignment

Detector

Address

Decoder

Abort

Status

NCS6/CFCE2

Transceiver

NCS7

Memory

Controller

Bus

Arbiter

Peripheral

Bridge

Peripheral

DMA

Controller

EF100

ETM

TSYNC

TCLK

TPS0 - TPS2

TPK0 - TPK15

CompactFlash

NAND Flash

SmartMedia

PDC

PDC

PDC

PDC

PDC

PDC

PDC

PDCPDCPDC

PDC

PDC

4

AT91RM9200

1768B–ATARM–07-Jun-05

主要特性 本节介绍各个模块的主要特性。

ARM920T 处理器 •ARM9TDMI

™

基于 ARM

®

v4T 架构

• 两套指令集

–32位高性能 ARM

®

指令集

–16位高代码密度 Thumb

®

指令集

•5级流水线结构:

– 取指令 (F)

– 指令译码 (D)

– 执行 (E)

– 数据存储器 (M)

– 写寄存器 (W)

•16-K字节数据缓存, 16-K 字节指令缓存

– 虚拟地址的 64 路相关缓存

– 每线 8 字

– 正向及反向写操作

– 伪随机或循环置换

– 低功耗 CAM RAM 设备

• 写缓冲器

–16字的数据缓冲器

–4地址的地址缓冲器

– 软件控制消耗

• 标准的 ARMv4 存储器管理单元 (MMU)

– 区域访问许可

– 允许以 1/4 页面大小对页面进行访问

–16个嵌入域

–64个输入指令 TLB 及 64 个输入数据 TLB

•8位、

16 位、 32 位的指令总线与数据总线

调试与测试 • 集成了嵌入式内部电路仿真器

• 调试单元

– 两引脚的 UART

– 调试信道

– 芯片 ID 寄存器

• 嵌入式追踪宏单元:ETM9 Rev2a

– 中级实现

– 半速时钟模式

– 四对地址比较器

– 两个数据比较器

– 八个存储器映射解码器输入

– 两个计数器

– 一个序列发生器

– 一个 18 字节的 FIFO

• 数字引脚通过 IEEE1149.1 JTAG 边界扫描

5

AT91RM9200

1768B–ATARM–07-Jun-05

引导程序 • 引导程序默认存储在 ROM 中

• 由外部存储器载入内部 SRAM 中运行

• 下载代码大小由内部 SRAM 大小决定

• 自动检测有效的应用程序

• 引导载入支持多数非易失性存储器

– 连接在 SPI NPCS0 上的 SPI DataFlash

®

– 两线 EEPROM

– 若器件集成了 EBI,则在 NCS0 上提供 8 位并行存储器

• 提供支持多种通信介质的引导上传器 (Boot Uploader) 以防外部 NVM 上未检测到有效程序

•DBGU (XModem协议 ) 上串行通信

•USB器件端口 (DFU 协议 )

嵌入式软件服务 •ATPCS适用

• AINSI/ISO 标准 C 适用

• 在 ARM/Thumb 交互工作中编译

•ROM进 入服务

• 提供 Te mp o、 Xmodem 及 DataFlash 服务

•CRC及正弦表

复位控制器 • 提供两条复位输入线 (NRST 与 NTRST):

• 初始化用户接口寄存器 ( 各个外设通过用户接口来定义 ) 且:

– 在 bootup 时对信号采样

– 强迫处理器读取零地址空间的下条指令

• 初始化嵌入式 ICE TAP 控制器

存储控制器 • 可编程的对四主机总线仲裁处理

– 内部总线由 ARM920T、 PDC、 USB 主机端口与以太网 MAC 主机共享

– 每个主机优先级在 0 ~ 7 之间分配

• 地址解码器提供如下选择:

– 八个 256-M 字节外部存储器区域

– 四个 1-M 字节内部存储器区域

– 一个 256-M 字节嵌入式外设区域

• 引导模式选项:

– 非易失性引导存储器可为片内或片外的

– 由 BMS 引脚在复位时的采样值选定

• 异常中断状态寄存器

– 保存所有引起发生异常中断的源、类型及访问参数

• 检测器失调

– 对所有数据访问进行校准检测

– 失调时产生中止

• 重新映射命令

– 对内部 SRAM 提供重新映射以代替引导 NVM

外部总线接口 • 集成了三个外部存储控制器:

JTAG上的复位信号

总线控制权在4个控制器间转

移,所以需要优先级

剩余637页未读,继续阅读

资源评论

newnewnew518

- 粉丝: 1

- 资源: 32

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功