没有合适的资源?快使用搜索试试~ 我知道了~

AURIX TC3xx_Power_Reset_Startup培训指导PPT文件

温馨提示

试读

32页

英飞凌AURIX TC3xx_Power_Reset_Startup培训指导PPT文件

资源详情

资源评论

资源推荐

AURIX™ 2

nd

Gen TC3xx

Power, Reset and Start-up Aspects

Nov 2

nd

, 2016

confidential

- DRAFT -

Agenda

Power Generation

Supply Monitoring and Reset

Power Modes

Power Distribution

Thermal Dissipation

1

2

3

4

5

2

2016-11-02 confidential Copyright © Infineon Technologies AG 2016. All rights reserved. - DRAFT - Infineon Proprietary

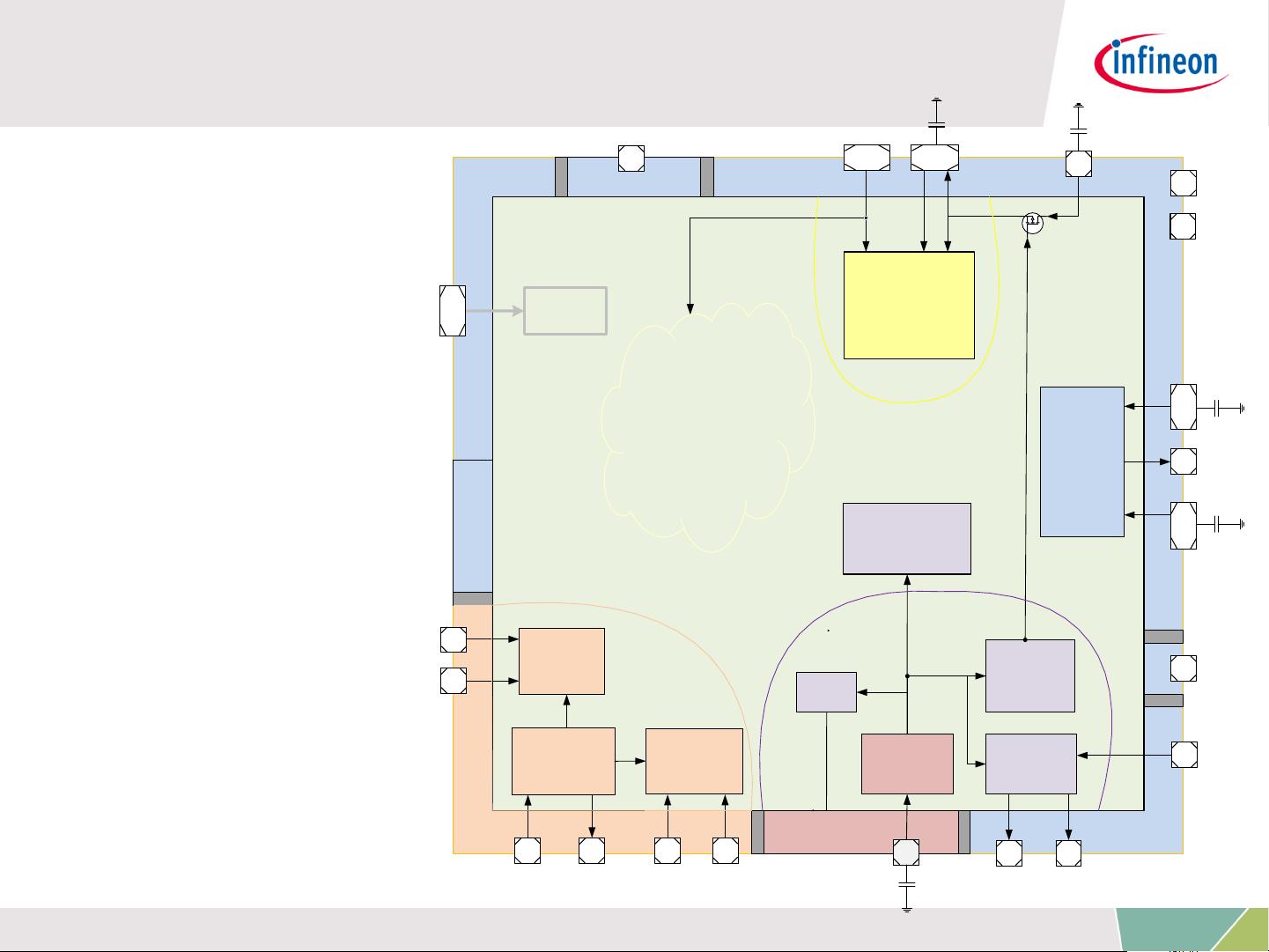

AURIX 2G

Power Domains

› 5V / 3.3V VEVRSB Standby Domain

– VDDPD Standby Domain

(Regulators, Start-up / Safety

modules, PMS, SCR)

– Standby Pads (P33, P34)

– CPU0 and CPU1

dLMU Standby RAM

› 5V / 3.3V VEXT Pad domain

– All Pads / Ports, Shared pads

– OSC, HSCT

› 5V / 3.3V VFLEX, VEBU independent

and isolated Pad domains

› 5V / 3.3V VDDM ADC domain

– EVADC, DSADC, ADC pads

› 3.3V VDDP3 Flash domain

– Flash Programming

› 1.25V VDD domain

– Core domain (CPUs,..)

– Flash Read Sense

› 1.25V VDDSB (ED domain, EMEM)

EVADC

ADC SUPPLY

Shared ADC pads

3.3V/5V (V

EXT

)

EVRC

SMPS

(V

DDPD

)

EVR PRE-

REGULATOR

V

GATE1P

CPU0+CPU1

dLMU

STANDBY RAM

(V

DD

or V

DDPD

)

V

GATE1N

HSCT

OSC

Sys PLL

Per. PLL

(V

DD

& V

EXT

)

3.3V/5V pads (V

FLEX

)

V

FLEX

(3.3/5 V)

V

SS(OSC)

(GND)

V

DD

(1.25 V)

V

EXT(OSC)

(5.0 V)

JTAG & LVDS pads

3.3/5.0V (V

EXT

)

EVR33

LDO

(V

DDPD

)

FLASH

(V

DD

& V

DDP3

)

V

DD

(1.25 V)

V

DDP3

(3.3 V)

3.3V/5V pads

(V

EXT

)

V

DDPD

(1.25 V)

FLEXPORT

/PORST

V

EXT

(5.0 V)

(3.3 V)

SCR

(V

DDPD

)

Standby Domain Pads

Shared ADC pads

P33.x/ P34.x (V

EVRSB

)

V

EVRSB

(3.3/5 V)

/ESRx

V

EXT

(3.3/5 V)

EEC/EMEM

(VDDSB)

(ED device only)

V

DDSB (ED)

(1.25 V)

I

DDRAIL

I

EXTFLEX

EDSADC

V

AREF2 + 3

(3.3/5 V)

V

AGND2 + 3

(GND)

V

AREF1

(3.3/5 V)

V

AGND1

(GND)

V

DDM

(3.3/5 V)

V

SSM

(GND)

Analog pads

3.3V/5V (V

DDM

)

Core Logic

(VDD)

V

EBU

(3.3/5 V)

3

2016-11-02 confidential Copyright © Infineon Technologies AG 2016. All rights reserved. - DRAFT - Infineon Proprietary

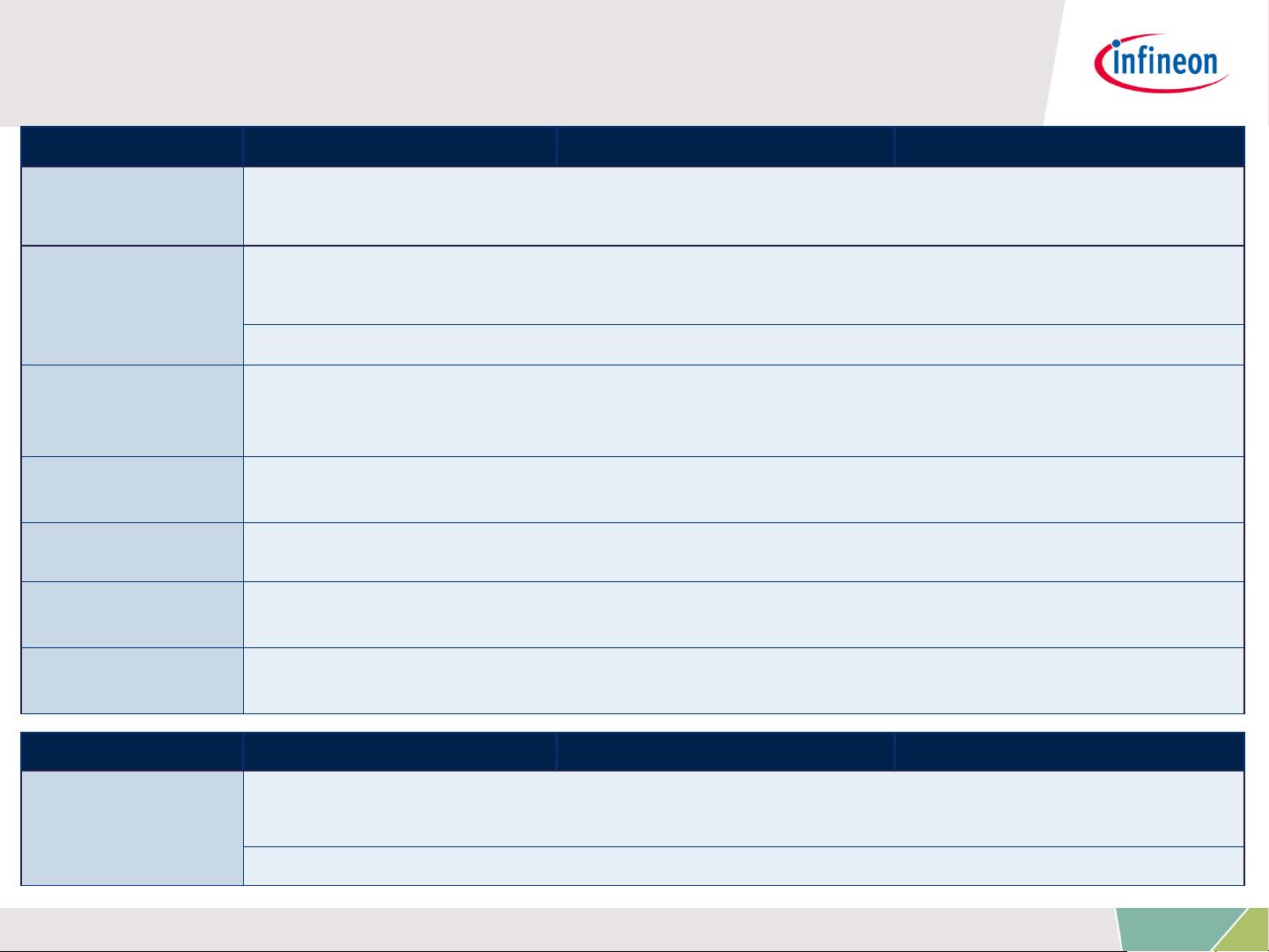

AURIX 2G

Salient features

TC39x TC38x TC37x TC36x TC35x

Dual / Triple Ext.

Supply

5V / 3,3V ± 10% External supply range. Single, dual & triple supply as in AURIX.

Separate VDDM / VAREF supply for ADC

EVRC Core

Regulator

LC DC DC (Efficiency =72%+) (0.8 MHz and 1.8 MHz nominal switching frequency)

3,3uH - 4,7uH inductor + 6,8 -10uF input cap +10 - 22uF output cap

Static accuracy target = 2% over PVT + 12mV ripple in case of SMPS

Nominal VDD

Set point range

TC3xx VDD nominal voltage = 1,25V ± 10%

1,2 V up to 1,3 V in steps of 5 mV in case of TC3xx

EVR33 3,3V regulator

LDO with internal pass devices. 1 uF buffer capacitor.

Internal regulator static accuracy target = 2% over PVT

VDDP3 Range &

Tolerance

3,3V ± 10%. No voltage scaling. Static accuracy = 2%

Primary supply

monitors

Bi-directional PORST concept as in C65. Configurable (1% - 2%) voltage and time hysteresis.

Default reset threshold < -10%

Secondary supply

monitors

Internal dedicated Secondary monitors with static accuracy = 2% over PVT. Configurable averaging filter

VEXT(3.3V/5V), VDDP3(3.3V), VDD(1.3V), VDDM(3.3V/5V), VEVRSB(3.3V/5V) & VDDPD(1.3V)

TC33x TC32x

EVRC Core

Regulator

SC DC DC . 1uF flying cap + 10uF i/p cap

300 mA current capability with 72% efficiency. Upto 450 mA capability with less efficiency.

Static accuracy target = 2% over PVT + 12mV ripple in case of SMPS

4

2016-11-02 confidential Copyright © Infineon Technologies AG 2016. All rights reserved. - DRAFT - Infineon Proprietary

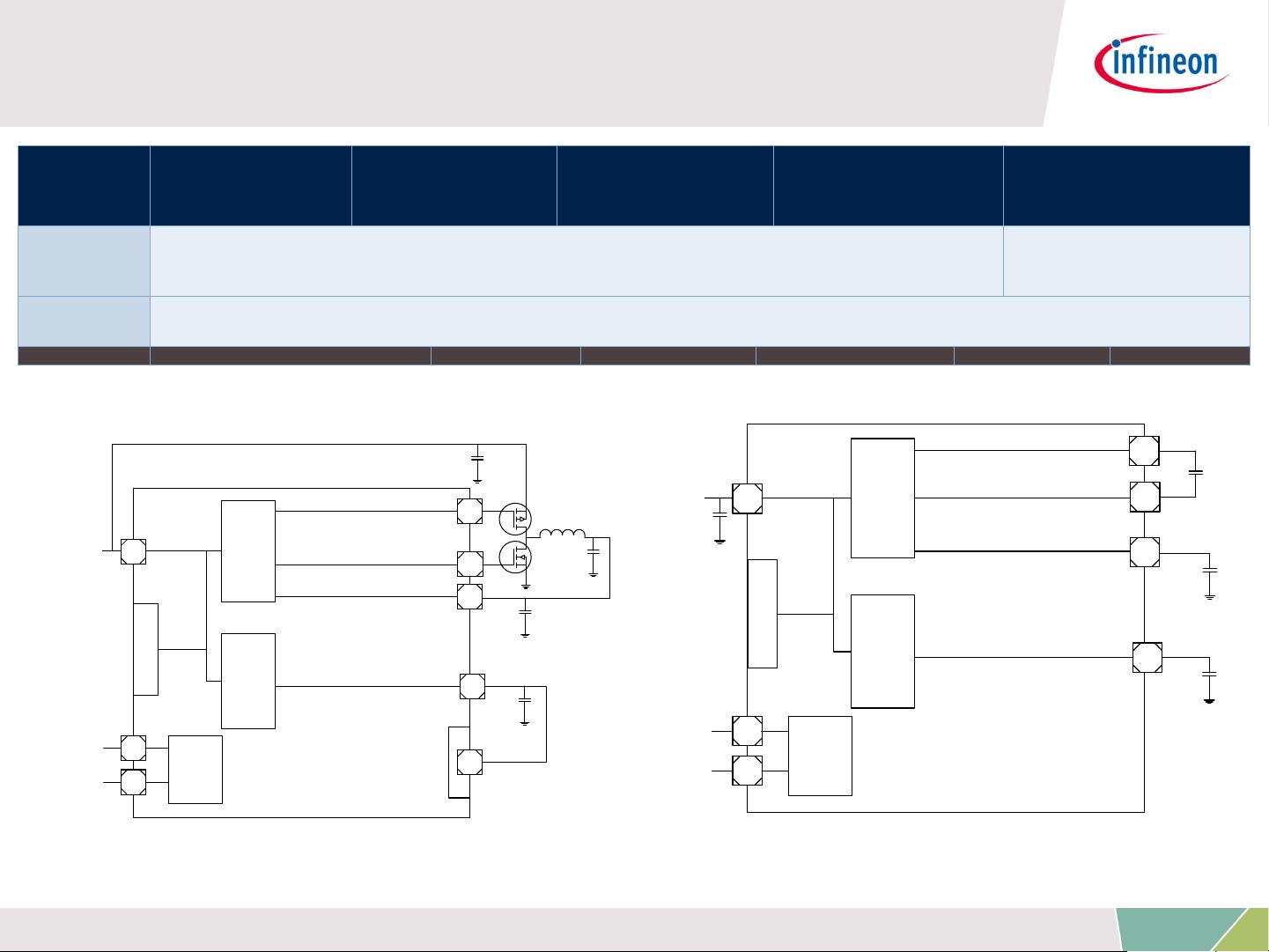

AURIX 2G

Regulator Support

TC39x

3.3V / 5V

TC38x

3.3V / 5V

TC37x

3.3V / 5V

TC36x TC35x

3.3V / 5V

TC33x TC32x

3.3V / 5V

EVR12

LC DC DC

3,3 - 4,7uH inductor + 6,8-10uF i/p cap +10-22uF o/p cap

SC DC DC

10 uF + 1 uF

EVR33 LDO with internal pass devices. 1 uF capacitor.

V

EXT

V

DD

ADC

EVRC

EVR33

EVR Switch mode topology a1 v 0.5

V

GATE1P

L

DC

C

DC

V

FLEX

V

GATE1N

V

DDM

/ V

AREF

(5 V or 3.3 V)

5 V

External Supply

V

DDP3

/ V

DDFL3

FLEXPORT

P

O

R

T

S

V

SSM

/ V

AGND

V

FLEX

can be either connected to

V

DDP3

(3.3 V) or

V

EXT

(5.0 V)

Separate analog supply

and ground pins

Exposed die pad is connected to digital ground.

1.2x V

3.3 V

P + N

Channel

MOSFET

C

OUT

C

IN

V

EXT

V

DD

ADC

EVRC

EVR33

EVR Switch mode topology a2 v 0.6

V

CAP0

V

CAP1

V

DDM

/ V

AREF

(5 V or 3.3 V)

5 V

External Supply

V

DDP3

P

O

R

T

S

V

SSM

/ V

AGND

Separate analog supply

and ground pins

Exposed die pad is connected to digital ground.

1.25 V

3.3 V

C

OUT

C

IN

C

FLY

C

OUT

5

2016-11-02 confidential Copyright © Infineon Technologies AG 2016. All rights reserved. - DRAFT - Infineon Proprietary

剩余31页未读,继续阅读

程序猿Dash

- 粉丝: 20

- 资源: 7

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于keras+fasterRCNN,在VOC格式的口罩数据集上训练,检测人群中有无戴口罩python源码+模型

- 基于opencv+qt5机器视觉的传统缺陷检测, 即采用标准图片和待测图片进行pixel to pixel的XOR操作源码+文档

- 管道内检测缺陷数据库管理系统源码+文档说明+sln

- 毕业设计-低功耗STM32F411开发板(原理图+PCB源文件+官方例程+驱动等)源码+文档说明+截图

- 基于yolov5-tensorRT检测+发动机缸体内壁缺陷检测系统源码+文档说明

- 基于C++实现的锂电池缺陷检测源码+文档说明

- push_version

- 软件自制图像批量压缩工具

- 经典缺陷检测算法源码整理包含PaDiM(2020ICPR)、PatchCore(2022CVPR)、SimpleNet+文档说明

- 基于深度学习的抗梯度噪声的缺陷检测器python源码+文档说明+模型的预训练

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论5