没有合适的资源?快使用搜索试试~ 我知道了~

TDC GPX2 规格书

需积分: 38 31 下载量 133 浏览量

2018-12-17

14:51:03

上传

评论 1

收藏 1.36MB PDF 举报

温馨提示

试读

77页

TDC GPX2 规格书 ps级别计时器

资源推荐

资源详情

资源评论

ams Datasheet Page 1

[v1-03] 2017-Dec-18 Document Feedback

TDC-GPX2

4-Channel Time-to-Digital Converter

The GPX2 is a high performance time-to-digital converter (TDC)

frontend device.

Highest measurement performance and highest data

throughput is achieved with LVDS stop inputs and LVDS serial

outputs for each channel. Current saving operation is also

possible with CMOS inputs and SPI readout.

High configuration flexibility and unlimited measurement

range cover many applications. They range from portable

handheld laser range equipment to ambitious time-of-flight

measurements of highest performance, as e.g. done in medical

imaging applications.

GPX2 operates without any locked loop technologies. GPX2

calculates all stop measurements inside, proportional to the

applied reference clock. Combinations of best single shot

accuracy of 10ps with lowest pulse-to-pulse spacing <5ns and

maximum data throughput rate of 70MSPS per stop input are

possible.

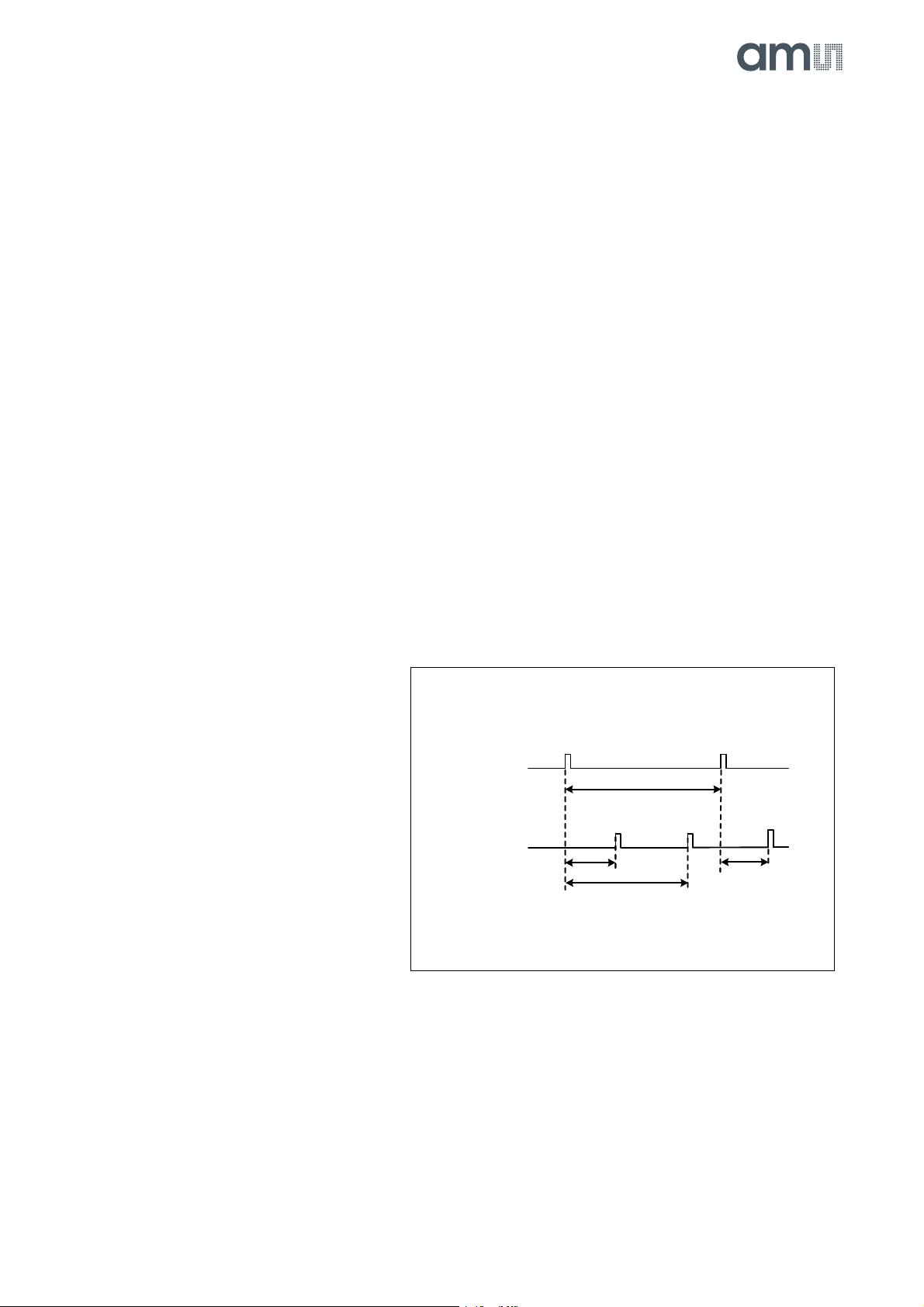

Figure 1:

Time Interval Measurements

Ordering Information and Content Guide appear at end of

datasheet.

General Description

#1

REFCLK

#2

STOP

T1

T3

T-REF

T2

Page 2 ams Datasheet

Document Feedback [v1-03] 2017-Dec-18

TDC-GPX2 − General Description

Key Benefits & Features

The benefits and features of this device are listed below:

Figure 2:

Added Value of Using TDC-GPX2

Applications

• Automated Test Equipment

• Laser Range Measurement

• Medical Imaging

• Time-of-Flight Measurement

• Particle Physics

• Lidar, Radar, Sonar

Benefits Features

• Simple data post-processing thanks to

calibrated results

• 4 stop channels with serial

• 20ns pulse-to-pulse spacing

• Maximum 35MSPS

• 2 combined channels with

• 5ns pulse-to-pulse spacing

• Maximum 70MSPS

• Single shot accuracy

• 20ps rms single shot resolution per channel

• 10ps rms with high resolution option

• Unlimited measuring range 0s to 16s

• Event assignment thanks to reference clock

index simplifies coincidence measurements

• Easy pulse width measurements

• High efficiency thanks high sample rate

• Differential reference clock input 2MHz to 12.5MHz,

optional with quartz

• Inputs optional with LVDS or CMOS level

• Readout with LVDS or SPI

• 16-stage FIFO per channel

• Automatic calibration to reference clock (no PLL or DLL)

• SPI compatible 4-wire interface for configuration

• Compact design thanks to small package

and low number of external components

• Reduced cooling thanks to low power

consumption

• Supply voltage 3.3V

• Power dissipation 60mW to 450mW

• Standby current 60μA

• QFN64 (9mm x 9mm) or QFP64 (12mm x 12mm)

ams Datasheet Page 3

[v1-03] 2017-Dec-18 Document Feedback

TDC-GPX2 − General Description

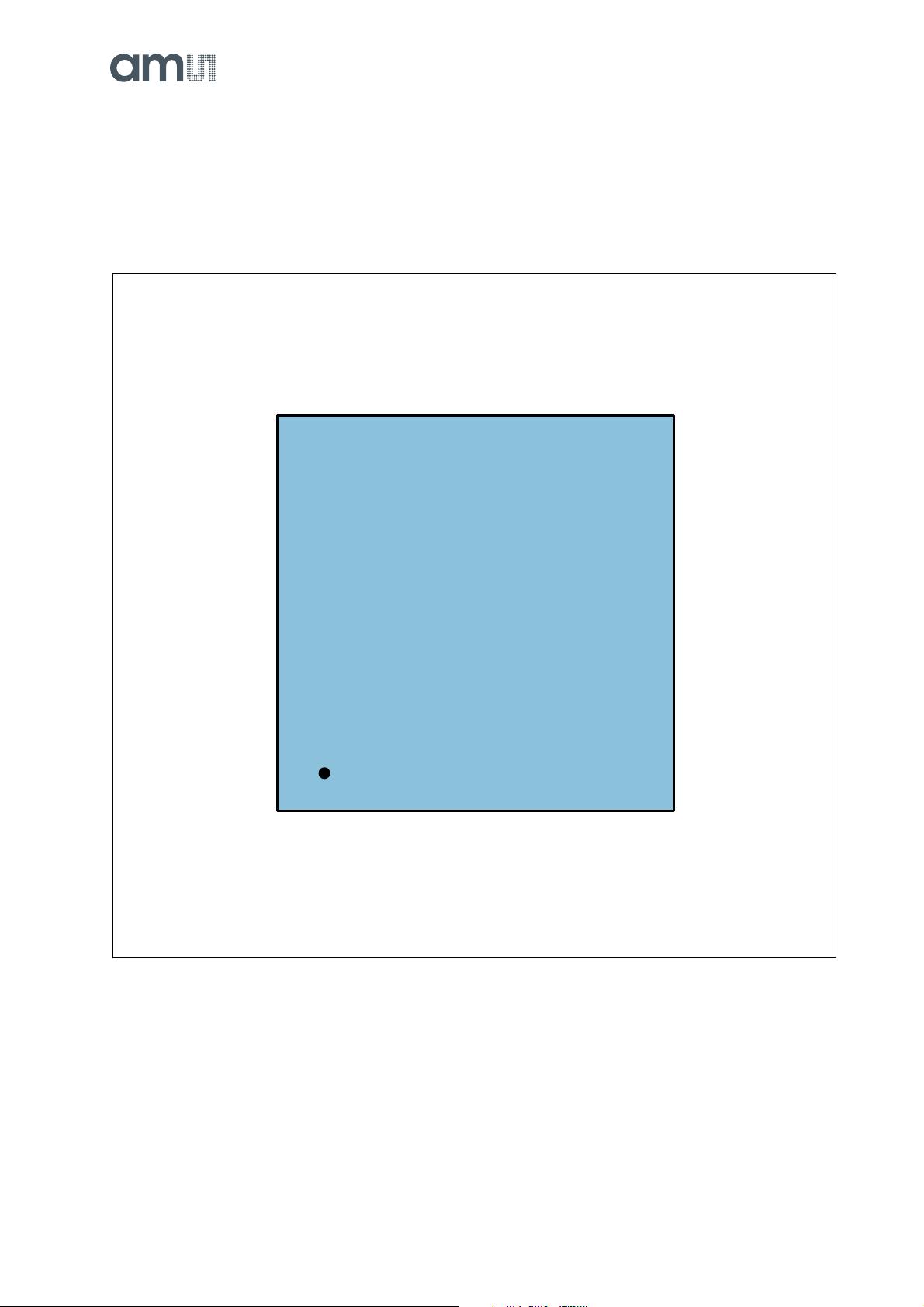

Block Diagram

The functional blocks of this device are shown below:

Figure 3:

Functional Blocks of TDC-GPX2

SDO4P

SDO4N

FRAME4P

FRAME4N

SDO3P

SDO3N

FRAME3P

FRAME3N

INTERRUPT

SSN

SCK

MOSI

MISO

PARITY

TVDD18

CVDD18

DVDD18

SDO1P

SDO1N

DVDD33

FRAME1P

FRAME1N

REFOSCI

REFOSCO

STOP1P

STOP1N

Encoder

Serializer

44:1 ... 14:1

Encoder

Serializer

44:1 ... 14:1

Encoder

Serializer

44:1 ... 14:1

Encoder

Serializer

44:1 ... 14:1

LCLKINP

LCLKINN

Serial Interface

Configuration

Reference

Clock

Index

Counter

FIFO

FIFO

FIFO

FIFO

SDO2P

SDO2N

FRAME2P

FRAME2N

STOP3P

STOP3N

STOP2P

STOP2N

STOP4P

STOP4N

DISABLEP

DISABLEN

RSTIDXP

RSTIDXN

REFCLKP

REFCLKN

TDC

TDC

TDC

TDC

TDC

DVDD18

RVDD33

DVDD33

Encoder

LCLKOUTP

LCLKOUTN

TVDD33

LVR

CVDD18O

TVDD18O

DVDD18O

Page 4 ams Datasheet

Document Feedback [v1-03] 2017-Dec-18

TDC-GPX2 − Pin A ssignm ents

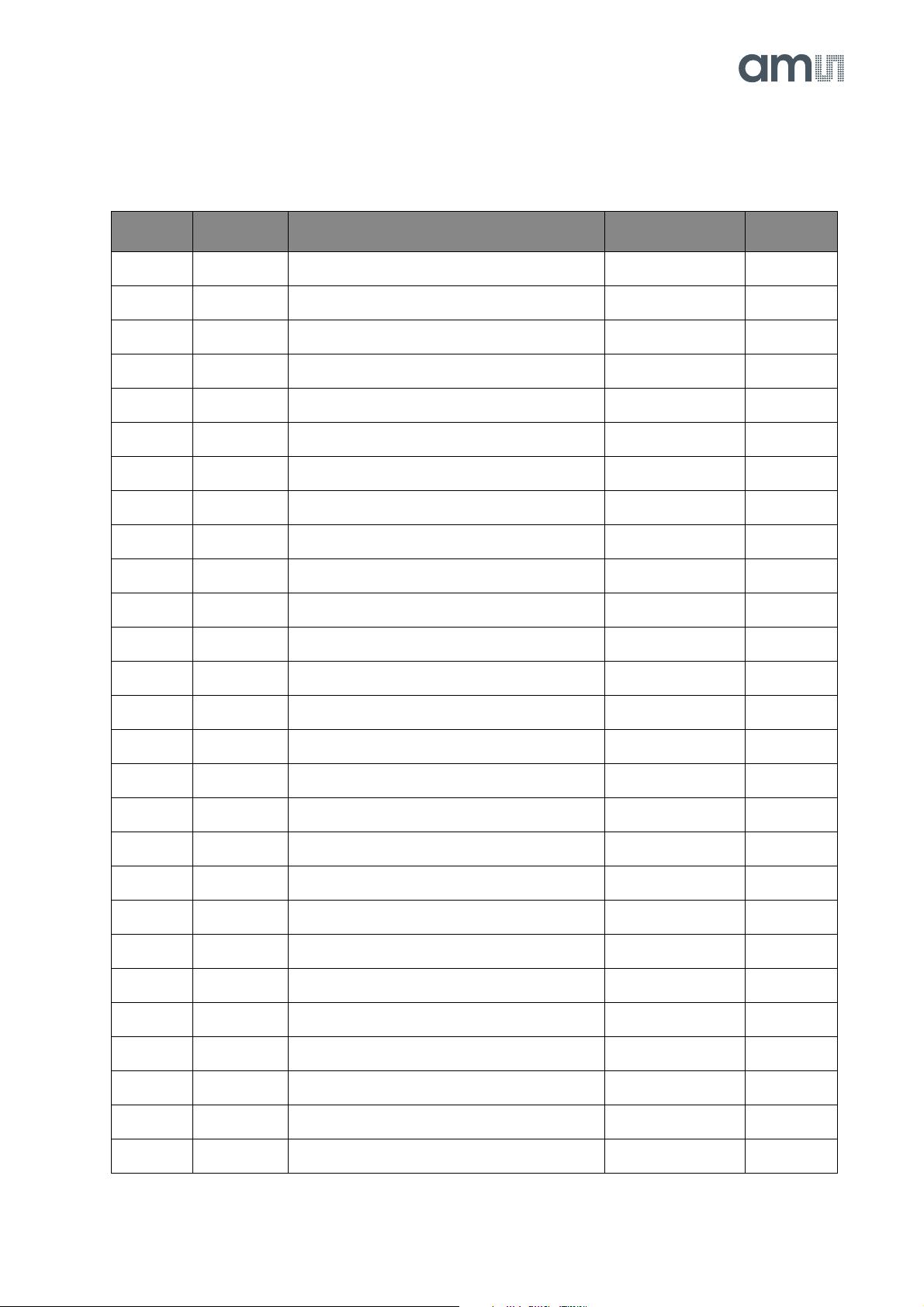

The TDC-GPX2 is shipped in QFN64 or QFP64 plastic packages

with the following pin assignment.

Pin Diagram

Figure 4:

Pin Diagram of TDC-GPX2

Pin Assignments

FRAME1N

FRAME1P

SDO1N

SDO1P

FRAME2N

FRAME2P

SDO2N

SDO2P

FRAME3N

FRAME3P

SDO3N

SDO3P

FRAME4N

FRAME4P

SDO4N

SDO4P

DGND

TVDD33

TGND

TVDD18

CVDD18

CGND

RGND

CVDD18O

TVDD18O

DVDD18O

RVDD33

DVDD18

DVDD33

DGND

LCLKOUTP

LCLKOUTN

STOP1N

STOP1P

STOP2N

STOP2P

TVDD33

RSTIDXN

RSTIDXP

REFCLKN

REFCLKP

DISABLEN

DISABLEP

TGND

STOP3N

STOP3P

STOP4N

STOP4P

TVDD33

TGND

TVDD18

REFOSCI

REFOSCO

PARITY

INTERRUPT

SSN

SCK

MOSI

MISO

DVDD18

DVDD33

DGND

LCLKINP

LCLKINN

TDC-GPX2

48

49

33

32

16

17

64

1

ams Datasheet Page 5

[v1-03] 2017-Dec-18 Document Feedback

TDC-GPX2 − Pin Assignments

Pin Description

Figure 5:

Pin Description of TDC-GPX2

Pin No. Pin Name Description Type Not Used

1 FRAME1N Negative frame signal of stop channel 1 LVDS Output Open

2 FRAME1P Positive frame signal of stop channel 1 LVDS Output Open

3 SDO1N Negative serial data output of stop channel 1 LVDS Output Open

4 SDO1P Positive serial data output of stop channel 1 LVDS Output Open

5 FRAME2N Negative frame signal of stop channel 2 LVDS Output Open

6 FRAME2P Positive frame signal of stop channel 2 LVDS Output Open

7 SDO2N Negative serial data output of stop channel 2 LVDS Output Open

8 SDO2P Positive serial data output of stop channel 2 LVDS Output Open

9 FRAME3N Negative frame signal of stop channel 3 LVDS Output Open

10 FRAME3P Positive frame signal of stop channel 3 LVDS Output Open

11 SDO3N Negative serial data output of stop channel 3 LVDS Output Open

12 SDO3P Positive serial data output of stop channel 3 LVDS Output Open

13 FRAME4N Negative frame signal of stop channel 4 LVDS Output Open

14 FRAME4P Positive frame signal of stop channel 4 LVDS Output Open

15 SDO4N Negative serial data output of stop channel 4 LVDS Output Open

16 SDO4P Positive serial data output of stop channel 4 LVDS Output Open

17 LCLKOUTN Negative serial clock output LVDS Output Open

18 LCLKOUTP Positive serial clock output LVDS Output Open

19, 21, 62 DGND Ground for digital and IO units Power Supply

20, 61 DVDD33 3.3V supply for digital and IO units Power Supply

22, 60 DVDD18 1.8V supply for digital and IO units Power Supply

23 RVDD33 3.3V supply for linear voltage regulator Power Supply

24 DVDD18O 1.8V supply voltage for digital and IO units Regulator Out Open

25 TVDD18O 1.8V supply voltage for time frontend Regulator Out Open

26 CVDD18O 1.8V supply voltage for time digital converter Regulator Out Open

27 RGND Ground for linear voltage regulator Power Supply

28 CGND Ground for TDC Power Supply

剩余76页未读,继续阅读

资源评论

ljthink

- 粉丝: 7

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功