没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

静态时序分析(Static Timing Analysis)基础及应用(下)

前言

在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。此

一趋势使得如何确保 IC 品质成為今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static

Timing Analysis 简称 STA)经由完整的分析方式判断 IC 是否能够在使用者指定的时序下正常工作,对确

保 IC 品质之课题,提供一个不错的解决方案。在「静态时序分析(Static Timing Analysis)基础及应用

(上)」一文中笔者以简单叙述及图例说明的方式,对 STA 的基础概念做了详尽的说明。接下来,就让

我们藉由实际设计范例来瞭解 STA 在设计流程的应用。

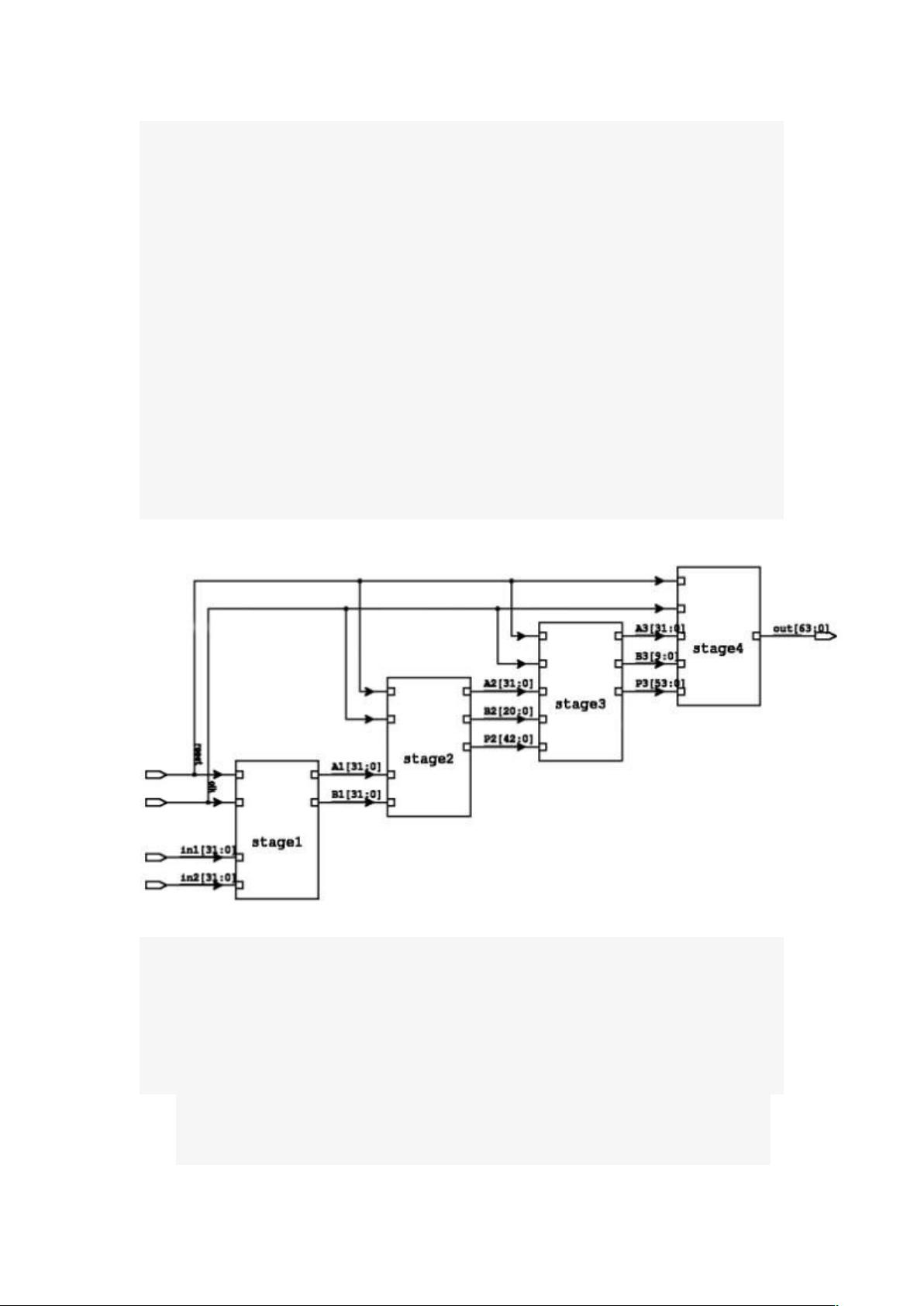

设计范例说明

设计范例为一个 32bit x 32bit 的 Pipeline 乘法器,其架构如图一所示。Pipeline 共分 3 级,电路之输出输

入端皆有暂存器储存运算数值。

图一

依据 Cell-based 设计的方式,首先以硬体描述语言设计图一之电路。接下来实作此电路,进行合成

(Synthesis)及布局与绕线(P&R)。并在实作的各步骤后进行静态时序分析,确认时序规格是否满足。

实作及验证所用到的软体及设计资料库如下所示:

← 合成:Synopsys

TM

Design Compiler

← 布局与绕线:Synopsys

TM

Astro

← 设计资料库:Artisan

TM

0.18um Cell Library

在接下来的文章中,各位将会看到静态时序分析在实作过程中的应用。藉由实际产生的数据瞭解在不同实

做步骤上时序分析的差异。

时序限制(Timing Constraint)

要作静态时序分析,首先要有时序限制。此设计范例的时序限制如下所述。(à 后為设定时序限制之

SDC 指令)

1 时脉规格(Clock Specification)

1.1 週期:6ns à create_clock -name "MY_CLOCK" -period 6 -waveform {0 3} [get_ports {clk}]

1.2 Source Latency:1ns à set_clock_latency -source 1 [get_clocks {MY_CLOCK}]

1.3 Network Latency:1ns à set_clock_latency 1 [get_clocks {MY_CLOCK}]

1.4 Skew:0.5ns à set_clock_uncertainty 0.5 [get_clocks {MY_CLOCK}]

2 周边状况(Boundary Condition)

2.1 输入延迟(Input Delay):1.2ns à set allin_except_CLK [remove_from_collection [all_inputs]

[get_ports clk] ]

set_input_delay $I_DELAY -clock MY_CLOCK $allin_except_CLK

2.2 输出延迟(Output Delay):1.2ns à set_output_delay $O_DELAY -clock MY_CLOCK

[all_outputs]

2.3 输出负载(Output Loading):0.5pF à set_load $O_LOAD 0.5 [all_outputs]

3 时序例外(Timing Exception):无

合成软体之时序报告

当 Synopsys Design Compiler 将电路合成完毕后,执行下面指令可以產生时序报告:

report_timing -path full -delay max -max_paths 10 -input_pins \

-nets -transition_time -capacitance > timing_syn.txt

时序报告会储存在 timing_syn.txt 此档案中。在档案的开头不远处,会列出此电路最有可能不符合时序规

格的路径(Critical Path)。例如:

Startpoint: S2/B2_reg_0_

(rising edge-triggered flip-flop clocked by MY_CLOCK)

Endpoint: S3/P3_reg_47_

(rising edge-triggered flip-flop clocked by MY_CLOCK)

Path Group: MY_CLOCK

Path Type: max

在这个例子中,Critical Path 的起点 Flip-Flop 是第 2 个 Pipeline Stage 内的 B2 暂存器的第 0 个位元,终

点 Flip-Flop 则是第 3 个 Pipeline Stage 内的 P3 暂存器的第 47 个位元(图二)。

在 Critical Path 报告的下方会有 Wire Load Model 的资讯,此范例使用的是 UMC18_Conservative

Model。这个 Model 会以较悲观的方式预估连线的延迟时间(Interconnect Delay)。

图二

继续往下检视档案,你会看到 Critical Path 的详细时序资讯。例如:

Point Fanout Cap Trans Incr Path

-------------------------------------------------------------------------------

clock MY_CLOCK (rise edge) 0.00 0.00

clock network delay (ideal) 2.00 2.00

S2/B2_reg_0_/CK (DFFHQX4) 0.00 0.00 2.00r

S2/B2_reg_0_/Q (DFFHQX4) 0.16 0.30 2.30r

S2/n36 (net) 1 0.03 0.00 2.30r

剩余13页未读,继续阅读

资源评论

liujl_sdn

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功