没有合适的资源?快使用搜索试试~ 我知道了~

三星Nand Flash 2G芯片资料

温馨提示

试读

47页

三星Nand Flash 2G芯片资料Nand Flash,K9GAG08U0E

资源推荐

资源详情

资源评论

- 1 -

K9GAG08U0E

Rev. 0.4, Nov. 2009

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND

SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed

herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung

Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property

right is granted by one party to the other party under this document, by implication, estoppel or other-

wise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or

similar applications where product failure could result in loss of life or personal or physical harm, or any

military or defense application, or any governmental procurement to which special terms or provisions

may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

ⓒ 2009 Samsung Electronics Co., Ltd. All rights reserved.

K9HCG08U5E

Advance

16Gb E-die NAND Flash

Multi-Level-Cell (1bit/cell)

datasheet

- 2 -

datasheet FLASH MOMORY

Rev. 0.4

K9HCG08U5E

K9GAG08U0E

Advanc

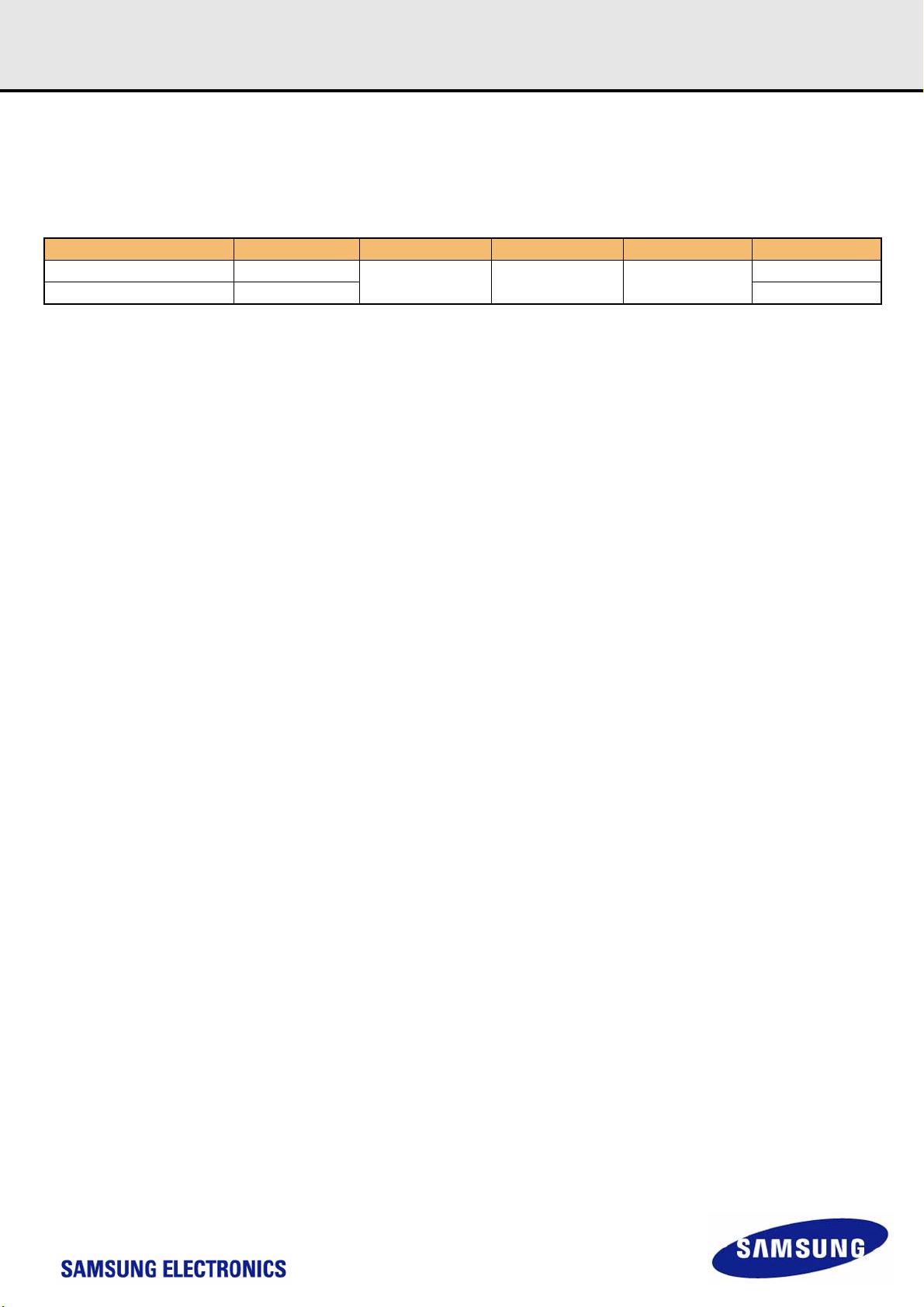

Revision History

Revision No. History Draft Date Remark Editor

0.0 1. Initial issue Jun. 12, 2009 Advance

0.1 1. Pin configuration is changed.

2. tREA is changed from 20ns to 25ns.

3. Memory cell array is amended.

4. Row address is modified.

5. Dummy busy time for Two-Plane Program(tDBSY) is deleted.

Oct. 21, 2009 Advance

0.2 1. Pin configuration is changed. Oct. 21, 2009 Advance

0.3

1. tRC/tWC is changed from 30ns to 20ns.

2. The Parameter related tRC/tWC is changed

Nov. 6, 2009 Advance

0.4 1. 52LGA (11x14) QDP is added Nov. 13, 2009 Advance S.M.Lee

- 3 -

Table Of Contents

datasheet FLASH MOMORY

Rev. 0.4

K9HCG08U5E

K9GAG08U0E

Advanc

1.0 ORDERING INFORMATION .....................................................................................................................................4

1.1 Product List.............................................................................................................................................................. 4

1.2 Features ...........................................................................................................................................................4

1.3 General Description................................................................................................................................................. 4

1.4 Pin Configuration (TSOP1)...................................................................................................................................... 5

1.5 Package Dimensions............................................................................................................................................... 5

1.6 Pin Description ........................................................................................................................................................ 7

2.0 PRODUCT INTRODUCTION......................................................................................................................................9

2.1 Absolute Maximum Ratings..................................................................................................................................... 10

2.2 Recommended Operating Conditions ..................................................................................................................... 10

2.3 Dc And Operating Characteristics(Recommended Operating Conditions Otherwise Noted.)................................. 10

2.4 Valid Block............................................................................................................................................................... 10

2.5 Ac Test Condition .................................................................................................................................................... 11

2.6 Capacitance(Ta=25×c, Vcc=3.3v, F=1.0mhz) ......................................................................................................... 11

2.7 Mode Selection........................................................................................................................................................ 11

2.8 Program / Erase Characteristics ........................................................................................................................11

2.9 AC Timing Characteristics for Command / Address / Data Input ............................................................................12

3.0 NAND FLASH TECHNICAL NOTES ..........................................................................................................................13

3.1 Initial Invalid Block(s)............................................................................................................................................... 13

3.2 Initial Invalid Block(s)............................................................................................................................................... 13

3.3 Error in write or read operation................................................................................................................................ 14

3.4 Addressing for program operation........................................................................................................................... 16

3.5 System Interface Using CE don’t-care. ...................................................................................................................17

4.0 TIMING DIAGRAMS ...................................................................................................................................................18

4.1 Command Latch Cycle ............................................................................................................................................ 18

4.2 Address Latch Cycle................................................................................................................................................ 18

4.3 Input Data Latch Cycle ............................................................................................................................................19

4.4 * Serial Access Cycle after Read(CLE=L, WE=H, ALE=L)...................................................................................... 19

4.5 Serial Access Cycle after Read(EDO Type, CLE=L, WE=H, ALE=L) ..................................................................... 20

4.6 Status Read Cycle................................................................................................................................................... 20

4.7 Read Operation ....................................................................................................................................................... 21

4.8 Read Operation(Intercepted by CE)........................................................................................................................ 21

4.9 Random Data Output In a Page .............................................................................................................................. 22

4.10 Cache Read Operation(1/2) .................................................................................................

................................. 23

4.11 Cache Read Operation(2/2) .................................................................................................................................. 24

4.12 Page Program Operation....................................................................................................................................... 25

4.13 Page Program Operation with Random Data Input ............................................................................................... 26

4.14 Copy-Back Program Operation with Random Data Input...................................................................................... 27

4.15 Cache Program Operation(available only within a block)...................................................................................... 28

4.16 Block Erase Operation........................................................................................................................................... 29

4.17 Read ID Operation................................................................................................................................................. 30

4.17.1ID Definition Table .....................................................................................................................................31

5.0 DEVICE OPERATION ................................................................................................................................................33

5.1 Page Read............................................................................................................................................................... 33

5.2 CACHE READ......................................................................................................................................................... 34

5.3 Page Program ......................................................................................................................................................... 36

5.4 Copy-back Program................................................................................................................................................. 37

5.5 Cache Program ....................................................................................................................................................... 38

5.6 Block Erase ............................................................................................................................................................. 41

5.7 Read Status............................................................................................................................................................. 42

5.8 Read ID ................................................................................................................................................................... 43

5.9 RESET..................................................................................................................................................................... 43

5.10 Ready/Busy ........................................................................................................................................................... 45

6.0 DATA PROTECTION & POWER UP SEQUENCE.....................................................................................................46

6.1 WP AC Timing guide ............................................................................................................................................... 47

- 4 -

datasheet FLASH MOMORY

Rev. 0.4

K9HCG08U5E

K9GAG08U0E

Advanc

1.0 ORDERING INFORMATION

1.1 Product List

1.2 Features

• Voltage Supply

- 3.3V Device : 2.7V ~ 3.6V

• Orga

nization

- Memory Cell Array : (2,076M x 110.49K) x 8bit

- Data Register : (8K + 436) x 8bit

• Automa

tic Program and Erase

- Page Program : (8K + 436)Byte

- Block Erase : (1M + 54.5K)Byte

• Page

Read Operation

- Page Size : (8K + 436)Byte

- Random Read : 400μs(

Max.)

- Serial Access : 20ns(Min.)

• Memo

ry Cell : 2bit / Memory Cell

• F

ast Write Cycle Time

- Program time : 1.6ms(Typ.)

- Block Erase Time : 1.5ms(Typ.)

• Command

/Address/Data Multiplexed I/O Port

• Har

dware Data Protection

- Program/Erase Lockout During Power Transitions

• Relia

ble CMOS Floating-Gate Technology

- ECC Requirement : 24bit/(1K +54.5)Byte

- Endurance & Data Retention : Pleae refer to the qualification report

• Command

Register Operation

• Unique ID f

or Copyright Protection

• Package

:

- K9GAG08U0E-SCB0/SIB0 : Pb-FREE PACKAGE

48 - Pin TSOP1 (12 x 20 / 0.5 mm pitch)

- K9HCG08U5E-LCB0/LCI0: Pb/Halogen-free

52- Pin LGA (11x14 / 0.75mm pitch)

1.3 General Description

The device is offered in 3.3V Vcc. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. A program operation

can be performed in typical 1.6ms on the 8,628-byte page and an erase operation can be performed in typical 1.5ms on a (1M+54.5K)byte block. Data in

the data register can be read out at 30ns cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command input.

The on-chip write controller automates all program and erase functions including pulse repetition, where required, and internal verification and margining

of data. Even the write-intensive systems can take advantage of the K9GAG08U0E′s extended reliability of P/E cycles which are presented in the Qualifi-

cation report by providing ECC(Error Correcting Code) with real time mapping-out a

lgorithm. The K9GAG08U0E is an optimum solution for large nonvol-

atile storage applications such as solid state file stor

age and other portable applications requiring non-volatility.

Part Number Density Interface Vcc Range Organization PKG Type

K9GAG08U0E-S 16Gb

Conventional 2.7V ~ 3.6V x8

48TSOP1

K9HCG08U5E-L 64Gb 52LGA(11x14)

- 5 -

datasheet FLASH MOMORY

Rev. 0.4

K9HCG08U5E

K9GAG08U0E

Advanc

1.4 Pin Configuration (TSOP1)

K9GAG08U0E-PCB0/PIB0

48-pin TSOP1

Standard Type

12mm x 20mm

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

N.C

N.C

N.C

N.C

N.C

N.C

R/B

RE

CE

N.C

N.C

Vcc

Vss

N.C

N.C

CLE

ALE

WE

WP

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

I/O7

I/O6

I/O5

I/O4

N.C

N.C

Vcc

Vss

N.C

N.C

N.C

I/O3

I/O2

I/O1

I/O0

N.C

N.C

N.C

N.C

N.C

1.5 Package Dimensions

48-PIN LEAD FREE PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)

48 - TSOP1 - 1220AF

Unit :mm/Inch

0.787±0.008

20.00±0.20

#1

#24

0.16

+0.07

-0.03

0.008

+0.003

-0.001

0.50

0.0197

#48

#25

0.488

12.40

MAX

12.00

0.472

0.10

0.004

MAX

0.25

0.010

()

0.039±0.002

1.00±0.05

0.002

0.05

MIN

0.047

1.20

MAX

0.45~0.75

0.018~0.030

0.724±0.004

18.40±0.10

0~8°

0.010

0.25

TYP

0.125

+0.075

0.035

0.005

+0.003

-0.001

0.50

0.020

()

0.20

+0.07

-0.03

剩余46页未读,继续阅读

资源评论

wb8810232022-03-13学习了,不错

wb8810232022-03-13学习了,不错 sunshineTom2013-03-08完整K9GAG08U0E数据手册

sunshineTom2013-03-08完整K9GAG08U0E数据手册 linzhongdubu2014-05-24资料比较完整,值得推荐!

linzhongdubu2014-05-24资料比较完整,值得推荐! hnoys2012-02-10完整K9GAG08U0E数据手册

hnoys2012-02-10完整K9GAG08U0E数据手册

linlong1988

- 粉丝: 1

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- IMG_20240425_190941.jpg

- 基于stm32的pid控制算法附带串口控制台

- 实验项目一:线性表(模板 ).docx

- 基于LM317A设计交流220V输入可调5V-12V直流输出稳压电源电路multisim10仿真源文件.zip

- Screenshot_2024-04-25-17-04-18-55_2332cb9b27b851b548ba47a91682926c.jpg

- -基于AVR单片机的LNG加液机控制器设计.pdf

- ThePowerOfNow-EckhartTolle.mobi

- BLOCK_TYPE_HEARTBEAT_D70A3465D4EE4E9_046141_dump_1st.dmp

- 项目方法测试调用接口工具

- studyupdate

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功