没有合适的资源?快使用搜索试试~ 我知道了~

针对DDR2-800和DDR3的PCB信号完整性设计

温馨提示

试读

14页

主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术

资源推荐

资源详情

资源评论

针对 DDR2-800 和 DDR3 的 PCB 信号完整性设计

摘要

本文章主要涉及到对 DDR2 和 DDR3 在设计印制线路板(PCB)时,考虑信号

完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是

讨论在尽可能少的 PCB 层数,特别是 4 层板的情况下的相关技术,其中一些设

计方法在以前已经成熟的使用过。

1. 介绍

目前,比较普遍使用中的 DDR2 的速度已经高达 800 Mbps,甚至更高的速度,

如 1066 Mbps,而 DDR3 的速度已经高达 1600 Mbps。对于如此高的速度,从

PCB 的设计角度来讲,要做到严格的时序匹配,以满足波形的完整性,这里有

很多的因素需要考虑,所有的这些因素都是会互相影响的,但是,它们之间还

是存在一些个性的,它们可以被分类为 PCB 叠层、阻抗、互联拓扑、时延匹配、

串扰、电源完整性和时序,目前,有很多 EDA 工具可以对它们进行很好的计算

和仿真,其中 Cadence ALLEGRO SI-230 和 Ansoft’s HFSS 使用的比较多。

表 1: DDR2 和 DDR3 要求比较

表 1 显示了 DDR2 和 DDR3 所具有的共有技术要求和专有的技术要求。

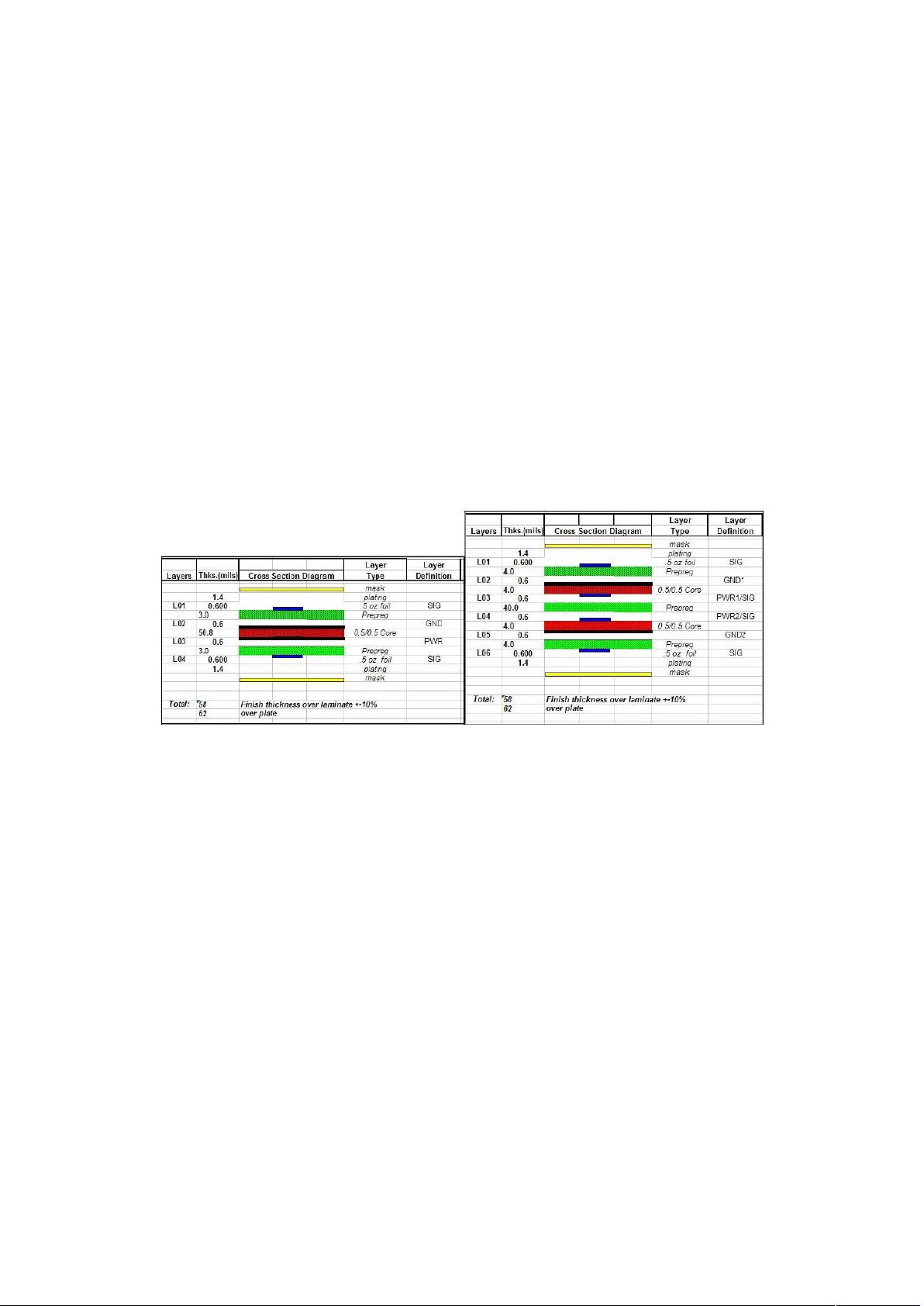

2. PCB 的叠层(stackup)和阻抗

对于一块受 PCB 层数约束的基板(如 4 层板)来说,其所有的信号线只能走在

TOP 和 BOTTOM 层,中间的两层,其中一层为 GND 平面层,而另一层为

VDD 平面层,Vtt 和 Vref 在 VDD 平面层布线。而当使用 6 层来走线时,设计一

种专用拓扑结构变得更加容易,同时由于 Power 层和 GND 层的间距变小了,

从而提高了 PI。

互联通道的另一参数阻抗,在 DDR2 的设计时必须是恒定连续的,单端走线的

阻抗匹配电阻 50 Ohms 必须被用到所有的单端信号上,且做到阻抗匹配,而对

于差分信号,100 Ohms 的终端阻抗匹配电阻必须被用到所有的差分信号终端,

比如 CLOCK 和 DQS 信号。另外,所有的匹配电阻必须上拉到 VTT,且保持

50 Ohms,ODT 的设置也必须保持在 50 Ohms。

在 DDR3 的设计时,单端信号的终端匹配电阻在 40 和 60 Ohms 之间可选择的

被设计到 ADDR/CMD/CNTRL 信号线上,这已经被证明有很多的优点。而且,

上拉到 VTT 的终端匹配电阻根据 SI 仿真的结果的走线阻抗,电阻值可能需要

做出不同的选择,通常其电阻值在 30-70 Ohms 之间。而差分信号的阻抗匹配

电阻始终在 100 Ohms。

图 1 : 四层和六层 PCB 的叠层方式

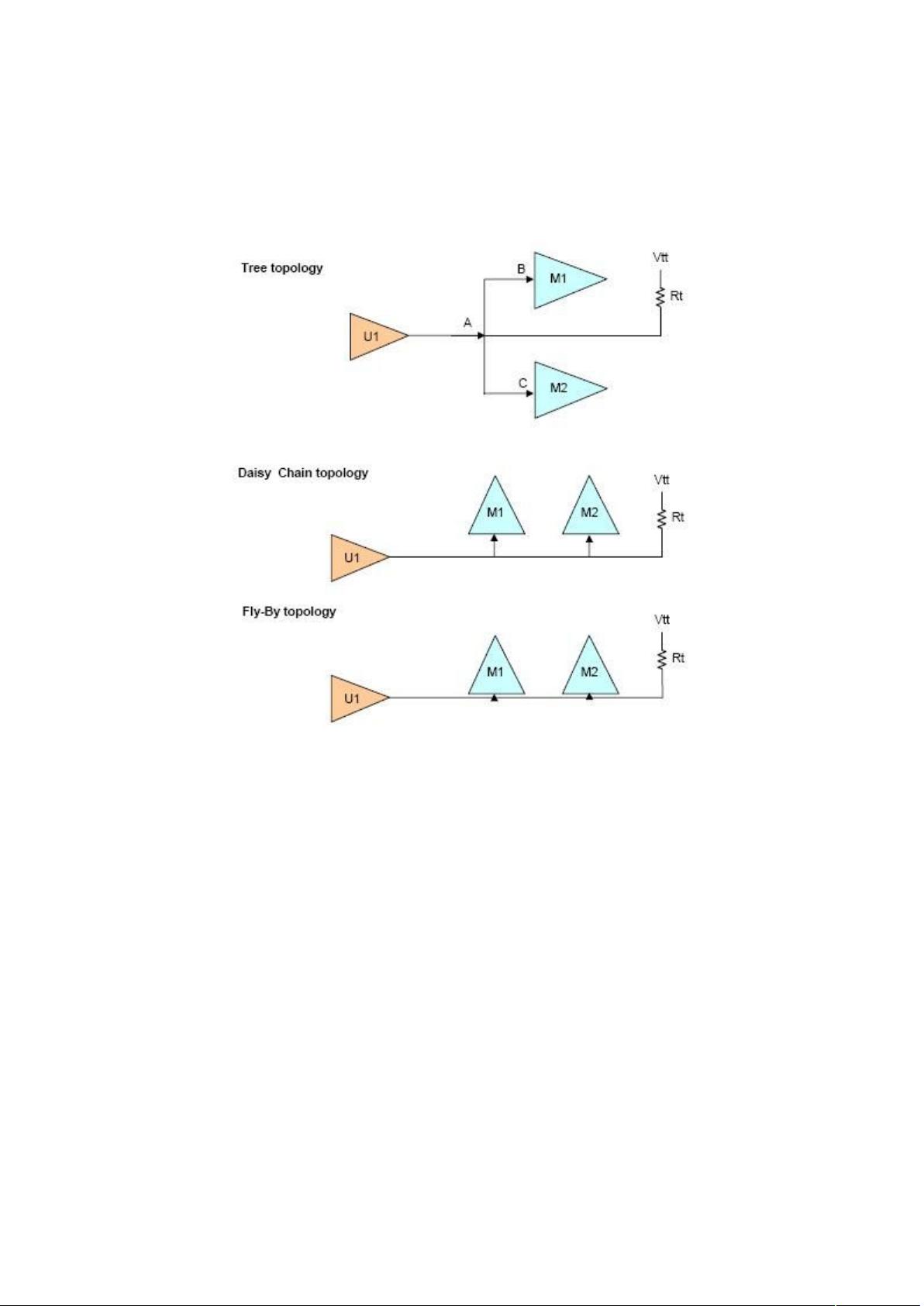

3. 互联通路拓扑

对于 DDR2 和 DDR3,其中信号 DQ、DM 和 DQS 都是点对点的互联方式,所

以不需要任何的拓扑结构,然而列外的是,在 multi-rank DIMMs(Dual In Line

Memory Modules)的设计中并不是这样的。在点对点的方式时,可以很容易

的通过 ODT 的阻抗设置来做到阻抗匹配,从而实现其波形完整性。而对于

ADDR/CMD/CNTRL 和一些时钟信号,它们都是需要多点互联的,所以需要选

择一个合适的拓扑结构,图 2 列出了一些相关的拓扑结构,其中 Fly- By 拓扑结

构是一种特殊的菊花链,它不需要很长的连线,甚至有时不需要短线

(Stub)。

对于 DDR3,这些所有的拓扑结构都是适用的,然而前提条件是走线要尽可能

的短。Fly-By 拓扑结构在处理噪声方面,具有很好的波形完整性,然而在一个

4 层板上很难实现,需要 6 层板以上,而菊花链式拓扑结构在一个 4 层板上是

容易实现的。另外,树形拓扑结构要求 AB 的长度和 AC 的长度非常接近(如图

2)。考虑到波形的完整性,以及尽可能的提高分支的走线长度,同事又要满足

板层的约束要求,在基于 4 层板的 DDR3 设计中,最合理的拓扑结构就是带有

最少短线(Stub)的菊花链式拓扑结构。

对于 DDR2-800,这所有的拓扑结构都适用,只是有少许的差别。然而,菊花

链式拓扑结构被证明在 SI 方面是具有优势的。

对于超过两片的 SDRAM,通常,是根据器件的摆放方式不同而选择相应的拓

扑结构。图 3 显示了不同摆放方式而特殊设计的拓扑结构,在这些拓扑结构中,

只有 A 和 D 是最适合 4 层板的 PCB 设计。然而,对于 DDR2-800,所列的这些

拓扑结构都能满足其波形的完整性,而在 DDR3 的设计中,特别是在 1600

Mbps 时,则只有 D 是满足设计的。

剩余13页未读,继续阅读

资源评论

yingzck2015-10-13非常有用,急需这方面的资源

yingzck2015-10-13非常有用,急需这方面的资源 xiongdazaici2015-12-22挺好的资料,谢谢!

xiongdazaici2015-12-22挺好的资料,谢谢!

lajifm

- 粉丝: 0

- 资源: 14

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功