数字时钟设计实验报告

2008--2009

学年第 一 学期 物电 学院期末考卷

《 EDA

技术及应用》

题目:数字时钟的设计与实现

学号:200672020130 姓名: 聂家宁 班级: 06

级电子信息工程( 1 )

成绩:

评语:

(考试题目及要求)

1. 设计一个数字时钟,具有按秒走时功能,能够分别显示小时

(2 位 24 小时)、分钟(2 位)、秒(2 位)。具有整点报

时 、 时 间 调 整 功 能 。 也 可 设 计 成 十 二 小 时 计 时 方 案

(AM,PM)。具有美观、清晰、人性化的显示界面设计,

走时精度不劣于±3 秒/月。

2. 设计条件:VHDL 语言,MAXPLUSII 开发工具,EPM7128

可编程逻辑芯片,蜂鸣器,20MHz 时钟源,8 位七段数码管,

128X32 像素单色液晶显示屏。

3. 设计报告至少应包含这些内容:系统方案设计、显示界面设

计、程序设计思路,电路设计框图、电路图,选用器件的功

能、性能、使用方法介绍以及接口时序分析,有详细注释的

源程序清单以及程序分析,结果说明与描述(最好附照片)

芯片资源占用率及程序优化度分析,芯片管脚分配与连线说

明,基于时序图的功能仿真分析,在线测试方法、测试数据

与测试结果,走时误差分析与功能、性能偏离分析,设计总

第 0 页 共 20 页 作者:聂家宁

装

订

线

数字时钟设计实验报告

结,参考文献。

数字时钟的设计报告

摘要:根据系统设计的要求,系统设计采用自顶向下的设计方法,可以将该系

统中的各功能模块细分为:秒计数模块、分计数模块、小时计数模块、报警模

块、时间设置模块和译码显示模块六个部分。

关键字:VHDL MAX+plus 七段共阴数码管 报警 设计 总结

正文:

一、 系统方案设计:

本实验采用 6 个八位七段数码管进行显示,具有以 24 小时为循环计时

的时、分、秒计数显示功能。具有整点报时功能和清零功能,且能够对计时

系统的小时、分钟进行调整。

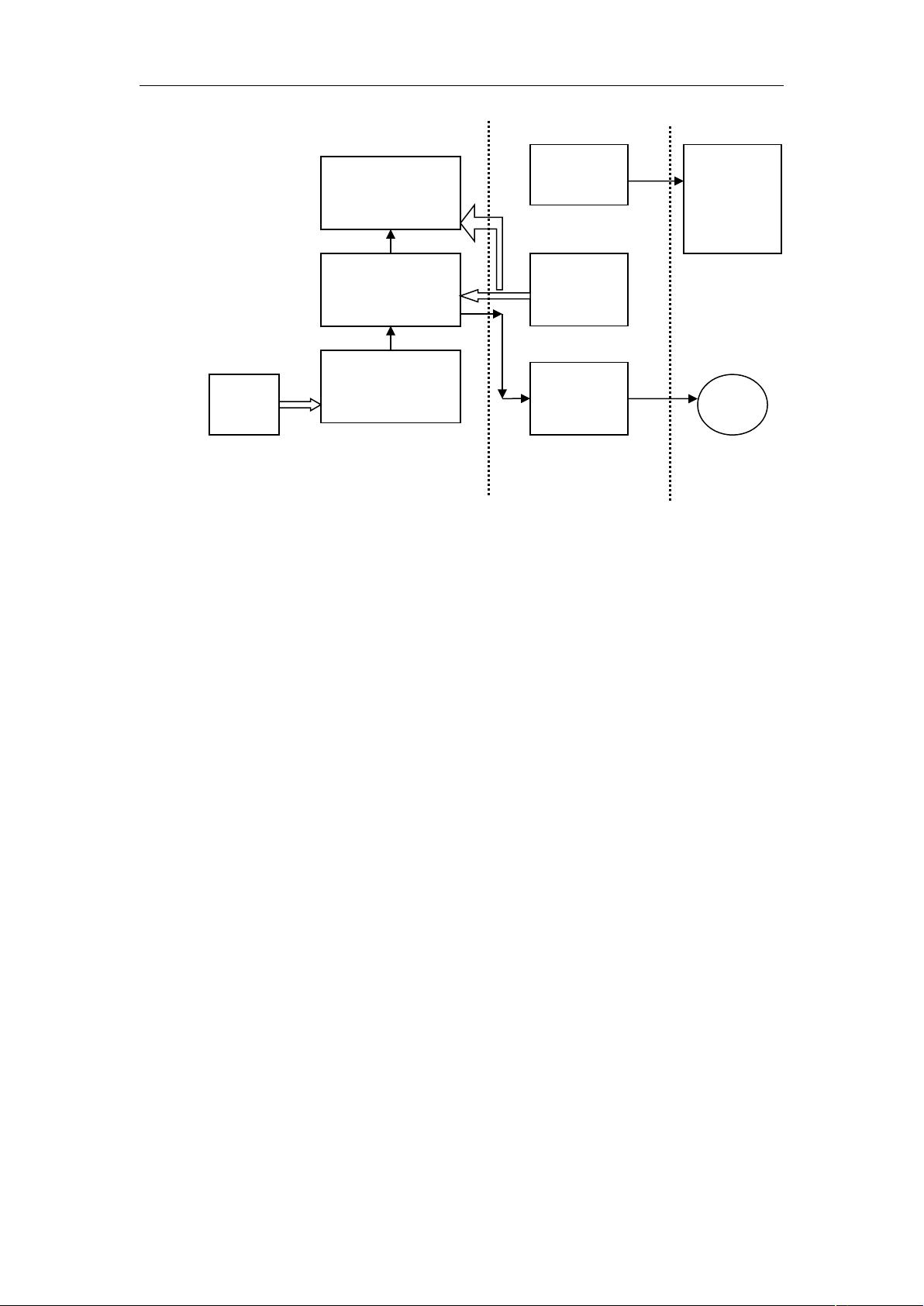

根据系统设计的要求,系统设计采用自顶向下的设计方法,可以将该系

统中的各功能模块细分为:秒计数模块、分计数模块、小时计数模块、报警

模块、时间设置模块和译码显示模块六个部分。先使用 VHDL 语言设计编译

将这每个模块制作成图元,然后再使用图形编辑器进行总体的整合,系统的

整体组装设计草图如下所示:

第 1 页 共 20 页 作者:聂家宁

数字时钟设计实验报告

图 1.系统总体设计草图

现在就先对本系统中最基本的三项内容设计进行阐述:

1. 秒计数模块的 VHDL 程序(MIAO.VHD)

秒计数模块中是以 60 进制进行循环的,故需要的秒数据输出应该是 7 位的

(其中低 4 位用于秒的低位,而高 3 位在作为秒的高位)。

另外在该模块下的程序由于考虑到系统功能中调整时钟和分钟的要求,故要在

秒计数模块中另外加入复位信号以及分钟设置信号。

以下是该模块的 VHDL 源程序

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY MIAO IS

PORT (CLK: IN STD_LOGIC;-------------------系统时钟信号

RESET: IN STD_LOGIC; ------------------系统复位信号

SETMIN: IN STD_LOGIC; --------------------分设置信号

ENMIN: OUT STD_LOGIC;-----------------分计数时钟信号

MOUT: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); ----秒计数值

END MIAO;

ARCHITECTURE ART OF MIAO IS

SIGNAL COUNT :STD_LOGIC_VECTOR(6 DOWNTO 0);---7 位计数器

SIGNAL ENMIN_1,ENMIN_2 :STD_LOGIC ;---前者是整秒进位,后者是调节分钟的信号

BEGIN

MOUT<=COUNT;----将计数器的值直接赋给秒计数

ENMIN_2<=(SETMIN AND CLK);--ENMIN_2 的内容是分设置信号和系统时钟信号的

“与”运算

第 2 页 共 20 页 作者:聂家宁

秒计数器模块

分计数器模块

时计数器模块

译码显示

模块

时间调整

模块

报警模块

7 段

数码管

显示

喇

叭

系统

时钟

基本功能 扩展功能 外部设备

秒高位 进位

分高位 进位

数字时钟设计实验报告

ENMIN<=(ENMIN_1 OR ENMIN_2);----ENMIN 的内容是整秒进位和调节分钟信号的

“或”运算

PROCESS(CLK,RESET,SETMIN)

BEGIN

IF (RESET='0') THEN-----初始化,即系统复位信号的功能

COUNT<="0000000";

ENMIN_1<='0'; -------将整秒的进位置零

ELSIF(CLK'EVENT AND CLK='1') THEN

IF(COUNT(3 DOWNTO 0)="1001") THEN ------1. 若 count 的 低 四位 是

“1001”

IF(COUNT<16#60#) THEN -------------2.并且 count 的值小于 60

IF(COUNT="1011001") THEN -------3.且 count 的值为 59

ENMIN_1<='1';COUNT<="0000000"; ---则 ENMIN_1 置 1,count 清

零

ELSE ------------否则,若只满足条件 1、2

COUNT<=COUNT+7;------则直接向 count 的高 3 位进 1

END IF;

ELSE---------------------------若不满足 count 的值小于 60

COUNT<="0000000";------------则直接将 count 清零

END IF;

ELSIF(COUNT<16#60#) THEN-------若 count 的低四位不满足条件 1,满足

2.

COUNT<=COUNT+1;

ENMIN_1<='0';---------------count 加计数,进位标志字为零

ELSE -------------------------若条件 1、2 均不满足

COUNT<="0000000";ENMIN_1<='0';-----------初始化

END IF;

END IF;

END PROCESS;

END ARCHITECTURE ART;

2. 分计数模块的 VHDL 程序(FEN.VHD)

分计数同秒计数基本相同,由于均是 60 进制的计数器,故思路完全一致。

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY FEN IS

PORT (INMIN: IN STD_LOGIC;-------------------系统时钟信号

RESET: IN STD_LOGIC; ------------------系统复位信号

DIPS: IN STD_LOGIC;-------------------时设置时钟信号

SETHOUR: IN STD_LOGIC; --------------------时设置信号

ENHOUR: OUT STD_LOGIC;-----------------时计数时钟信号

SOUT: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); ----秒计数值

BELL: OUT STD_LOGIC;-----------------时钟报警信号

第 3 页 共 20 页 作者:聂家宁

数字时钟设计实验报告

END ENTITY FEN;

ARCHITECTURE ART OF FEN IS

SIGNAL COUNT :STD_LOGIC_VECTOR(6 DOWNTO 0);

SIGNAL ENHOUR_1,ENHOUR_2 :STD_LOGIC ;--前者是整分进位字,后者是调节时

钟信号

BEGIN

SOUT<=COUNT;

ENHOUR_2<=(SETHOUR AND DIPS);

ENHOUR<=(ENHOUR_1 OR ENHOUR_2);

BELL<=ENHOUR_1;-------------将 ENHOUR_1 信号赋给 BELL

PROCESS(INMIN,RESET,SETHOUR)

BEGIN

IF (RESET='0') THEN

COUNT<="0000000";

ENHOUR_1<='0';

ELSIF(INMIN'EVENT AND INMIN='1') THEN

IF(COUNT(3 DOWNTO 0)="1001") THEN

IF(COUNT<16#60#) THEN

IF(COUNT="1011001") THEN

ENHOUR_1<='1';COUNT<="0000000";

ELSE

COUNT<=COUNT+7;

END IF;

ELSE

COUNT<="0000000";

END IF;

ELSIF(COUNT<16#60#) THEN

COUNT<=COUNT+1;

ENHOUR_1<='0'AFTER 100 NS;

ELSE

COUNT<="0000000";ENHOUR_1<='0';

END IF;

END IF;

END PROCESS

END ARCHITECTURE ART;

此源程序不须再作过多解释,只有一点需要注意的:报警信号 BELL 的如

何获取,本来构思时把报警作为一个单独的功能模块来处理,可是在编程实验

程序,以及具体的调试中发现 BELL 作为整点报时的信号,其功能与分钟计数

中的 ENHOUR_1 是完全相同的,故只需将 BELL 放在分钟模块中一起进行处

理。即将 ENHOUR_1 的值赋给了 BELL.

3. 时计数模块的 VHDL 程序(SHI.VHD)

LIBRARY IEEE ;

第 4 页 共 20 页 作者:聂家宁