S3C2440A RISC MICROPROCESSOR ARM INSTRUCTION SET

3-1

3 ARM INSTRUCTION SET

INSTRUCTION SET SUMMAY

This chapter describes the ARM instruction set in the ARM920T core.

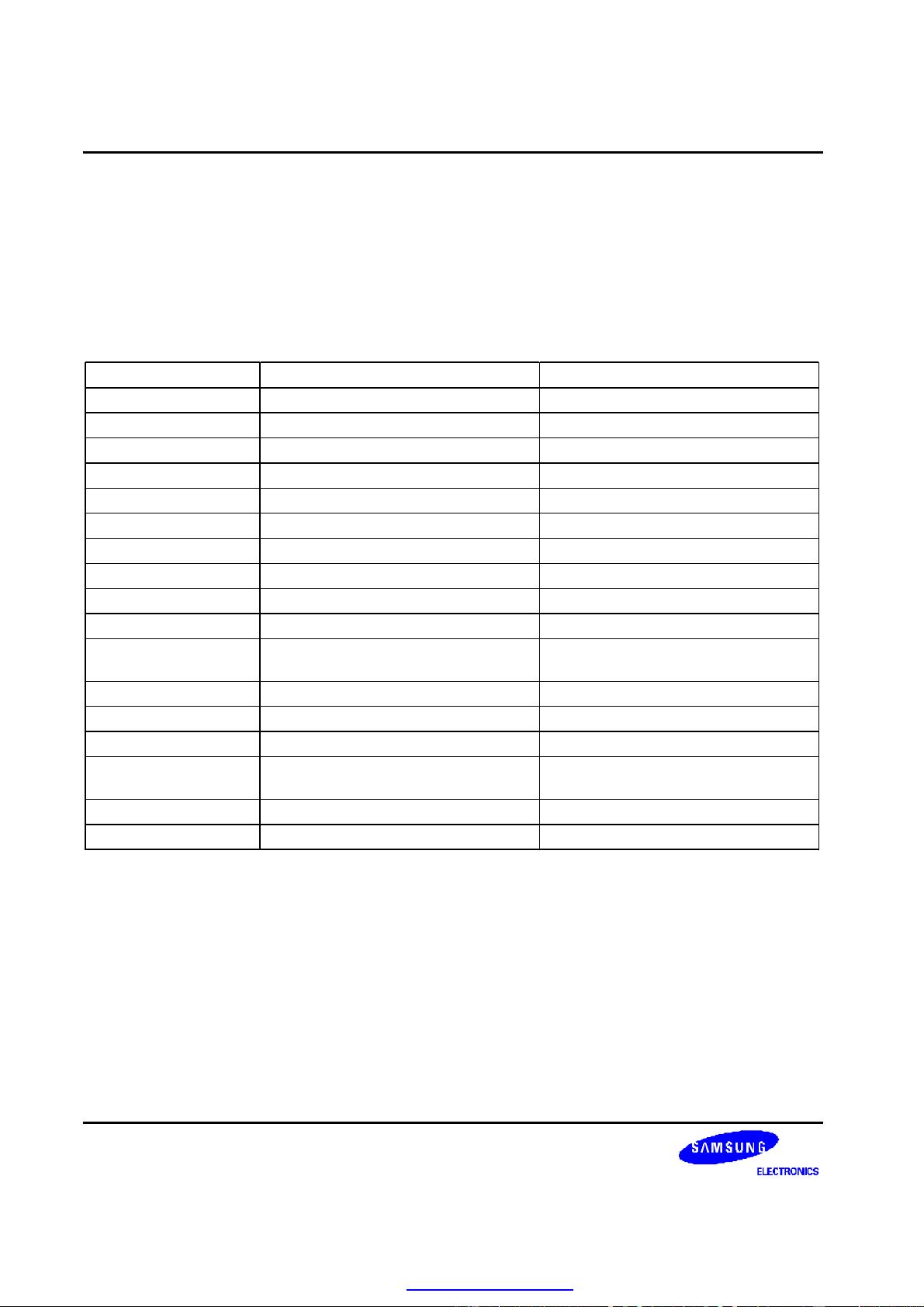

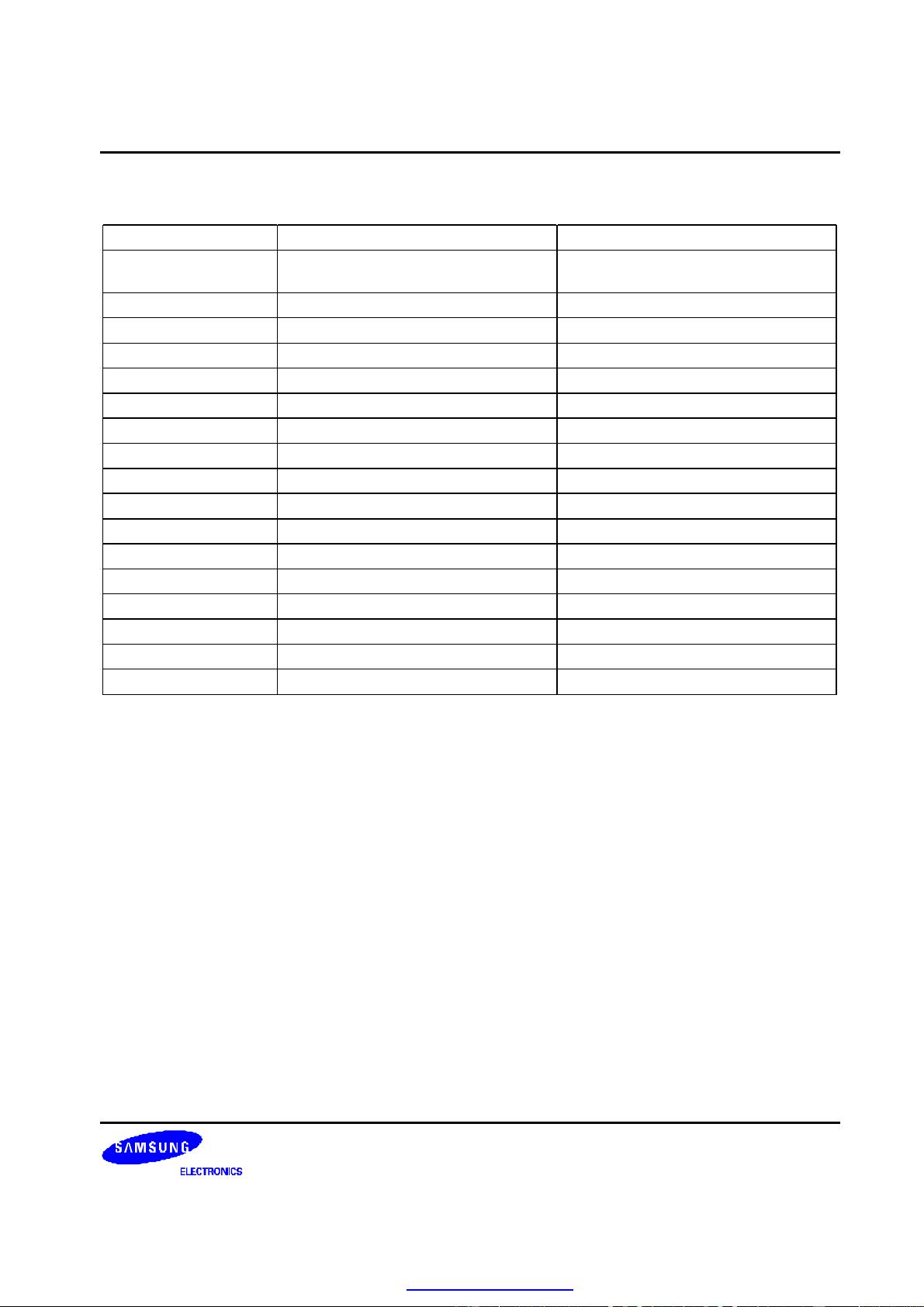

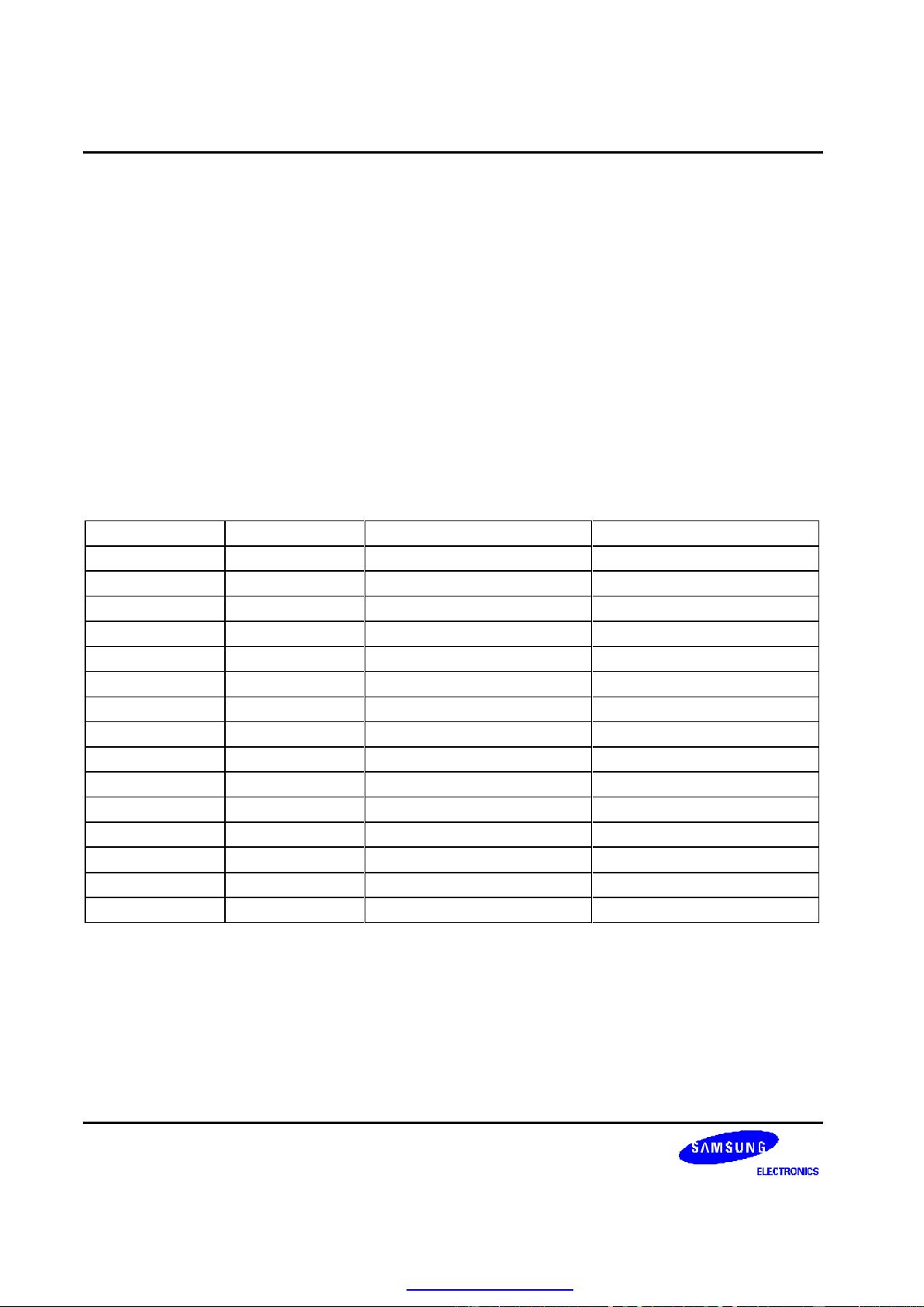

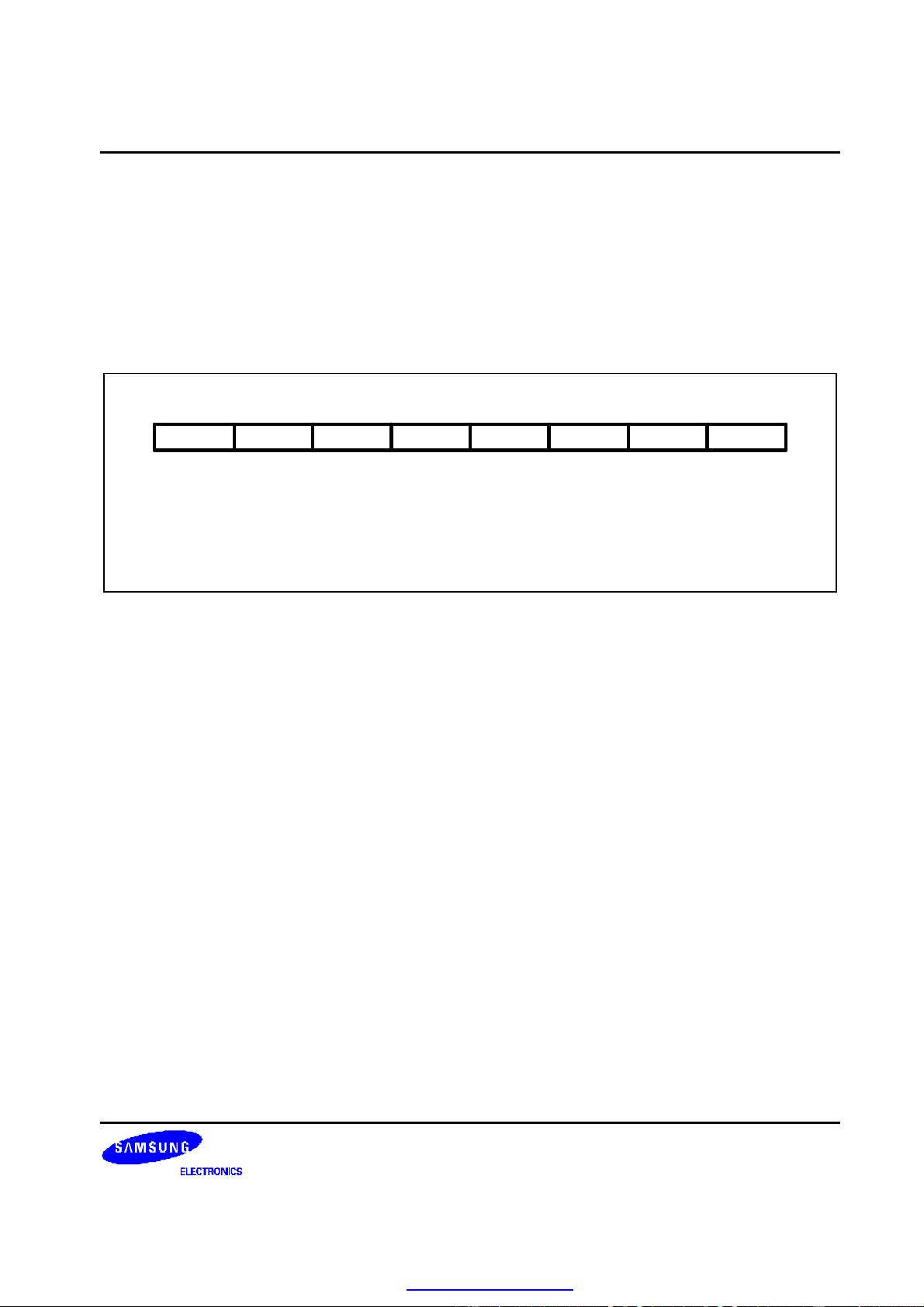

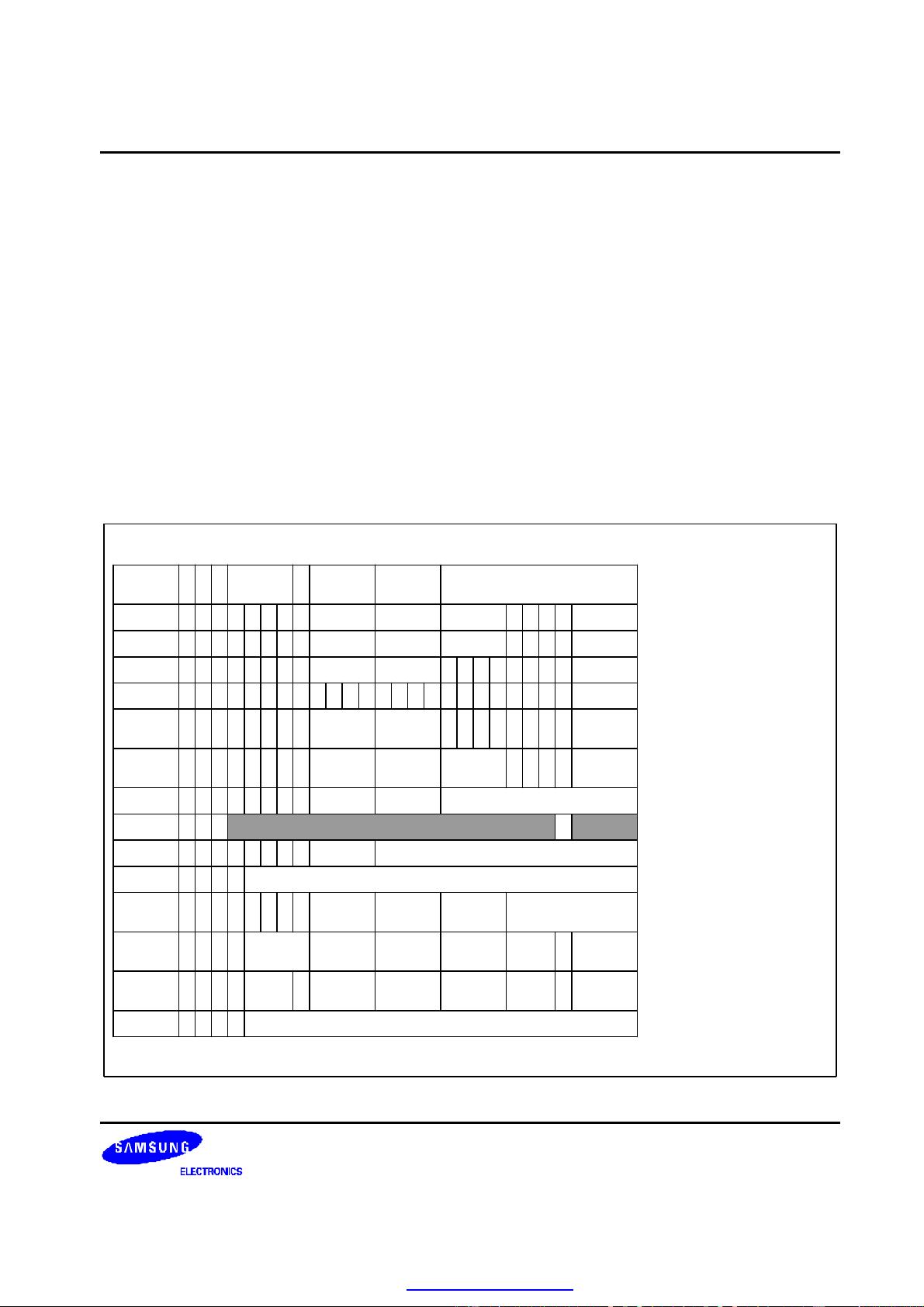

FORMAT SUMMARY

The following figure shows the ARM instruction set.

Cond Rn Data/Processing/

PSR Transfer

0 0 I S

Opcode

000PU0WL

000PU1WL

01IPUBWL

01I

100PUBWL

11 11 1 1 11

10 L1

110PUBWL

11 11

11 01

11 01 L

Rd

Rd

RnRdHi RdLo

Rn

Rn

Rn

Rn

Rd

Rd

Rd

Rn Register List

Rn

CRn

CRn

CRd

Rd

CP Opc

CP

Opc

Operand2

Rs

Rm

Rm

Rm

Rm

Rn

Rn

Rd

Offset Offset

CRd OffsetCP#

CP#

CP#

CP

CP

CRm

CRm

Ignored by processor

0

1

Offset

Cond

Cond

Cond

Cond

Cond

Cond

Cond

Cond

Cond

Cond

Cond

Cond

Cond

Cond

0000 00 AS

ASU100 00

000 0 001 B

1 00 01000

1

1

1

1

1

1

0

0

0

0

H

H

0

0

0

0

S

S

1

1

1

0

1

1

1

0

0

1

0

0

1

0

0

1

0

0

1

Multiply

Multiply Long

Single Data Swap

Branch and Exchange

Halfword Data Transfer:

register offset

Halfword Data Transfer:

immendiate offset

Single Data Transfer

Undefined

Block Data Transfer

Branch

Coprocessor Register Transfer

Coprocessor Data Operation

Coprocessor Data Transfer

Software Interrupt

Offset

272625242322212019181716151314121110 313029289876543210

272625242322212019181716151314121110 313029289876543210

Figure 3-1. ARM Instruction Set Format

PDF created with pdfFactory Pro trial version www.pdffactory.com