USER'S MANUAL

S3C6410X

RISC Microprocessor

February 29, 2008

Preliminary REV 0.00

Confidential Proprietary of Samsung Electronics Co., Ltd

Copyright © 2008 Samsung Electronics, Inc. All Rights Reserved

Important Notice

The information in this publication has been carefully

checked and is believed to be entirely accurate at

the time of publication. Samsung assumes no

responsibility, however, for possible errors or

omissions, or for any consequences resulting from

the use of the information contained herein.

Samsung reserves the right to make changes in its

products or product specifications with the intent to

improve function or design at any time and without

notice and is not required to update this

documentation to reflect such changes.

This publication does not convey to a purchaser of

semiconductor devices described herein any license

under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or

guarantee regarding the suitability of its products for

any particular purpose, nor does Samsung assume

any liability arising out of the application or use of

any product or circuit and specifically disclaims any

and all liability, including without limitation any

consequential or incidental damages.

"Typical" parameters can and do vary in different

applications. All operating parameters, including

"Typicals" must be validated for each customer

application by the customer's technical experts.

Samsung products are not designed, intended, or

authorized for use as components in systems

intended for surgical implant into the body, for other

applications intended to support or sustain life, or for

any other application in which the failure of the

Samsung product could create a situation where

personal injury or death may occur.

Should the Buyer purchase or use a Samsung

product for any such unintended or unauthorized

application, the Buyer shall indemnify and hold

Samsung and its officers, employees, subsidiaries,

affiliates, and distributors harmless against all

claims, costs, damages, expenses, and reasonable

attorney fees arising out of, either directly or

indirectly, any claim of personal injury or death that

may be associated with such unintended or

unauthorized use, even if such claim alleges that

Samsung was negligent regarding the design or

manufacture of said product.

S3C6410X RISC Microprocessor

User's Manual, Preliminary Revision 0.00

Copyright © 2008 Samsung Electronics Co.,Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in

any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior

written consent of Samsung Electronics Co.,Ltd.

Samsung Electronics Co., Ltd.

San #24 Nongseo-Dong, Giheung-Gu

Yongin-City Gyeonggi-Do, Korea

446-711

Home Page: http://www.samsungsemi.com/

E-Mail: mobilesol.cs@samsung.com

Printed in the Republic of Korea

S3C6410X_USER’S MANUAL_PRELIMINARY_REV 0.00 iii

Revision History

Revision No Description of Change Refer to Author(s) Date

0.00 - Initial Release (Preliminary) - W.J.Kim February 29, 2008

NOTE: Revised parts are written in blue.

S3C6410X_UM_REV0.00 PRODUCT OVERVIEW

1-1

Preliminary product information describe products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1 PRODUCT OVERVIEW

1 ARCHITECTURAL OVERVIEW

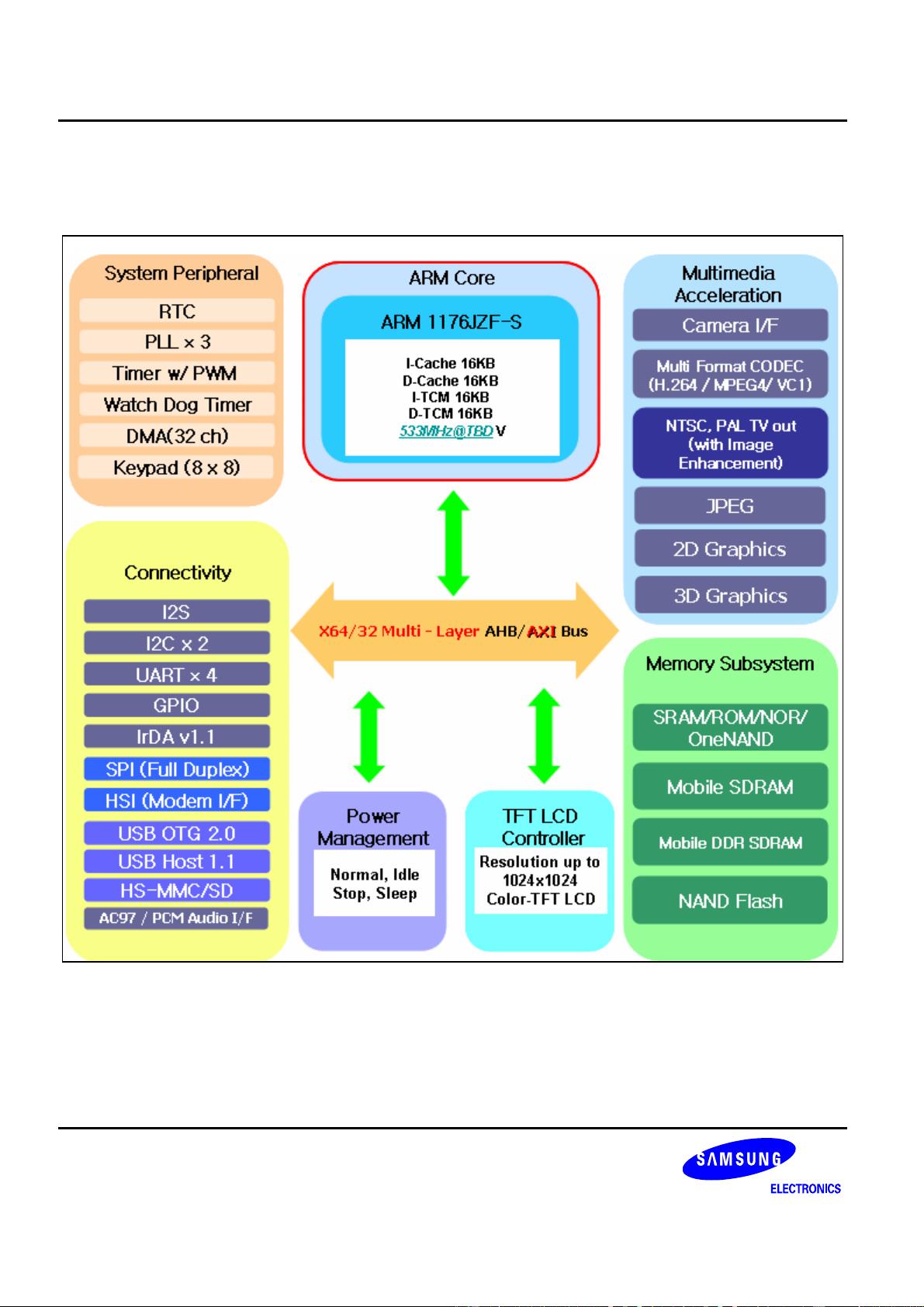

The S3C6410X is a 16/32-bit RISC microprocessor, which is designed to provide a cost-effective, low-power

capabilities, high performance Application Processor solution for mobile phones and general applications. To

provide optimized H/W performance for the 2.5G & 3G communication services, the S3C6410 adopts 64/32-bit

internal bus architecture. The 64/32-bit internal bus architecture is composed of AXI, AHB and APB buses. It also

includes many powerful hardware accelerators for tasks such as motion video processing, audio processing, 2D

graphics, display manipulation and scaling. An integrated Multi Format Codec (MFC) supports encoding and

decoding of MPEG4/H.263/H.264 and decoding of VC1. This H/W Encoder/Decoder supports real-time video

conferencing and TV out for both NTSC and PAL mode. Graphic 3D (hereinafter 3D Engine) is a 3D Graphics

Hardware Accelerator which can accelerate OpenGL ES 1.1 & 2.0 rendering. This 3D Engine includes two

programmable shaders: one vertex shader and one pixel shader.

The S3C6410 has an optimized interface to external memory. This optimized interface to external memory is

capable of sustaining the high memory bandwidths required in high-end communication services. The memory

system has dual external memory ports, DRAM and Flash/ROM/DRAM port. The DRAM port can be configured to

support mobile DDR, DDR, mobile SDRAM and SDRAM. The Flash/ROM/DRAM port supports NOR-Flash,

NAND-Flash, OneNAND, CF, ROM type external memory and mobile DDR, DDR, mobile SDRAM and SDRAM.

To reduce total system cost and enhance overall functionality, the S3C6410 includes many hardware peripherals

such as a Camera Interface, TFT 24-bit true color LCD controller, System Manager (power management & etc.),

4-channel UART, 32-channel DMA, 4-channel Timers, General Purpose I/O Ports, I2S-Bus interface, I2C-BUS

interface, USB Host, USB OTG Device operating at high speed (480Mbps), 3-channel SD/MMC Host Controller

and PLLs for clock generation.

The ARM subsystem is based on the ARM1176JZF-S core. It includes separate 16KB Instruction and 16KB data

caches, 16KB Instruction and 16KB Data TCM. It also includes a full MMU to handle virtual memory management.

The ARM1176JZF-S is a single chip MCU, which includes support for JAVA acceleration. The ARM1176JZF-S

includes a dedicated vector floating point coprocessor allowing efficient implementation of various encryption

schemes as well as high quality 3D graphics applications. The S3C6410X adopts the de-facto standard AMBA

bus architecture. These powerful, industry standard features allow the S3C6410X to support many of the industry

standard Operating Systems.

By providing a complete set of common system peripherals, the S3C6410X minimizes overall system costs and

eliminates the need to configure additional components. The S3C6410X is implemented using an advanced 90nm

CMOS process. The low-power, simple, elegant and fully static-design scheme is particularly suitable for cost-

sensitive and power-sensitive applications.

PRODUCT OVERVIEW S3C6410X_UM_REV0.00

1-2

Preliminary product information describe products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1.1 FEATURES

This section summarizes the features of the S3C6410. Figure 1-1 is an overall block diagram of the S3C6410X.

Figure 1-1 S3C6410 Block Diagram