没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

第 4 章 嵌入式设备

SOPC 包括可以在 Altera 可编程逻辑中实现的标准嵌入式外围设备库,Altera 提供给用

户这些设备的 Verilog HDL 或 VHDL 源代码以及所有系统综合需要的软件程序。

SOPC 包括的嵌入式设备有:

■ 微控制器设备

● PIO

● Timer

■ 串行通信设备

● JTAG UART

● UART

● SPI

■ 显示设备

● LCD 控制器

■ 存储设备

● SDRAM 控制器

● CFI 控制器

● EPCS 控制器

● DMA 控制器

■ 多处理器协调设备

● Mutex

● Mailbox

■ 其他存储器映像设备

● System ID

● PLL(锁相环)

● Performance Counter(性能计数器)

这些 SOPC Builder 组件有在 Nios II 开发板上定义器件逻辑和接口信号可用的系统选择

可在 SOPC Builder MegaWizard 或系统外围设备模板文件(PTF)中配置。

一个完整的系统可以包含许多嵌入式设备,数量只受目标器件容量的限制。

4.1 PIO

PIO(并行输入/输出)在 Avalon Memory-Mapped(Avalon-MM:Avalon 存储器映像)

从属设备端口和通用 I/O 端口之间提供存储器映像接口,I/O 端口连接片内用户逻辑和连接

到 FPGA 外部设备的 I/O 引脚。

PIO 提供到用户逻辑或外部设备的 I/O 访问,如:

■ 控制 LED;

■ 从开关获得数据;

·1·

■ 控制显示设备;

■ 配置片外设备,如特定应用标准产品(ASSP)。

PIO 的中断请求(IRQ)输出可以根据输入信号产生中断。PIO 包含在 SOPC Builder 中,

可以容易地集成到任何 SOPC Builder 生成系统中。

4.1.1 PIO 功能说明

每个 PIO 可提供多达 32 个 I/O 端口,智能主机(例如微处理器)通过读写 Avalon-MM

接口控制 PIO 端口,在主机的控制之下,PIO 在输入端捕捉数据,在输出端输出数据。当

PIO 端口直接连接到 I/O 引脚时,主机可以通过写 PIO 中的控制寄存器使引脚处于三态。

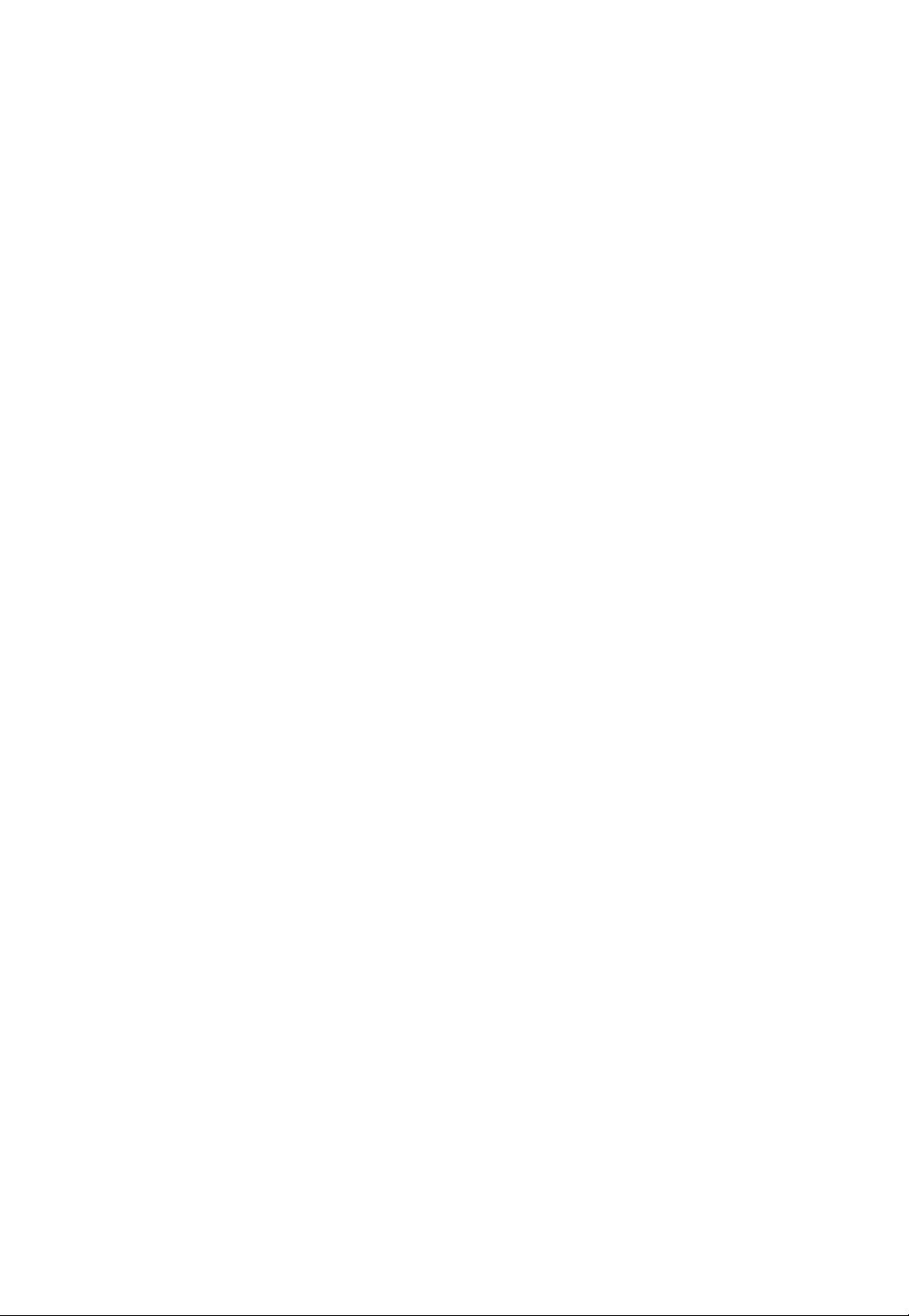

使用多个 PIO 的范例系统如图 4.1 所示,其中使用多个 PIO 连接 LED、从片内复位请求

逻辑捕捉边沿并控制片外 LCD 显示器。

图 4.1 使用多个 PIO 的范例系统

当把 PIO 集成到 SOPC Builder 生成系统时,PIO 有两个用户可见部分:

■ 4 个存储器映像寄存器:data(数据)、direction(方向)、interruptmask(中断屏蔽)

和 edgecapture(边沿捕捉);

■ 1-32 个 I/O 端口。

I/O 端口可以连接 FPGA 片内逻辑和连接到片外设备的 I/O 引脚,寄存器提供连接到 I/O

端口的接口并通过 Avalon-MM 接口进行访问。

有些寄存器在某些硬件配置中不需要,此时不需要的寄存器不存在 ,读不存在的寄存

器返回未定义值,写不存在的寄存器无效。

1.数据输入和输出

PIO 的 I/O 端口可以连接片内或片外逻辑,可以配置为输入、输出或输入/输出。如果用

于控制设备上的双向 I/O 引脚,PIO 还提供带三态控制的双向模式。

·2·

FPGA

IRQ

边沿

捕捉

PIO

(输入)

CPU

系统互连结构总线

PIO

(输出)

复位请求逻辑

存储器

PIO

(双向)

LED

LCD

读和写数据寄存器的硬件逻辑是独立的,读数据寄存器返回输入端口上的值,写数据

寄存器影响输出端口上的值。输入和输出端口是独立的,读数据寄存器不返回以前写的数

据。

2.边沿捕捉

PIO 可以配置为捕捉输入端口上的边沿,可以捕捉低到高转换、高到低转换或两者都捕

捉,每当输入检测到边沿,在边沿捕捉寄存器中将会有指示,检测边沿的类型在系统生成

时指定,不能通过寄存器改变。

3.IRQ 产生

PIO 可以配置为在某些输入条件下产生中断请求。

中断请求产生的条件可以是:

■ 电平有效:PIO 硬件可以检测高电平,通过非门可以检测低电平;

■ 边沿有效:边沿捕捉配置确定引起中断请求的边沿类型。

每个输入端口的中断可以分别屏蔽,中断屏蔽确定可以产生中断的输入端口。

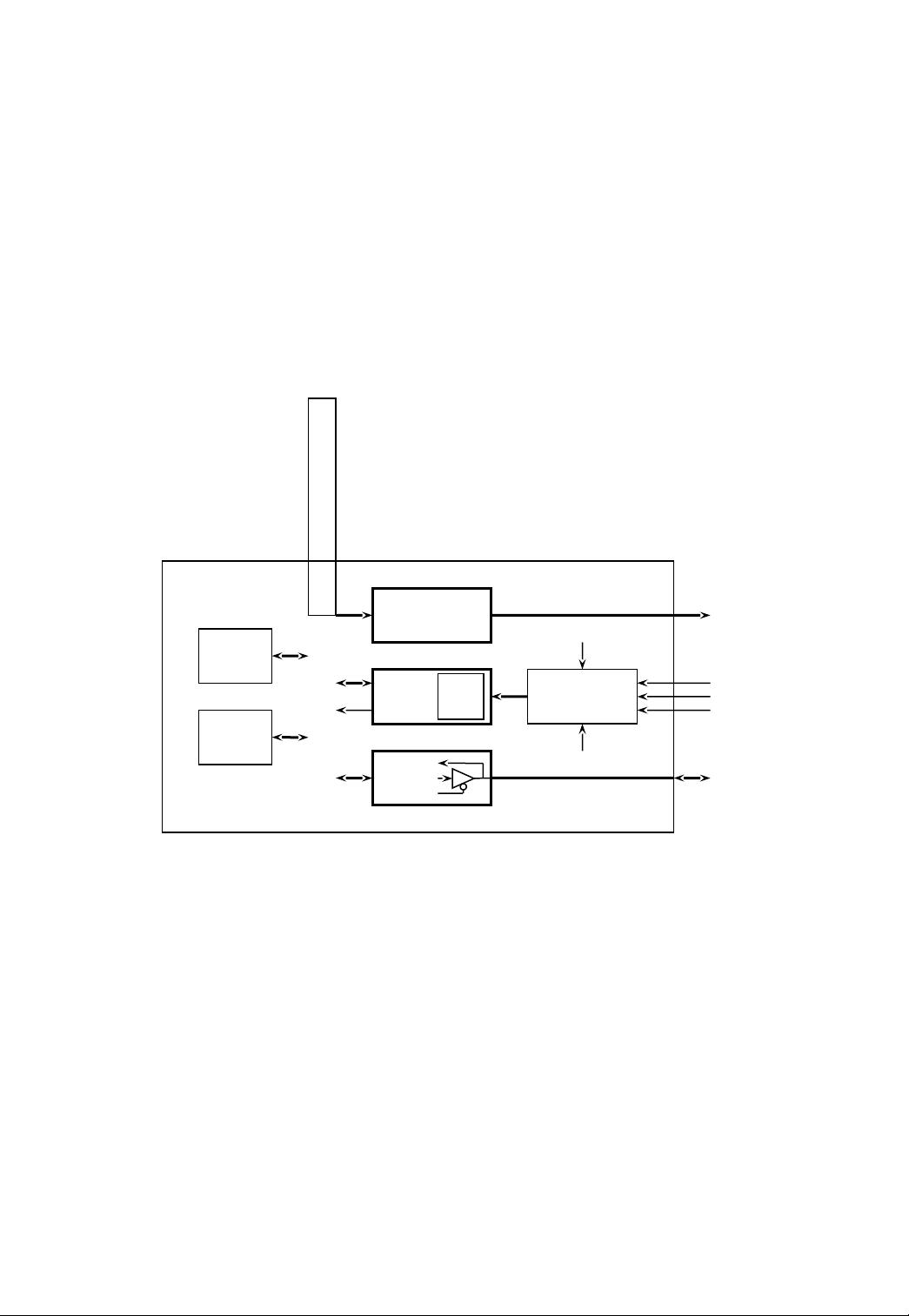

4.范例配置

PIO 配置为带中断支持的输入/输出端口的方框图如图 4.2 所示。

图 4.2 带中断支持的输入/输出端口

PIO 配置为不支持中断的双向端口的方框图如图 4.3 所示。

图 4.3 双向端口

5.Avalon-MM 接口

PIO 的 Avalon-MM 接口包含单个 Avalon-MM 从属设备端口,能够进行基本的 Avalon-

MM 读写传输,Avalon-MM 从属设备端口提供中断请求信号以便产生中断。

6.器件支持

PIO 支持所有的 Altera FPGA 系列。

4.1.2 PIO 硬件配置

·3·

address

data

control

data in

out

interruptmask

edgecapture

片内逻辑

Avalon-MM

从属设备

接口

IRQ

data in

out

direction

片内逻辑

Avalon-MM

从属设备

接口

address

data

control

PIO 的硬件功能通过 PIO 的 SOPC Builder 配置向导进行配置,PIO 配置向导主要有两个

标签:Basic Settings(基本设置)和 Input Options(输入选项), Simulation(仿真)标签

只在对硬件进行仿真时使用。

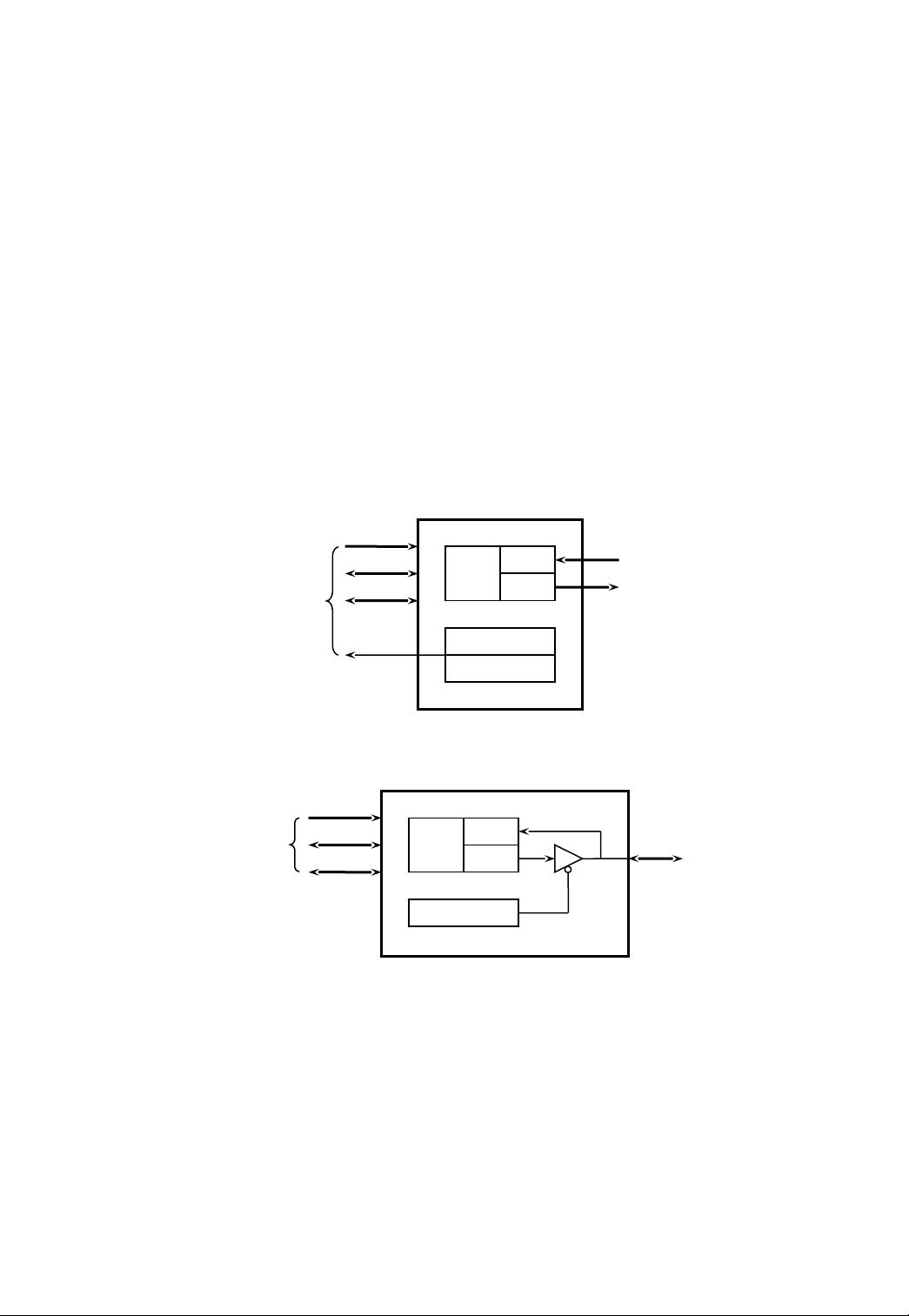

1.基本设置

基本设置标签如图 4.4 所示,用于指定 I/O 端口的 Width(宽度)和 Direction(方向)。

(1)宽度设置

宽度设置可以是 1-32 之间的任何整数值。

图 4.4 PIO 配置向导的基本设置标签

(2)方向设置

方向设置有 4 个选项,如表 4.1 所示。

表 4.1 方向设置

设 置 说 明

Bidirectional (tristate) ports

(双向(三态)端口)

每个 PIO 位共用一个输入/输出设备引脚,每个引脚的方向可单独选择。

为了三态 I/O 引脚,设置引脚方向为输入

Input ports only(输入端口) PIO 端口可以捕捉输入

Output ports only ( 输 出 端

口)

PIO 端口可以驱动输出

Both input and output ports

(输入/输出端口)

输入和输出端口总线独立,相当于输入端口和输出端口的合成。和输入/

输出端口不同,双向(三态)端口公用设备引脚,方向可单独选择

2.输入选项

输 入 选 项 标 签 如 图 4.5 所 示 , 用 于 Edge Capture Register ( 边 沿 捕 捉 寄 存 器 ) 和

Interrupt(中断)设置。当在基本设置标签中选择 Output ports only 时输入选项标签不可用。

·4·

(1)边沿捕捉寄存器设置

当选中 Synchronously capture(同步捕捉)选项时 PIO 包含边沿捕捉(edgecapture)寄

存器,此时必须指定检测的边沿类型:

■ Rising Edge(上升沿)

■ Falling Edge(下降沿)

■ Either Edge(任一边沿)

当指定类型的边沿在输入端口出现时,边沿捕捉寄存器给出指示,并在允许中断的情

况下产生中断。

图 4.5 PIO 配置向导的输入选项标签

当不选中 Synchronously capture 选项时边沿捕捉寄存器不存在。

(2)中断设置

当选中 Generate IRQ(生成 IRQ)选项并且在输入端口出现指定事件时 PIO 产生中断输

出,此时必须指定中断事件的原因:

■ Level(电平):每当特定输入是高电平并且在中断屏蔽(interruptmask)寄存器中允

许该输入中断时 PIO 产生中断;

■ Edge(边沿):每当边沿捕捉寄存器的特定位是 1 并且在中断屏蔽寄存器中允许该位

中断时 PIO 产生中断。

当不选中 Generate IRQ 选项时中断屏蔽寄存器不存在。

4.1.3 PIO 软件编程

PIO 的软件编程模型包括访问硬件的寄存器和软件结构。对于 Nios II 处理器用户,

Altera 提供定义 PIO 寄存器的 HAL 系统库头文件。

·5·

剩余40页未读,继续阅读

桃花心木9629

- 粉丝: 6

- 资源: 13

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

- 1

- 2

- 3

- 4

- 5

前往页