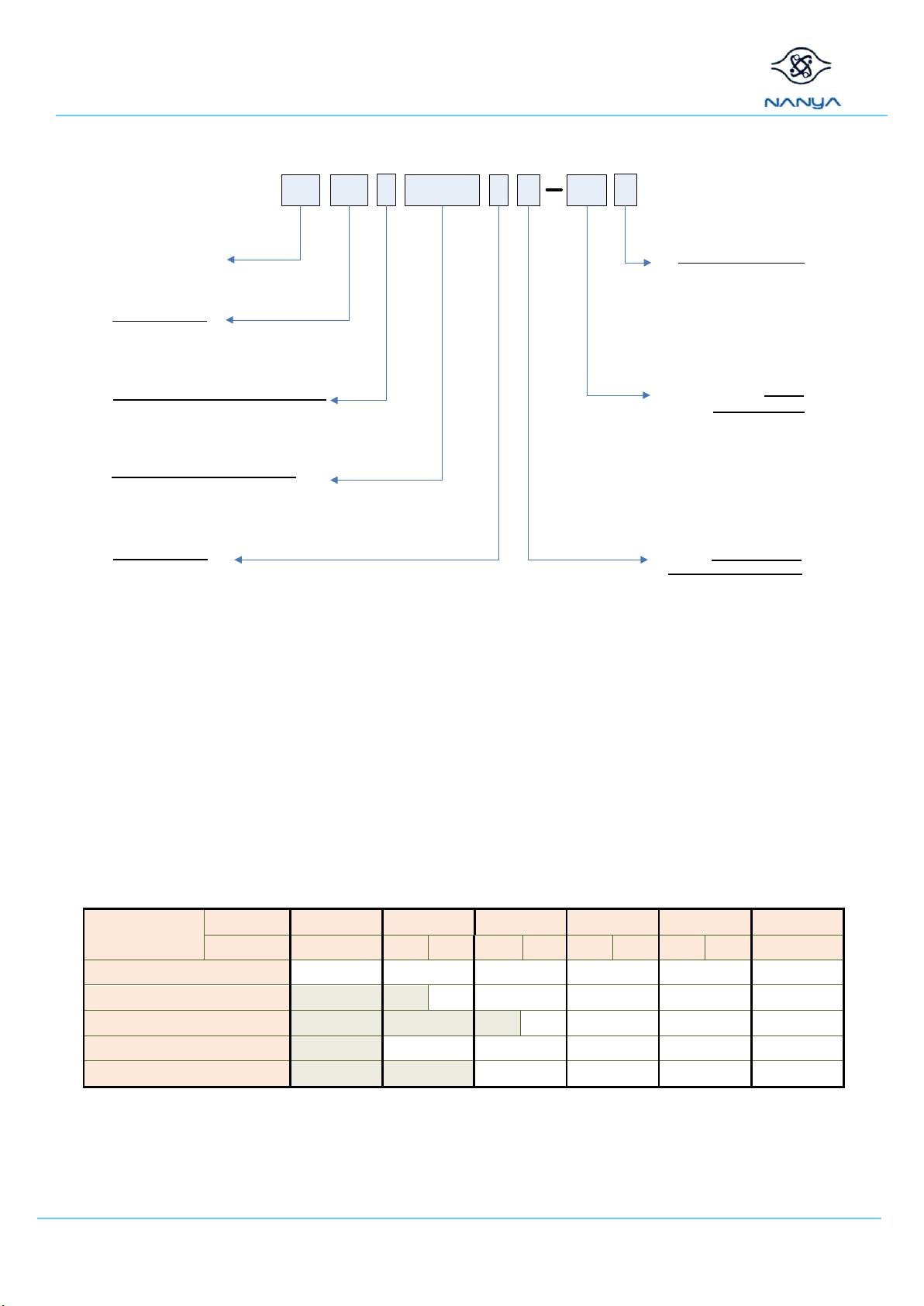

The 4Gb Double-Data-Rate-3 (DDR3(L)) DRAM is a high-speed CMOS SDRAM containing 4,294,967,296 bits. It is internally configured as an octal-bank DRAM. The 4Gb chip is organized as 64Mbit x 8 I/O x 8 banks and 32Mbit x16 I/O x 8 banks. These synchronous devices achieve high speed double-data-rate transfer rates of up to 2133 Mb/sec/pin for general applications. The chip is designed to comply with all key DDR3(L) DRAM key features and all of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and falling). All I/Os are synchronized with a single ended DQS or differential DQS pair in a source synchronous fashion. These devices operate with a single 1.5V ± 0.075V or 1.35V -0.067V/+0.1V power supply and are available in BGA packages.

剩余160页未读,继续阅读

- 粉丝: 2

- 资源: 8

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 什么是移动应用开发-关于移动应用开发的相关介绍

- 第二组汇报 PPT.pptx

- 什么是大数据开发-相关介绍-关于大数据开发的相关介绍

- 什么是软件测试-相关介绍-关于软件测试的相关介绍

- 前端开发-什么是前端开发-关于前端开发的一些相关介绍

- Sora AI-关于文生视频的使用场景说明

- suno AI文生视频的相关教程和介绍使用

- 什么是后端开发-关于后端开发的一些小介绍分享

- Jurassic Pack Vol. II Dinosaurs 侏罗纪包卷恐龙二号Unity游戏模型资源unitypackage

- Jurassic Pack Vol. III Dinosaurs 侏罗纪包卷恐龙三号Unity游戏模型资源unitypackag

信息提交成功

信息提交成功