课程实验报告

课程名称 EDA 技术与应用 班级 通信 164 实验日期

2018.10.2

0

姓名 吴勃 学号

2016272

56

实验成绩

实验名称 实验 2:一位半减器和一位全减器的设计

实

验

目

的

及

原

理

1.学习使用 Quartus II 系统

2.了解一位半减器和一位全减器的工作原理以及如何设计一位半减

器和一位全减器

3.用 VHDL 语言设计一个一位半减器和一位全减器

4.学会进行功能仿真和时序仿真

5. 一位半减器的工作原理是:输入减数和被减数,输出差和借位

6. 一位全减器的工作原理是:输入减数、被减数和低位来的借位,

输出差和借位

实

验

环

境

Quartus II 9.0

实

验

步

骤

1.启动 Quartus 系统

2.新建一个 project 命名为 h_suber

3.选择目标器件 Cyclone II 系列

4.建立一个 VHDL 文件,输入源程序并检查错误

5.进行元件例化操作

6.编译并修改语法错误

7.建立一个“Vector Wavefrom File”文件

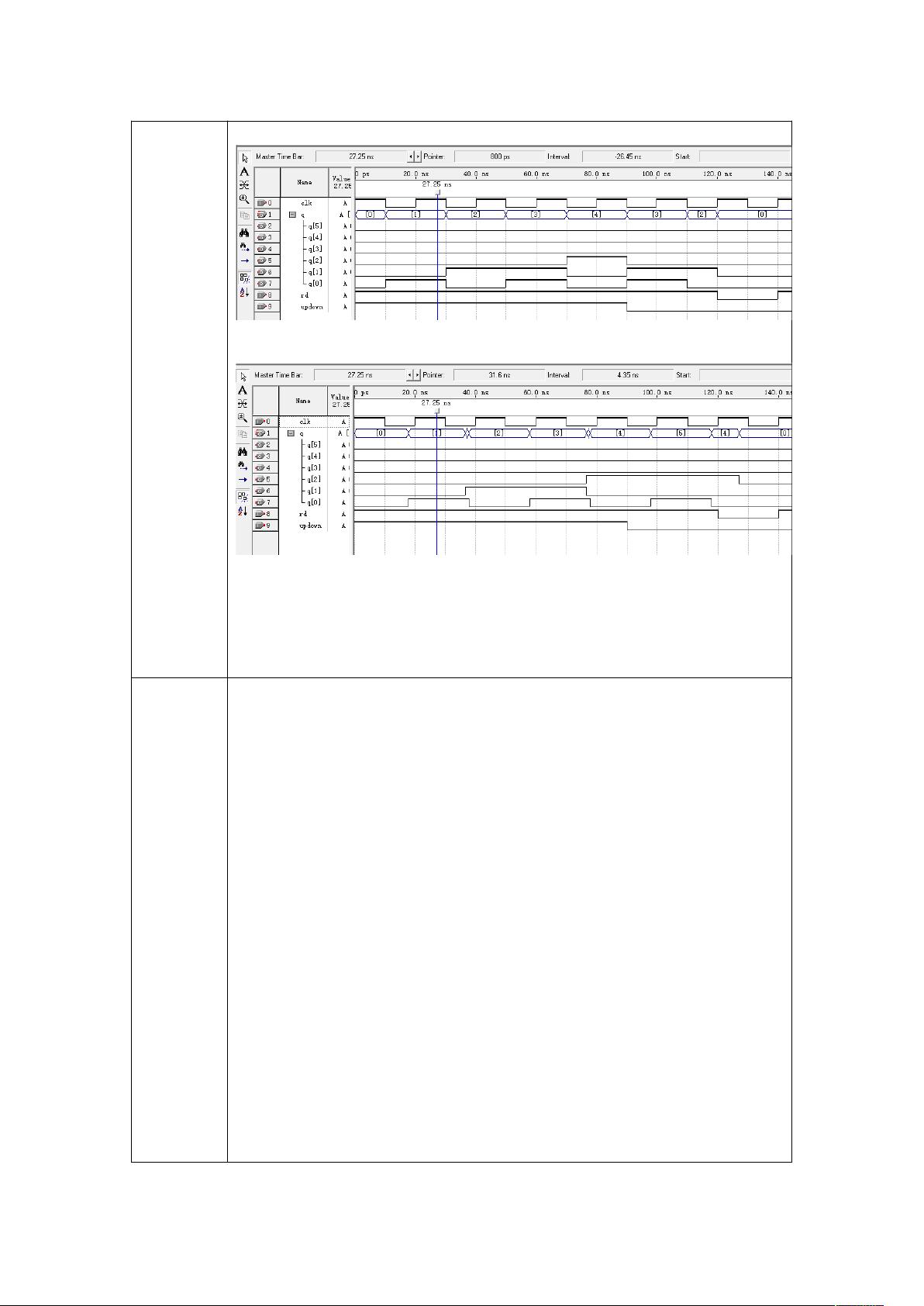

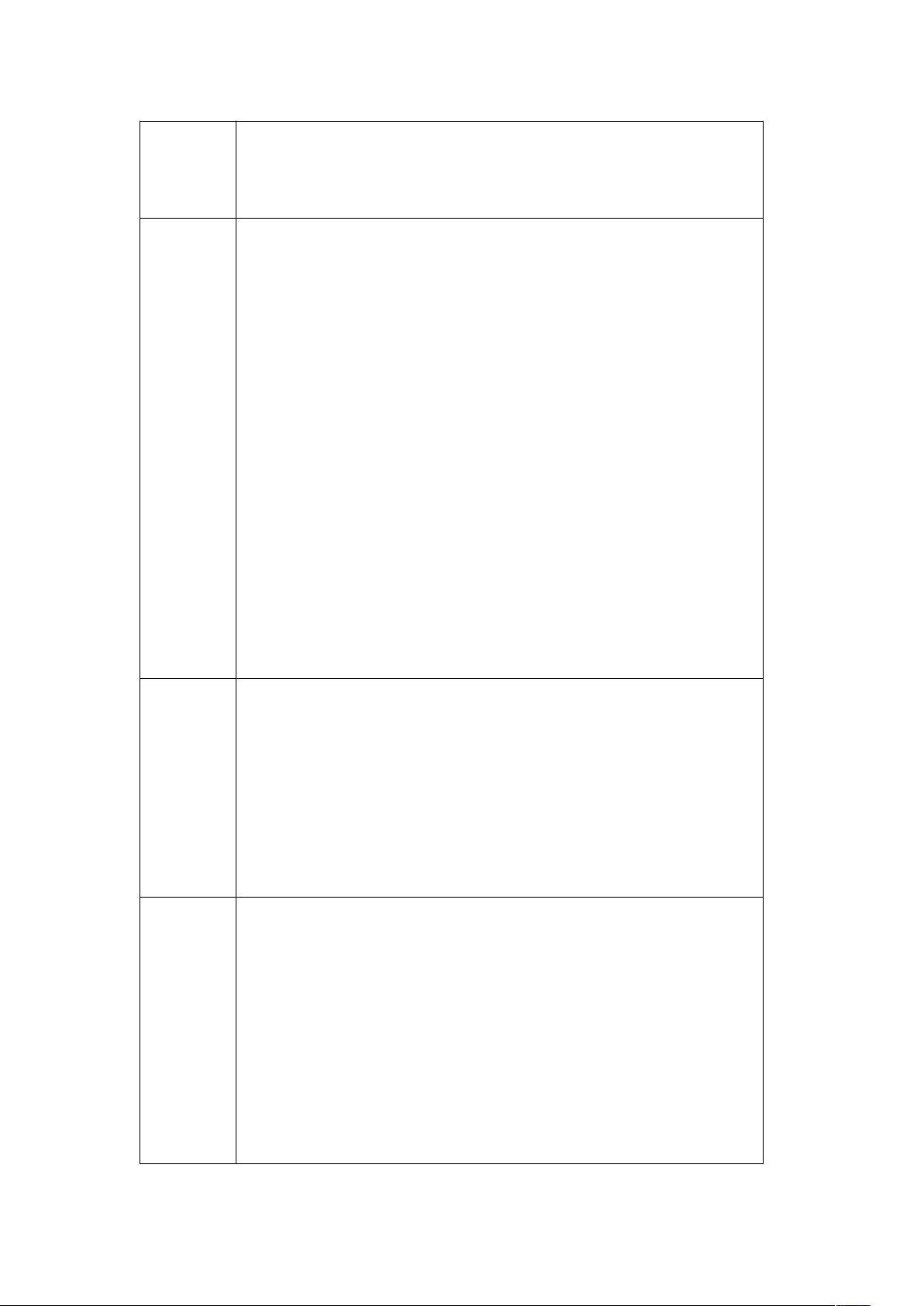

8.进行功能仿真和时序仿真 修改逻辑错误,记录仿真波形

实

验

原

理

两个二进制数相减叫做半减,实现半减操作的电路称为半减器。假

如 A 为被减数,B 为减数,bro 表示半减差,sub 表示向高位从二

进制数减法的角度看,真值表中只考虑了两个被减数本身没有考虑

低位来的借位,这就是半减器的由来。

全减器能减数、被减数和低位来的借位信号相减,并根据求减结果

给出该位的借位信号。