实验 6.1 设计数字钟实验

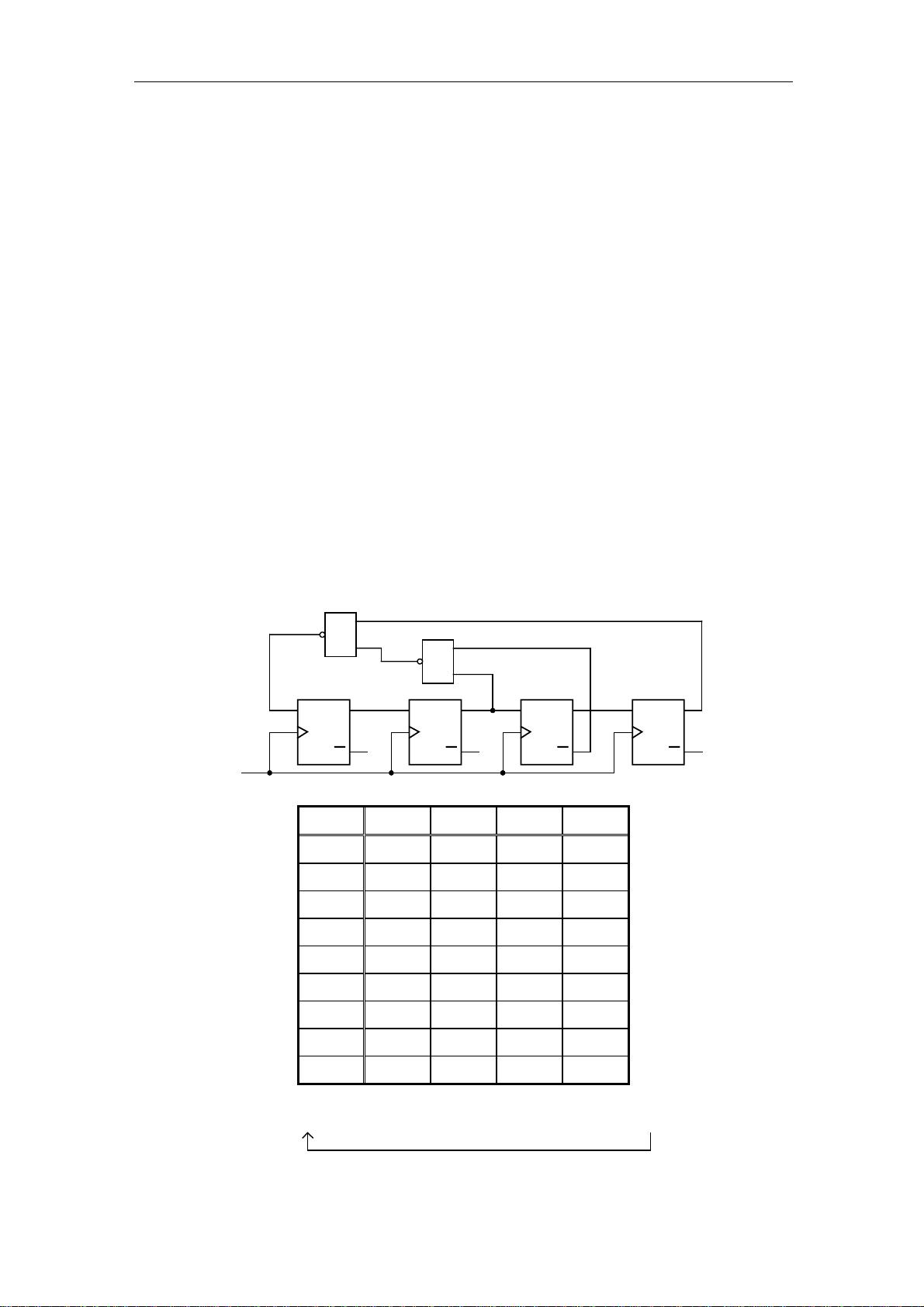

一、数字钟电原理图:

图 6.1-1 数字钟电原理图

二、用 VHDL 语言实现数字钟

1、8 分频器

⑴、源程序见实验指导书。

⑵、符号生成

图 6.1-2 8 分频器的生成符号

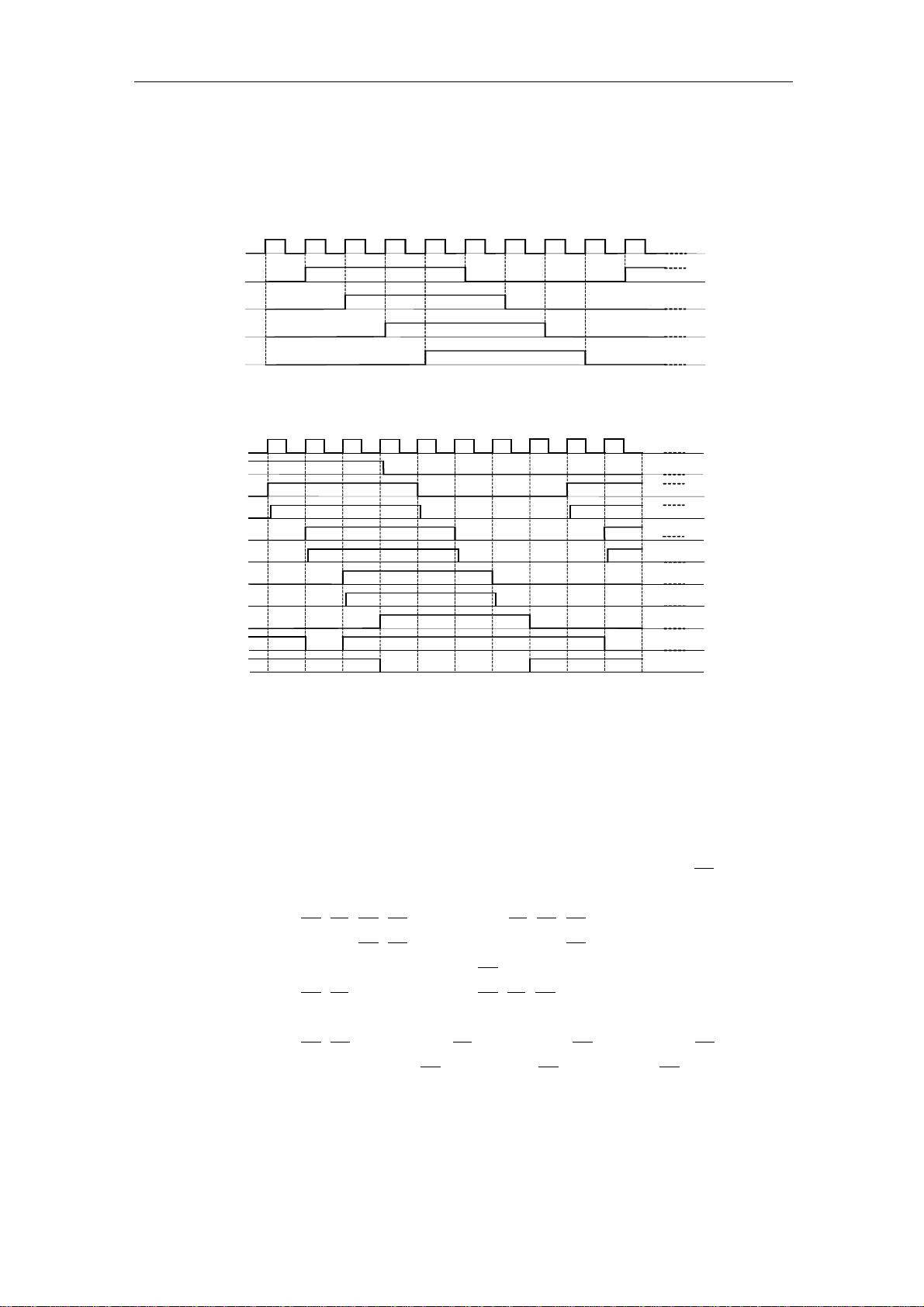

⑶、仿真波形

图 6.1-3 8 分频器的仿真波形

由以上波形可见,对 8 赫兹的输入脉冲信号 CLKI,CLKO1 输出 4 赫兹的脉冲信号,

CLKO2 输出 1 赫兹的脉冲信号。CLKO1 作为校时信号,CLKO2 作为秒信号。

202

2、60 进制计数器

⑴、源程序见实验指导书。

⑵、符号生成

图 6.1-4 60 进制计数器的生成符号

⑶、仿真波形

图 6.1-5 60 进制计数器的仿真波形

由以上仿真波形可见,该程序实现了 60 进制计数器的功能。

3、24 进制计数器

⑴、源程序见实验指导书。

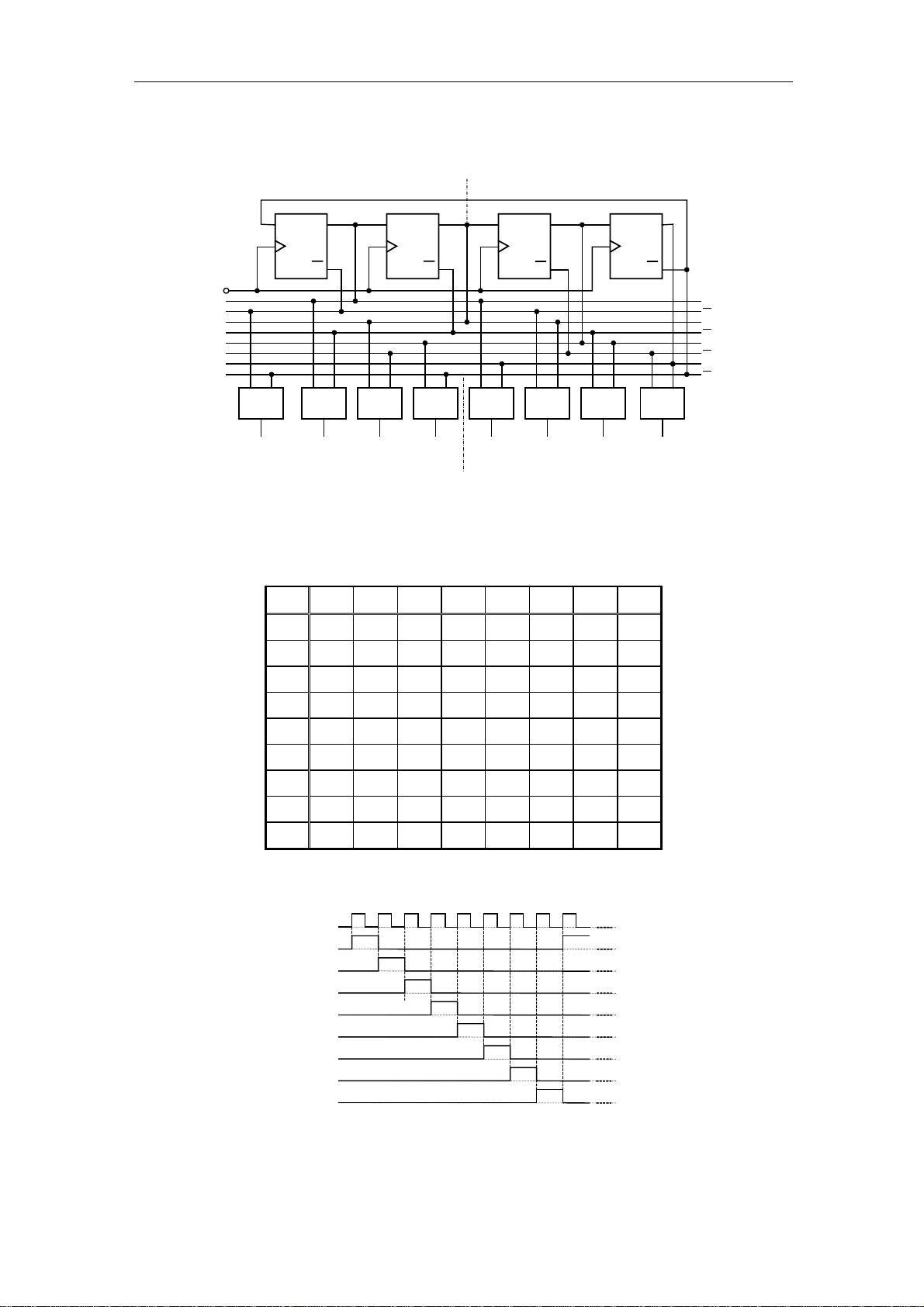

⑵、符号生成

图 6.1-6 24 进制计数器的生成符号

⑶、仿真波形

203

图 6.1-7 24 进制计数器的仿真波形

由以上仿真波形可见,该程序实现了 24 进制计数器的功能。

4、2 选 1 数据选择器

⑴、源程序见实验指导书。

⑵、符号生成

图 6.1-8 2 选 1 数据选择器的生成符号

⑶、仿真波形

图 6.1-9 2 选 1 数据选择器的仿真波形

由以上仿真波形可见,该程序实现了 2 选 1 数据选择器的功能。

5、数字钟仿真波形

204

图 6.1-10 数字钟的仿真波形

由以上仿真波形可见,当秒计数器计数满 60 时,分计数器加 1;当分计数器计数满 60

时,时计数器加 1;当时计数器计数满 24 时,回到 0。由上可见,该电路实现了数字钟的功

能。

6、校时波形

以校分为例,其波形为:

图 6.1-11 数字钟校时的仿真波形

由以上波形可见,当调分信号有效时,分计数器以 4 赫兹的频率开始计数,直至调分

信号消失,数字钟从所调时间开始计时。

通过以上设计,完成数字钟的基本功能。

205

实验 6.2 简单洗衣机时序电路

—— 设计洗衣机控制器

一、源程序

MODULE CTR

R,C1,C2,RUN,STOP,CK pin 32,25,26,27,28,11;

E0,E1,E2,E3,E4,E5,E6,E7 pin 6,7,8,9, 44,3,4,5 ISTYPE 'REG';

D0,D1,D2,D3,D4,D5,D6,D7,D8,D9,D10 node ISTYPE 'REG';

PUT=[STOP,RUN,C2,C1,R];

CNT1=3; // 洗衣循环次数;

CNT2=3; //清洗循环次数;

CNT3=2; //清洗换水循环次数;

WAITP=[D1,D0]; //延迟;

LOOP1=[D4,D3,D2]; // 计数器 1;

LOOP2=[D7,D6,D5]; // 计数器 2;

LOOP3=[D10,D9,D8]; // 计数器 3;

"Count States

s0=^b00000000; s1=^b00101000; s2=^b10001000;

s3=^b01001000; s4=^b00011000; s5=^b00100100;

s6=^b10000100; s7=^b01000100; s8=^b00010100;

s9=^b10000010; s10=^b00000001; // 状态量,为 1 表示相应输出 Ei 有效。

State_Diagram[E0,E1,E2,E3,E4,E5,E6,E7]

State s0: case (PUT == 0):s0; //保持复位;

(PUT == 8):s1; //运行命令有效,转进水洗衣;

endcase;

State s1: case (PUT == 0):s1;// 保持运行;

(PUT == 2):s2; //水位到,转正转洗衣;

endcase;

State s2: CASE (WAITP == 0): s2 //延时未到,保持正转洗衣;

WITH { WAITP :=1; LOOP1 :=LOOP1;}

(WAITP == 1): s3 //延时到,反转洗衣;

WITH { WAITP :=0; LOOP1 :=LOOP1;}

endcase;

State s3: case ((WAITP == 0)&( LOOP1 !=CNT1)): s3 //延时未到且循环1未到3次,

保持反转洗衣

WITH{WAITP :=1; LOOP1 :=LOOP1;}

((WAITP == 1)&( LOOP1 !=CNT1)): s2 //延时到,同时循环 1 未到

3 次,正转洗衣

WITH{WAITP :=0; LOOP1 :=LOOP1+1;}

206