没有合适的资源?快使用搜索试试~ 我知道了~

高速源同步系统时序分析

温馨提示

试读

8页

针对共同时钟同步系统与源同步系统详细的时序分析过程,好东西,大家共享之!

资源推荐

资源详情

资源评论

同步系统的时序分析

关于高速信号的时序分析,主要针对两种最常见的同步时序系统:共同时钟同步系统与源同

步系统。

共同时钟同步原理及时序分析

所谓共同时钟,就是在数据传输过程中,驱动端和接受端共享一个时钟,而这个时钟是由外部

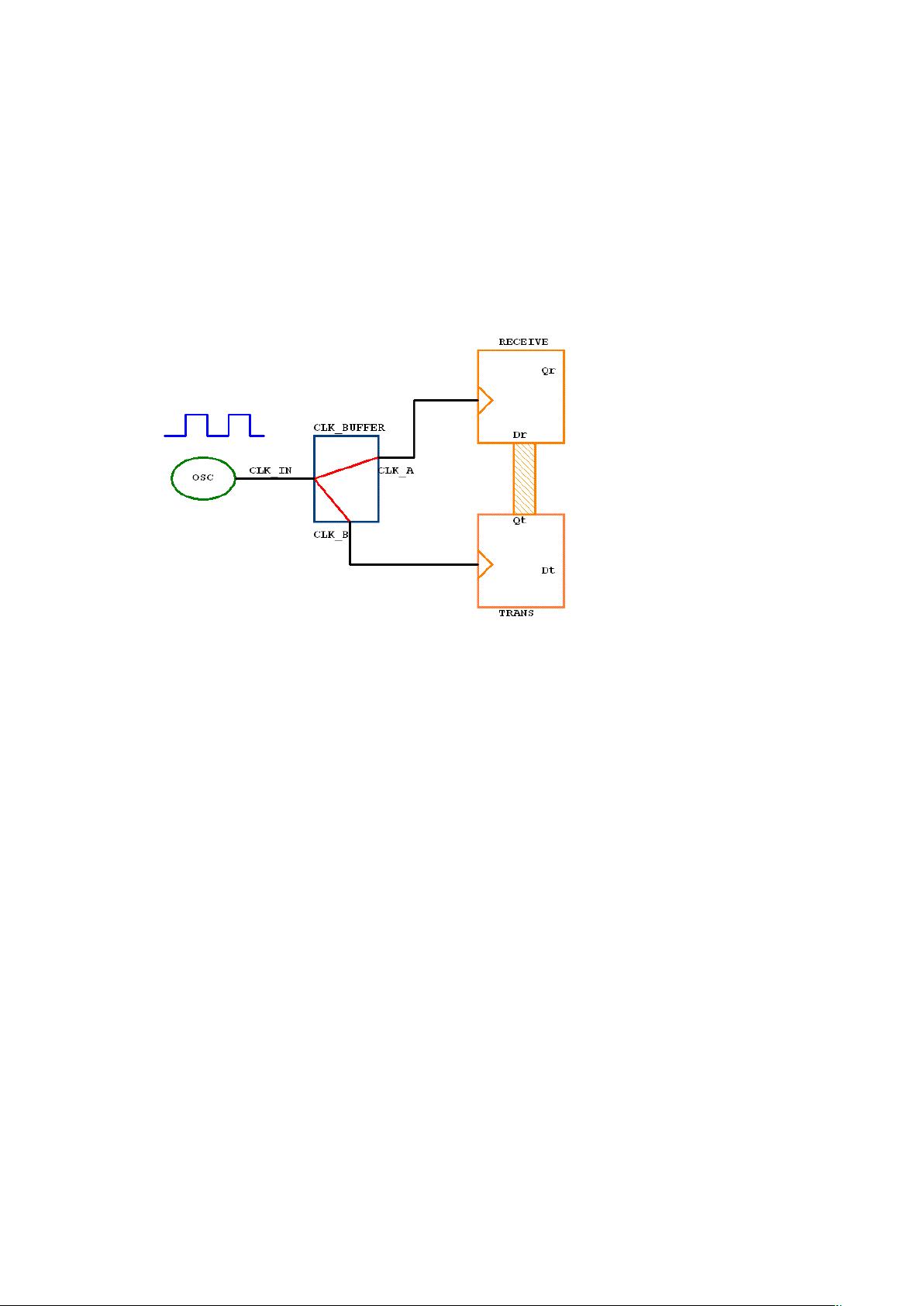

的一个器件提供,并且是同一个缓冲器输出的同相位时钟信号。如图 1 所示:

图 1:共同时钟拓扑结构

OSC 提供时钟输入,CLK_BUFFER 则分兵分两路把时钟信号分别输出为 CLK_A 和 CLK_B

到驱动端和接收端,暂时不考虑时钟 A 和 B 在 Buffer 内部的 Skew 与在 PCB 板上由于走线长度

不统一(当然也包括时钟信号接收端的负载不同)所造成的总的 Skew,即我们认为时钟 A 和 B

在理想状态下同时到达了 TRANS 和 RECEIVE。当 CLK_B 到达 TRANS 后,在第一个时钟的上

升沿,TRANS 会将数据 Dt 锁存到 Qt 等待输出,直到 Qt 输出电平达到有效参考电平 Vmeas

(通常是高电平的一半左右),这段时间我们就称之为驱动端数据信号的 Tco。

Qt 输出数据信号,通过总线传输到 RECEIVE 的 Dr,在 CLK_A 的第二个时钟上升沿到来之前

把数据送至芯片组内部。不难看出,如果要使得系统正常工作,必须在一个时钟周期内让数据

信号从驱动端发送到接收端,即理论上图 1 中的 Qt 到 Dr 的斜线通道的传输延时要小于一个时

钟周期。如果传输延时大于一个时钟周期,则接收端的第二个 CLK 信号的上升沿到来时,正确

的数据还在传输过程中,就会导致由于数据信号建立时间不足而导致错误的发生。这就是接收

端的数据对建立时间的要求。

上述分析得出结果就是数据信号要提前 CLK_A 的第二个上升沿到来,那么要提前多少呢?

这就要满足接收端的 setup time。这就要求传输线尽可能地短,但是太短的传输线又带来另一个

问题,就是如果数据信号提前 CLK_A 的第二个上升沿太多的时间,那么时钟的上升沿对数据

信号进行锁存的时候,数据信号没有足够的 hold on time 来保证被正确地采样,同样也会导致数

据出错。

综上所述,共同时钟的时序要求就是:数据信号传输线不能太长或者太重,太长导致数据来

得太慢,接收端没有足够的数据建立时间;当然数据信号传输线也不能太短,太短导致数据信

号提前接收端时钟的第二个上升沿太多,没有足够的数据保持时间。这就是共同时钟的一个最

1

资源评论

beiyouxia2020-01-02非常好的资料,感谢分享!

beiyouxia2020-01-02非常好的资料,感谢分享!

chenzhugy

- 粉丝: 6

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功