没有合适的资源?快使用搜索试试~ 我知道了~

VHDL Verilog 实现三态门的源程序以及testbench代码

温馨提示

试读

9页

1)VHDL 语言下同步、异步三态门的实现和仿真; 2)VerilogHDL 语言下同步、异步三态门的实现和仿真;

资源推荐

资源详情

资源评论

http://blog.sina.com.cn/u/1726672527

1/9 韦志恒 weizhiheng99@yahoo.com.cn

HDL语言的INOUT端口仿真暨三态门仿真

------VHDL 和 VerilogHDL

韦志恒 weizhiheng99@yahoo.com.cn

关键词:

inout 双向端口 三态门原理 inout 双向端口方针 三态门仿真

概述

三态门是 FPGA 编程开发中经常遇到的一个问题。一个典型的应用就是 TI 的 DSP 的

EMIF 总线。针对 HDL 语言的三态门应用示例和仿真示例在网上很多,但是往往只讲述一

种语言的,没有给予两种语言下三态门的一个综合评述,如讲述二者使用、仿真时的区别等。

特别是 VerilogHDL 语言下的三态门仿真,很多讲述都是语焉不详,包括使用 Force 语句等,

这些使用人手工干预的仿真方法明显违背了 EDA 自动化的宗旨,是使用者对其仿真方法不

明确的情况下的一种权益之计。

本文将使用一个 DSP EMIF 接口逻辑的例子,详细讲述:

(0)什么叫做 Z 态?三态的晶体管级实现是怎样的?

(1)VHDL 语言下同步、异步三态门的实现和仿真;

(2)VerilogHDL 语言下同步、异步三态门的实现和仿真;

(3)综述两种语言下仿真的要点。

一 双向管脚 INOUT 与三态门介绍

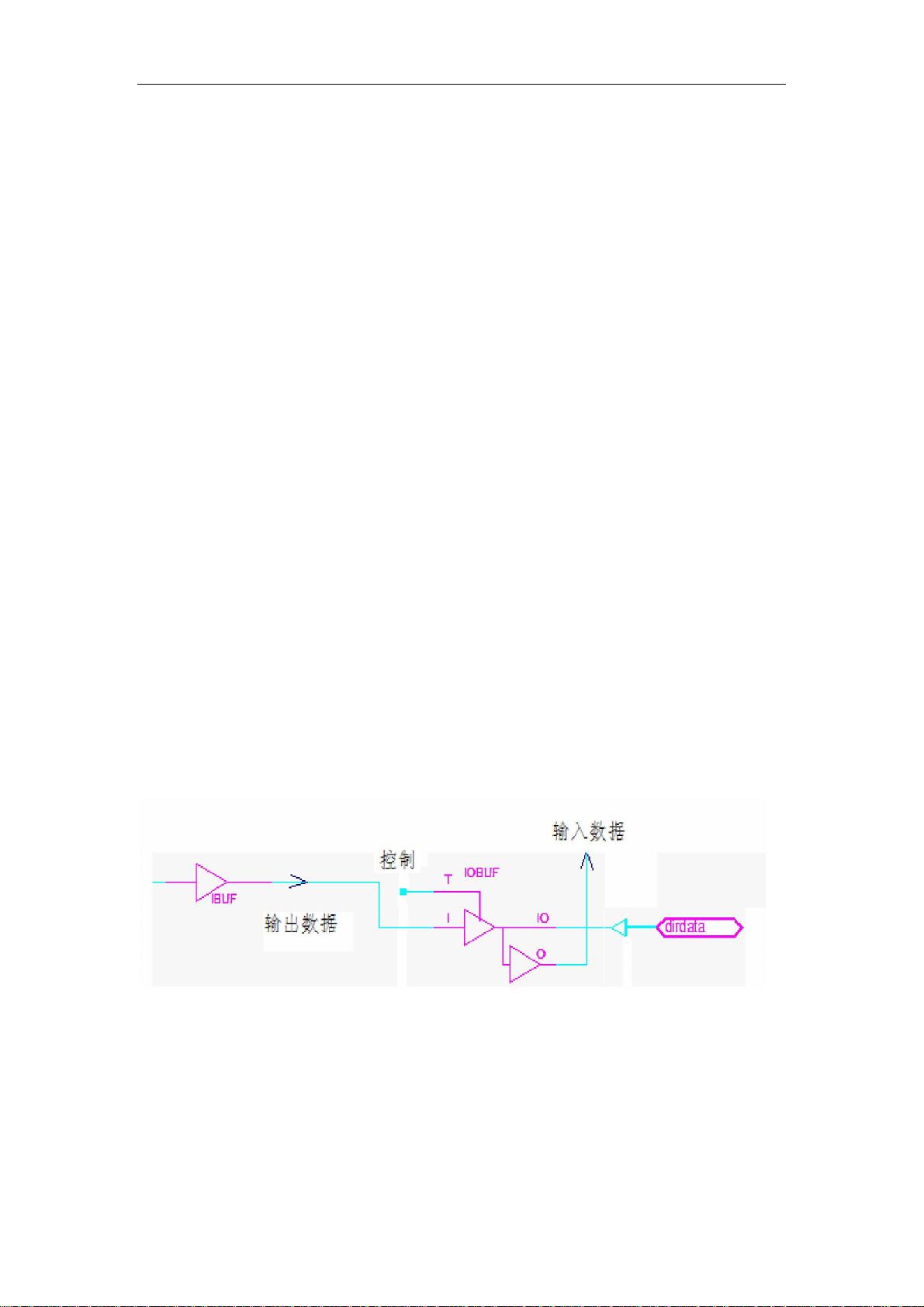

图 1 一个典型的 FPGA 的管脚

由图 1 可以看出,一个 FPGA 的管脚由一个输入缓冲器和一个三态输出缓冲器构成。

三态输出缓冲器,即三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三

种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门

都有一个 EN 控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态。

准确来讲,三态的高阻态(Z 态)指的就是门的输出脚的两个驱动 TTL 或 MOS 管都处

于截止状态时的输出状态。参考图 2、图 3 和图 4 有更详细的理解。

资源评论

wangxru2014-11-25已经参考仿真通过啦~

wangxru2014-11-25已经参考仿真通过啦~ qiaokuangdie47732016-12-30不错不错,值得下载

qiaokuangdie47732016-12-30不错不错,值得下载 mymarian2013-10-23内容很详细,不错

mymarian2013-10-23内容很详细,不错 hit_092014-10-24很有帮助,谢谢分享!!!

hit_092014-10-24很有帮助,谢谢分享!!! chengozhou2013-05-12VerilogHDL好学吗

chengozhou2013-05-12VerilogHDL好学吗

chenyan8189

- 粉丝: 15

- 资源: 11

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功