没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

利用

!"#$

实现

%&’(

编解码功能

朱勤为

!

唐 宁

!

赵明剑

"

桂林电子科技大学 信息与通信学院

!

广西 桂林

541004

#

摘要

)HDB3

"

三阶高密度双极性

$

码具有无直流分量

%

低频成分少

%

连零个数不超过

3

个

%

便于提取时钟信号等特点

&

通

过对

HDB3

编解码原理进行分析和研究

!

提出一种基于

FPGA

的

HDB3

编解码实现方法

!

给出

Verilog HDL

语言的实现

方法和仿真波形

!

完成硬件电路的设计和测试

!

采用该方法设计的

HDB3

编解码器已应用于相关实验设备中

&

关 键 词

*HDB3

编码

’

HDB3

解码

’

FPGA

’

Verilog HDL

中图分类号

*TN911.2

文献标识码

:

A

文章编号

:

1674-6236

(

2009

)

12-0076-04

+,-.-/0 1"2$ ,3 456-070 %&’8 5390: 4;9 905390: <=;5,-3;

ZHU Qin-wei

,

TANG Ning

,

ZHAO Ming-jian

(

!"#$%&% "’ ()*"+ ,-./") -)0 1",,2)/34./")

,

52/$/) 6)/78+9/.: "* ; $8<.+")/< =8>?)"$"&:

,

52/$/) 541004

,

@?/)4

)

>?@,:45,* The H DB3 code

(

High Den sity Bipolar of order 3 code

)

has the featu res of no DC c omponent

,

little low frequency

component and less than three zero string

,

making the extraction of clock signal is more accessible.Through analyzing the

principle of HDB3 coding and decoding

,

a new coding and decoding method base d on FPGA is proposed.All the modules

are programmed and simulated by Verilog HDL.And the hardware circuit is desi gned and tested.The HDB3 coder and de-

coder have been applied to relat ed experi mental eq uipment.

A0B C3:9@* HDB3 coder

;

HDB3 decoder

;

FPGA

;

Verilog HDL

D

引言

数字通信系统的某些应用可对基带信号 不 载 波调 制 而

直接传输

,

其中传输线路对码型的要求如下

:

信码中不宜有

直流分量

,

低频分量应尽可能的少

,

码型要便于时钟信号提

取

。

根据这些要求

,

ITU- T

(

国际电联

)

在

G. 703

建议中规定

,

对于

2 MHz

、

8 MHz

、

32 MHz

速 率 的 数 字 接 口 均 采 用

HDB3

(

三阶高密度双极性

)

码

[1]

。

HDB3

码具有无直流分量

,

低频成

分少

,

连零个数不超过

3

个等特点

,

便于时钟信号的提取 和

恢复

,

适合在信道中直接传输

[2-3]

。

这里利用

Verilog HDL

语

言

[4-5]

设计用于数字通信系统中的

HDB3

编解码器

。

E %&F(

编码模块设计

要设计一个实用的编码模块

,

首先要深入研究其编码规

则及其特点

,

然后根据编码规则设计符合电路特性的编码流

程

。

HDB3

码的编码规则包括

:

①

将消息代码变换成

AMI

码

,

AMI

码的编码规则是对码流中的非

“

0

”

符号进行正负交替

;

②

检查

AMI

码中的连零情况

,

当连零的个数小于

4

个时

,

保持

AMI

的形式不变

;

当连零的个数达到

4

个或超过

4

个时

,

则将

非零码后的第

4

个

“

0

”

替换成

V

码

,

其中

V

码的极性与前一非

零码

(

+1

或

-1

)

的极性保持一致

,

例如

,

前面的非零码是

+1

,

则

将

V

码记为

+V

;

③

完成插

V

操作后

,

检查

2

个相邻

V

码之间

非零码的个数是否为偶数

,

若为偶数

,

则再将相邻

2

个

V

码中

后一个

V

码的前一非零码后的第一个

“

0

”

变为

B

码

,

B

码的极

性与前一非

“

0

”

码的极性相反

,

同时

B

码后面的非

“

0

”

码极性

再次进行交替变换

,

保证极性交替反转特性

。

编码规则中出现的

V

码

、

B

码只是作为标识符

,

最终的

电路实现还是

“

0

”

和

“

1

”

这两种逻辑电平

,

因此需要采用二进

制 编 码 对

“

1

”、 “

0

”、

V

、

B

进 行 编 码

, “

00

”

表 示

“

0

”, “

01

”

表 示

“

1

”,“

10

”

表示

B

,“

11

”

表示

V

。

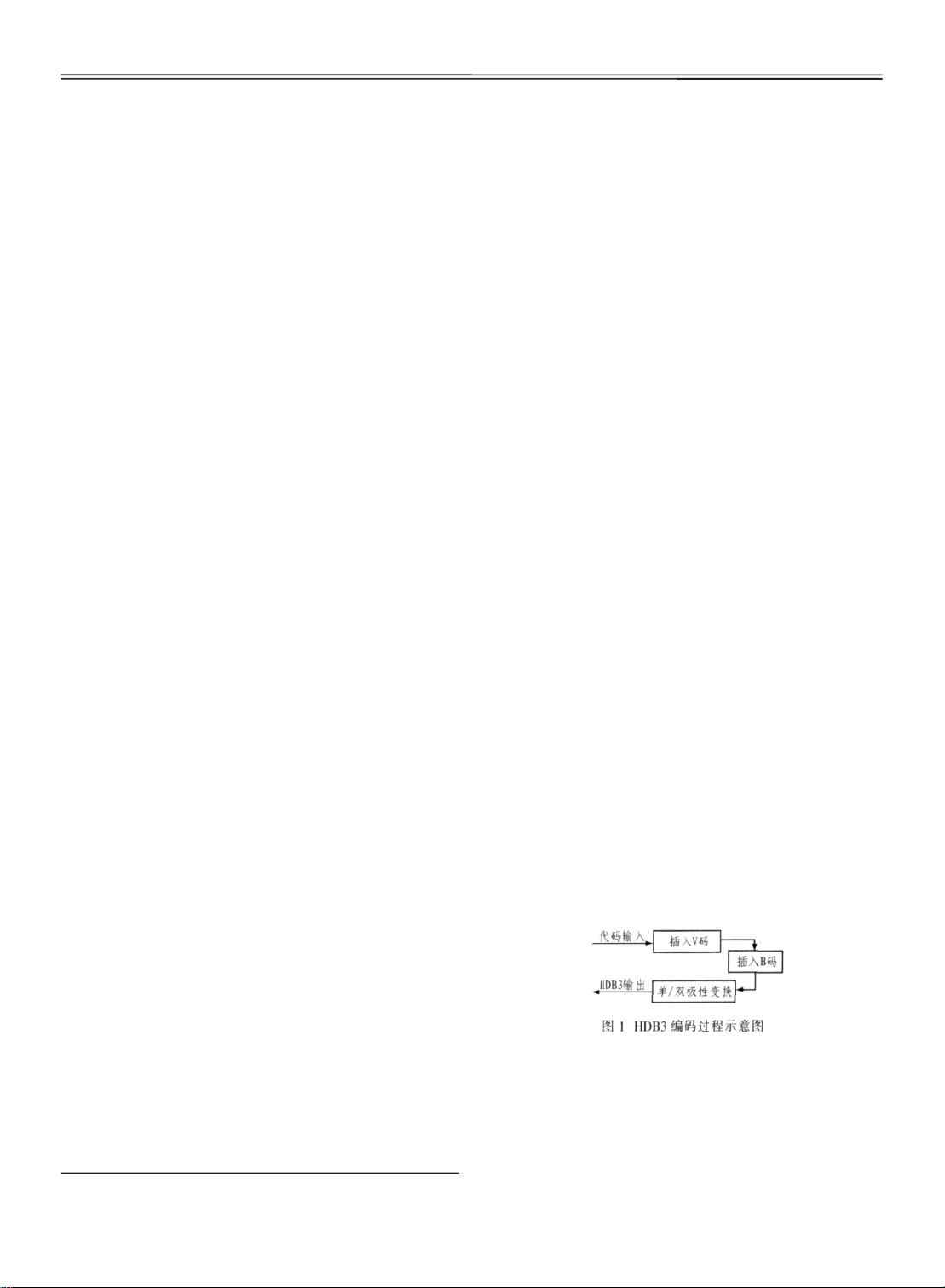

根据编码规则和利用

FPGA

实

现的特点

,

将编码过程

:

首先插入

V

码

,

然后插入

B

码

,

最后

是单双极性变换

。

如果按照编码规则的顺序设计

,

应该首先

进行单双极性变换

[6]

,

在完成插

V

和插

B

后

,

还需根据编码规

则变换当前

B

码之后的非零码的极性

,

这需要大量的寄存器

来保存当前数据的状态

,

导致电路非常复杂

,

占用大量 的

FPGA

内部逻辑单元

,

实现难度大

,

且成本高

。

HDB3

编码过程

示意图如图

1

所示

。

GHI

插入

J

码过程

插入

V

码过程是对消息代码里的连零串进行检测

,

一旦

出现

4

个连零串的时候

,

就把第

4

个

“

0

”

替换成破坏符

V

,

其

他情况下消息代码原样输出

。

输入的代码经插

V

操作后全部

转换成双相码

,

即

“

0

”

变换成

“

00

”,“

1

”

变换成

“

01

”,

V

变换成

“

11

”。

图

2

是插入

V

码过程的流程

,

代码输入到插

V

模块后

,

收稿日期

:

2009-06-21

稿件编号

:

200906074

作者简介

:

朱勤为

"

1984-

$!

男

!

浙江东阳人

!

硕士研究生

&

研究方向

(

集成电路设计与测试

&

图

1 HDB3

编码过程示意图

2009

年

12

月

Dec. 2009

第

17

卷 第

12

期

Vol.17 No.12

电子设计工程

Electronic Design Engineering

-76-

资源评论

cat_261

- 粉丝: 1

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功