没有合适的资源?快使用搜索试试~ 我知道了~

资源详情

资源评论

资源推荐

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

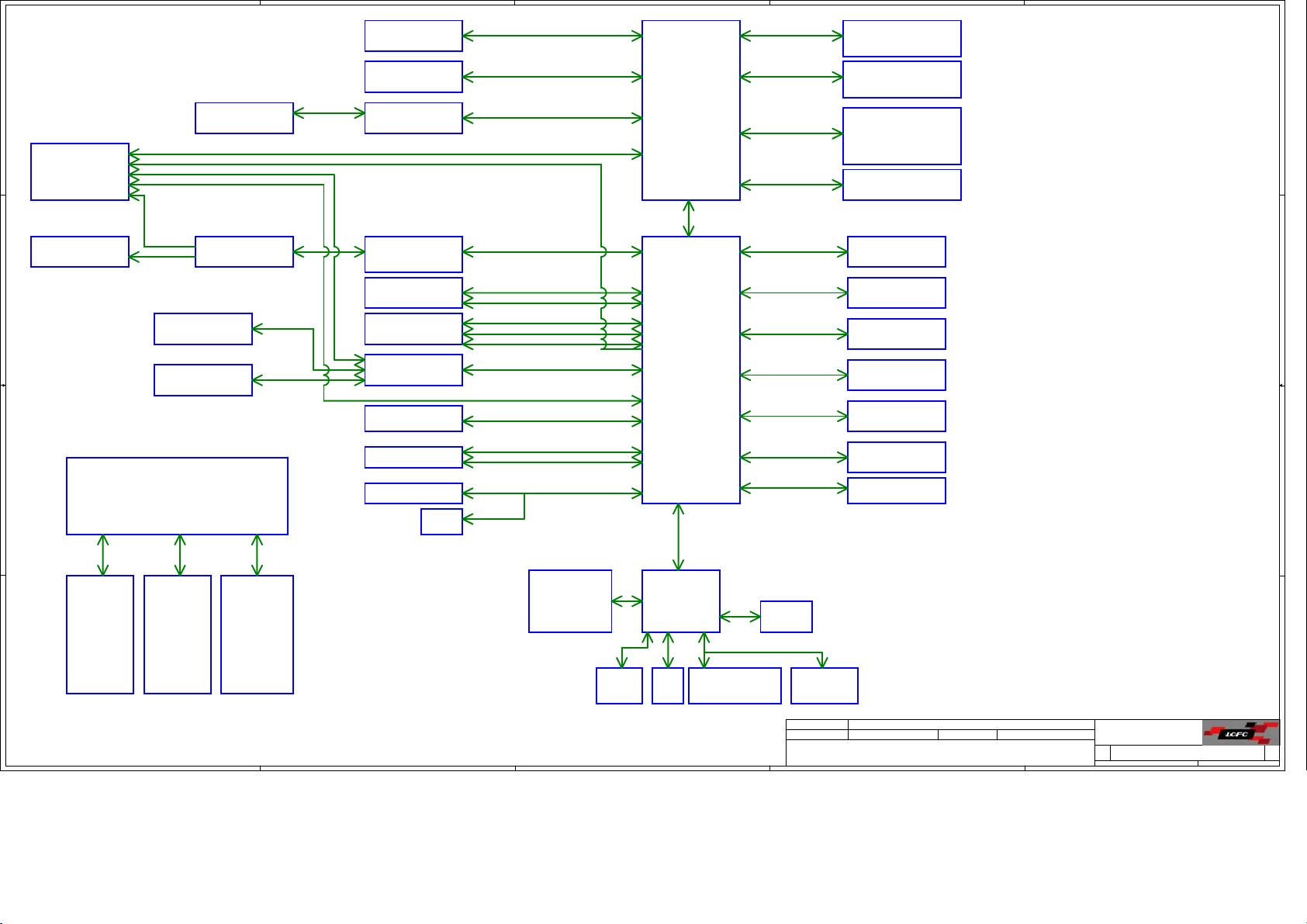

T460P

Page:03~13==>CPU SKL-H

Page:14~23==>PCH SKL-H

Page:24=====>XDP CONNECTOR

Page:25=====>RTC BATTERY

Page:26=====>SPI FLASH

Page:27~28==>DDR4 MEMORY

Page:31~39==>N16S-GT

Page:40~41==>THINK ENGINE

Page:42~44==>MEC1653L

Page:45~50==>AUDIO ALC3245-CG

Page:51~53==>LAN WGI219LM

Page:54=====>CARD_READER RTS5232S-GR

Page:55=====>THERMAL SENSOR/G SENSOR/TPM

Page:56=====>eDP/CMOS/LOGO-LED CONN.

Page:57=====>HDMI BTB CONN.

Page:58=====>PS8330B REPEATER DP

Page:60=====>CS13 DOCKING CONN.

Page:59=====>MINI-DP CONN.

Page:61=====>SATA HDD CONN.

Page:62=====>WLAN/WWAN/SIM CONN.

Page:63=====>USB3 P1/2 CONN.

Page:64=====>USB3 P3 CONN.

Page:65=====>FAN/SC CONN

Page:66=====>KEYBOARD/TRACK POINT CONN

Page:67=====>Click Pad/FPR/PBTN

Page:68=====>SMBUS SWITCH/LPC DEBUG PORT

Page:69=====>EMC solution for BDW ESD

Page:70=====>LOAD SW VCCST/VCCSTG

Page:79=====>SCREW HOLE

Page:80=====>DC-IN

Page:81=====>BATTERY INPUT

Page:82=====>BATTERY CHARGER(BQ24780S)

Page:83=====>DC/DC VCC5M/VCC3M

Page:84=====>DC/DC IMVP8

Page:85=====>DC/DC VCCPUCORE

Page:86=====>DC/DC VCCGFXCORE_I

Page:87=====>DC/DC VCCSA

Page:88=====>CPU PROCESSOR DECOUPLING

Page:89=====>DC/DC VCCCPUIO

Page:90=====>DC/DC VCC1R0_SUS

Page:91=====>DC/DC VCC1R2A/VCC0R6B

Page:92=====>DC/DC VCC2R5A

Page:93=====>DC/DC GFXCORE_D

Page:94=====>DC/DC VCC1R5VIDEO

Page:95=====>DC/DC VCC1R05VIDEO_PLL

CPU

BGA144 0

35W

3,4,5,6,7,8,9,

10,11,12,13

Intel

Skylake_H

vPro

14,15,16,17,18

19,20,21,22,23

PCH

Intel

Skylake-QM170

eDP CONN 14"

FHD/WQHD

eDPx4

HDMI BOARD

HDMI Conn

PS8330 REPEATERmDP Conn.

Docking CS13

NGFF CARD

WLAN(WiGig)&BT

NGFF CARD WWAN

LAN

Intel

WGI219LM Vpro

LAN SWITCH

PI3L720ZHEX

DDI1

DDI2

DDI3

mDP

PCIE Gen1 X1MDI

DOCK MDI

SYS MDI

LAN RJ45 CONN

PCIE Gen1 X2

USB2.0

PCIE Gen1 X1

USB2.0

GPP

DDI3

GPP

Codec

ALC3245-CG

HDA AUDIO

I2S

I2S

SP_OUTL

SLEEVE/RING

USB2.0&USB3.0

SPK Conn.

AUDIO Conn

USB2.0&USB3.0

DMI X4

USB3.0 CONN

USB1&USB2

USB3.0 CONN

USB3

USB2.0 Camera

USB2.0

Smart Card Slot

USB2.0

Fingerprint

USB2.0

Touch Panel

USB2.0&USB3.0

USB2.0&USB3.0

USB2.0

USB2.0

USB2.0

USB2.0

40,41

Lenovo

ASIC

ThinkEngine

42,43,44

Embedded

Controller

MEC1653L

FAN KEYBOARD

TRACK POINT CONN

Click Pad

SPI ROM 8+8 RTC BATTERY

SATA HDD SATA HDD

RTCRST

SPI

LPC BUS

G-Sensor

TPM

DDR 2166

DDR 2166

UNBUFFERED

DDR4

SO-DIMMA1 Channel A

UNBUFFERED

D

DR4

SO-DIMMB1 Channel B

PEG X4

PROC XDP CONN

NVIDIA

dGPU

31-39

N16S-GT

28

27

24

2526

45,46,48,49

51

54

Cardreader

RTS5232S-GR

PCIE Gen1 X1

55

55

I2C

56

57

5859

60

5253

61

62

62

63

64

65

56

67

56

50

47

65 66 67

POWER

BOTTON

67

USB BOARD

AUDIO BOARD

AUDIO BOARD HDMI BOARD USB BOARD

T460P MAIN BOARD

BTB BTB WTB

AUDIO CONN

LID SW

HDMI CONN

PS8407

USB CHARGE

TPS2546RTER

USB CONN

POWER BOTTON

POWER LED

Page:71=====>LOAD SW LOAD SW PCH SUS/TRA

Page:72=====>LOAD SW LAN

Page:73=====>LOAD SW B

Page:74=====>LOAD SW WWAN&WLAN

Page:75=====>LOAD SW VIDEO&FBVDD

Page:76=====>DISCHARGE CIRCUIT VIDEO

PCIE Gen1 X1

USB3.0

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSE D TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

TITLE PAGE

Custom

199

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSE D TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

TITLE PAGE

Custom

199

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSE D TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

TITLE PAGE

Custom

199

Tuesday, November 03, 2015

2015/07/16

2016/01/16

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

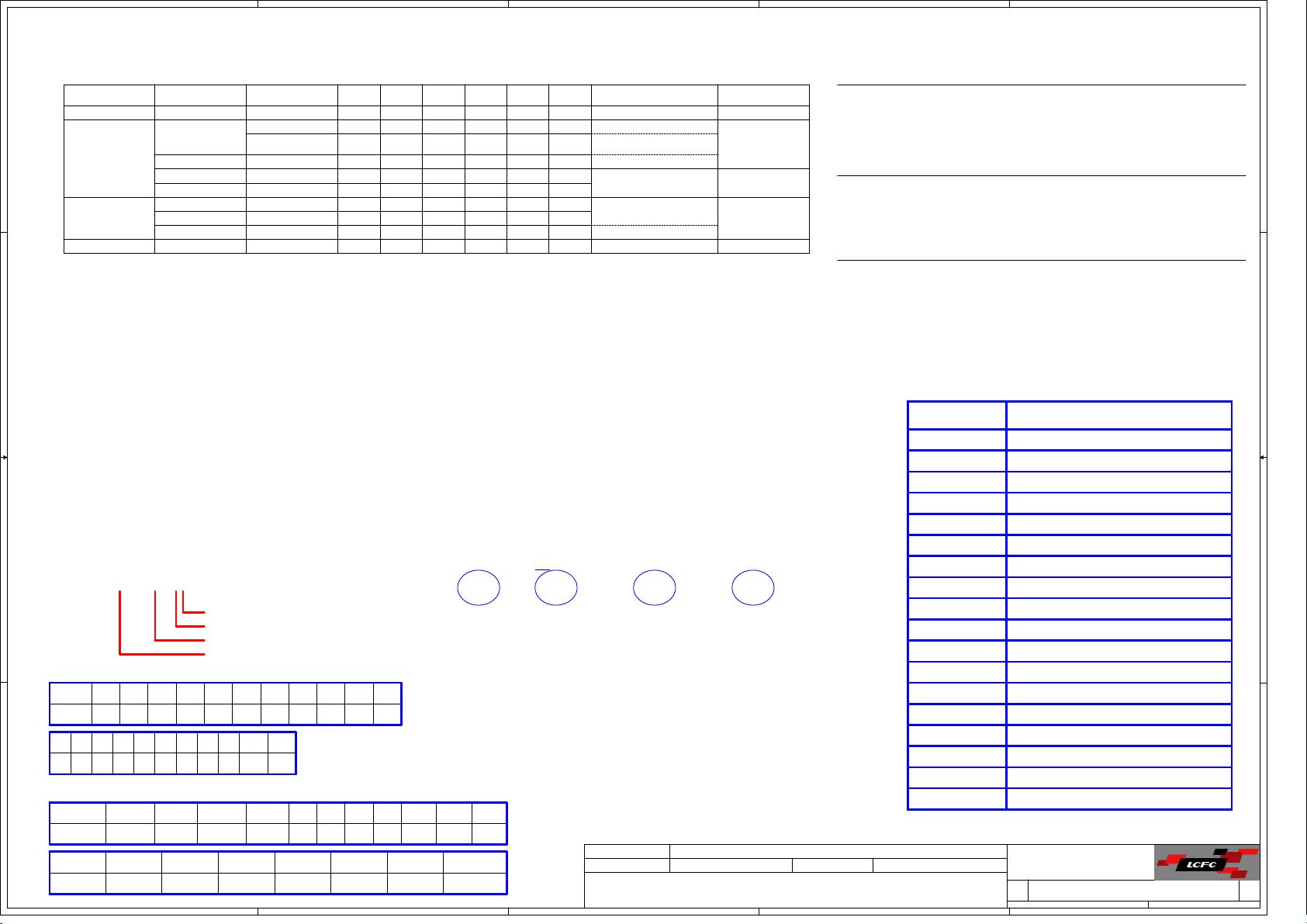

Gx State

(System State)

Sx State

(System State)

Mx State

(System State)

SW

Power

M

Power

SUS

Power

AMT

Power

A

Power

B

Power

User Observation Chipset

G0 S0 M0

S3

M3

ON ON ON ON ON ON

M-OFF

ON ON ON ON ON OFF

ON ON ON OFF ON OFF

Deep S3 M-OFF ON ON OFF OFF ON OFF

S4 M3 ON ON ON ON OFFOFF

Deep S4 M-OFF ON ON ONOFF OFF OFF

G1

G2

S5

Deep S5

S5 EC OFF

M-OFF

M-OFF

M3

G3 --- --- OFF OFF OFF OFF OFF OFF

OFF OFF OFF OFF OFF

OFFOFFOFF

OFF OFFON

ON

ON

ON

ON

ON ON

ON

System Operating

Standby

Standby

with USB wake enabled

Standby

Hibernation

with RTC wakeup

Hibernation or

Shutdown

No Power

Full On

Suspend-to-RAM

(STR)

Suspend-to-Disk

(STD)

Soft Off

Mechanical Off

Schematics Mark Definition

TABLE: SYSTEM POWER STATE

0x9E

Master VGA

0XC8

Intel Lan_I219

1001 0000b

DDR DIMM1

Device

EC SMBus0 address

Address

Device

PCH SM Bus address

0001 011X b

Smart Battery

Device

EC SMBus2 address

Address

0001 0010

Charge Controller

Device

Address

EC SMBus10 address

Device

1001 0010b

DDR DIMM2

Address

Address

PCH SM Bus0 address

G-Senor (LIS3DH)

EC SMBus1 address

G-Senor (KX023)

Device

Address

0011 000Xb

0011 110Xb

CH-A

CH-B

Code Z5VZ5U Y5UZ5P Y5PY5V

Symbol

X5R NPOX7R X6SCOG

01 32547698A

CJCHBJ SJSHCK UJ X5SSLUK

B

NOJ

CFEDHGKJI

+-0.05PF

L

+-0.25PF+-0.1PF +-1%+-0.5PF

Symbol

+-2% +-3%Tolerance +-10%+-5% +-30%+-20%

AB DCGFJHMKN

+30,-10%+100,-0%Tolerance

Symbol P Q ZXVYS

+40,-20%+20,-10% +50,-20%+80,-20%

Tolerance:

-30% ~ 10%

Temperature Characteristics:

Ceramic Capacitors:

Tolerance

0.1U_0402_6.3VXX

Rated Voltage

Temperature Characteristics

Package Size

Capacitor Naming Note

NOTE

For EMI SolutionEMC@

BOM Structure Table

BOM Structure

ME@ ME Connector

For GC6 functionGC6@

DEBUG@ For EE DEBUG

VSE2G@

DPRE@ DP re-driver function

NODPRE@ Disable DP re-driver

NGC6@ NON GC6 function

RF@ For RF Solution

VHC2G@

VME2G@

For SAMSUNG VRAM Setting

For RF HYNIX VRAM Setting

For Micron VRAM Setting

X76_VSE2G@

X76_VHC2G@

X76_VME2G@

K4W4G1646E-BC1A x4 + 24.9K

H5TC4G63CFR-N0C x4 +30.1k

MT41J256M16HA-093G x4 +10k

CS@ For CURRENT SENSE

UMA@

DIS@

For UMA

For DIS

UC1@ For CPU

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

Blank

Custom

299

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

Blank

Custom

299

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

Blank

Custom

299

Tuesday, November 03, 2015

2015/07/16

2016/01/16

ZZZ2

K4W4G1646E-BC1A

X76_VSE2G@

X7608112001

ZZZ1

BT463

DA80000Z600

PCB@

ZZZ3

MT41J256M16HA-093G

X76_VME2G@

X7608112002

ZZZ4

H5TC4G63CFR-N0C

X76_VHC2G@

X7608112003

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

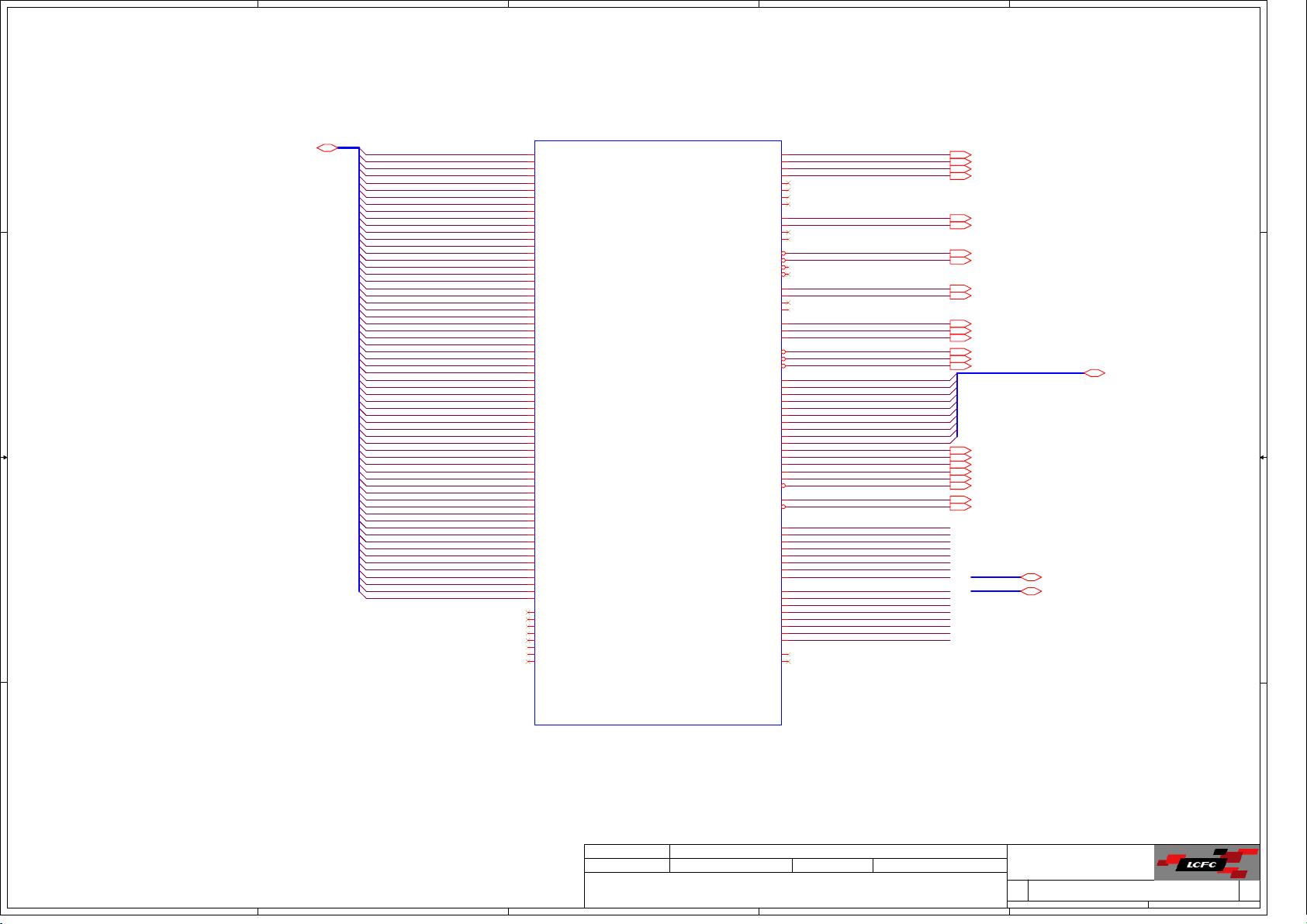

DDR4 INTERLEAVE IMPLEMENTATION

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A12

M_A_A11

M_A_A10_AP

M_A_A9

-M_A_ACT

M_A_BG1

M_A_A13

M_A_BA0

M_A_BA1

M_A_BG0

M_A_A15_CAS_N

M_A_A14_WE_N

M_A_A16_RAS_N

M_A_A1

M_A_A0

M_A_CKE0

M_A_CKE1

-M_A_CS1

-M_A_CS0

M_A_ODT1

M_A_ODT0

M_A_DDRCLK1_1066M

-M_A_DDRCLK1_1066M

-M_A_DDRCLK0_1066M

M_A_DDRCLK0_1066M

-M_A_DQS0

-M_A_DQS1

-M_A_DQS2

-M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS1

M_A_DQS0

M_A_DQS7

-M_A_DQS4

M_A_DQS3

M_A_DQS2

M_A_DQ53

M_A_DQ55

M_A_DQ54

M_A_DQ56

M_A_DQ58

M_A_DQ57

M_A_DQ59

M_A_DQ61

M_A_DQ60

M_A_DQ62

M_A_DQ63

-M_A_DQS5

-M_A_DQS7

-M_A_DQS6

M_A_PARITY

-M_A_ALERT

M_A_ODT1 [27]

M_A_ODT0 [27]

M_A_BG0 [27]

M_A_BA0 [27]

M_A_BA1 [27]

M_A_CKE0 [27]

M_A_CKE1 [27]

-M_A_CS0 [27]

-M_A_CS1 [27]

M_A_DDRCLK0_1066M [27]

-M_A_DDRCLK0_1066M [27]

-M_A_DDRCLK1_1066M [27]

M_A_DDRCLK1_1066M [27]

-M_A_ACT [27]

-M_A_ALERT [27]

M_A_PARITY [27]

M_A_BG1 [27]

M_A_A12 [27]

M_A_A13 [27]

M_A_A11 [27]

M_A_A10_AP [27]

M_A_DQ[0..63][27]

M_A_A14_WE_N [27]

M_A_A15_CAS_N [27]

M_A_A16_RAS_N [27]

M_A_A[0..9] [27]

-M_A_DQS[0..7] [27]

M_A_DQS[0..7] [27]

Size

Document Number Rev

Date: Sheet of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : DDR4 CH-A

Custom

399

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : DDR4 CH-A

Custom

399

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : DDR4 CH-A

Custom

399

Tuesday, November 03, 2015

2015/07/16

2016/01/16

DDR CHANNEL

A

SKYLAKE_HALO

BGA1440

1 OF 14

UC1A

SKYLAKE-H-CPU_BGA1440

QHR7@

DDR0_DQ[36]/DDR1_DQ[4]

AB5

DDR0_DQ[35]/DDR1_DQ[3]

AA5

DDR0_DQ[34]/DDR1_DQ[2]

AA4

DDR0_DQ[32]/DDR1_DQ[0]

AB1

DDR0_DQ[31]/DDR0_DQ[47]

BC2

DDR0_DQ[30]/DDR0_DQ[46]

BC1

DDR0_DQ[45]/DDR1_DQ[13]

V4

DDR0_ECC[6]

AY1

DDR0_DQ[63]/DDR1_DQ[47]

L1

DDR0_DQ[54]/DDR1_DQ[38]

R1

DDR0_DQ[55]/DDR1_DQ[39]

P1

DDR0_DQ[43]/DDR1_DQ[11]

U2

DDR0_DQ[28]/DDR0_DQ[44]

BD5

DDR0_DQ[20]/DDR0_DQ[36]

BG2

DDR0_DQ[19]/DDR0_DQ[35]

BF5

DDR0_DQ[16]/DDR0_DQ[32]

BG4

DDR0_ECC[4]

BA5

DDR0_DQ[60]/DDR1_DQ[44]

M5

DDR0_DQ[4]

BN5

DDR0_DQ[2]

BP3

DDR0_DQ[3]

BR3

DDR0_DQ[5]

BP6

DDR0_DQ[6]

BP2

DDR0_DQ[7]

BN3

DDR0_DQ[8]

BL4

DDR0_DQ[9]

BL5

DDR0_DQ[10]

BL2

DDR0_DQ[11]

BM1

DDR0_DQ[13]

BK5

DDR0_DQ[14]

BK1

DDR0_DQ[18]/DDR0_DQ[34]

BF4

DDR0_DQ[21]/DDR0_DQ[37]

BG1

DDR0_DQ[23]/DDR0_DQ[39]

BF2

DDR0_DQ[25]/DDR0_DQ[41]

BD1

DDR0_DQ[27]/DDR0_DQ[43]

BC5

DDR0_DQ[29]/DDR0_DQ[45]

BD4

DDR0_DQ[12]

BK4

DDR0_DQ[17]/DDR0_DQ[33]

BG5

DDR0_DQ[15]

BK2

DDR0_CKP[0]

AG1

DDR0_DQ[42]/DDR1_DQ[10]

U1

DDR0_DQ[41]/DDR1_DQ[9]

V2

DDR0_DQ[40]/DDR1_DQ[8]

V5

DDR0_DQ[37]/DDR1_DQ[5]

AB4

DDR0_DQ[33]/DDR1_DQ[1]

AB2

DDR0_DQ[26]/DDR0_DQ[42]

BC4

DDR0_DQ[22]/DDR0_DQ[38]

BF1

DDR0_ECC[3]

AY5

DDR0_DQ[58]/DDR1_DQ[42]

L4

DDR0_DQ[52]/DDR1_DQ[36]

R5

DDR0_DQ[47]/DDR1_DQ[15]

U4

DDR0_DQ[44]/DDR1_DQ[12]

V1

DDR0_DQ[39]/DDR1_DQ[7]

AA1

DDR0_DQSP[8]

AY3

DDR0_DQSN[8]

BA3

DDR0_DQSN[7]/DDR1_DQSN[5]

L3

DDR0_DQSN[6]/DDR1_DQSN[4]

P3

DDR0_DQSN[5]/DDR1_DQSN[1]

U3

DDR0_DQSN[4]/DDR1_DQSN[0]

AA3

DDR0_DQSP[3]/DDR0_DQSP[5]

BC3

DDR0_DQSP[2]/DDR0_DQSP[4]

BF3

DDR0_DQSP[1]

BK3

DDR0_DQSP[0]

BP5

DDR0_DQSP[7]/DDR1_DQSP[5]

M3

DDR0_DQSP[5]/DDR1_DQSP[1]

V3

DDR0_DQSP[6]/DDR1_DQSP[4]

R3

DDR0_DQSN[3]/DDR0_DQSN[5]

BD3

DDR0_DQSP[4]/DDR1_DQSP[0]

AB3

DDR0_DQSN[1]

BL3

DDR0_DQSN[2]/DDR0_DQSN[4]

BG3

DDR0_DQSN[0]

BR5

DDR0_PAR

AG3

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

AU2

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

AU3

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

AE3

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

AU4

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

AN2

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

AN3

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

AT4

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

AH2

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

AP3

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

AN1

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

AP1

DDR0_MA[4]

AP2

DDR0_MA[3]

AP5

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

AN4

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

AP4

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

AH3

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

AD1

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

AG4

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

AH4

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

AU1

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

AH1

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

AH5

DDR0_ODT[3]

AD4

DDR0_ODT[2]

AE1

DDR0_ODT[1]

AE4

DDR0_CS#[3]

AE5

DDR0_ODT[0]

AD3

DDR0_CS#[2]

AD2

DDR0_CS#[1]

AE2

DDR0_CKE[3]

AT5

DDR0_CS#[0]

AD5

DDR0_CKE[1]

AT2

DDR0_CKE[2]

AT3

DDR0_CKE[0]

AT1

DDR0_CLKN[3]

AL1

DDR0_CLKN[2]

AK3

DDR0_CLKP[3]

AL2

DDR0_CLKP[2]

AL3

DDR0_CKP[1]

AK2

DDR0_CKN[1]

AK1

DDR0_CKN[0]

AG2

DDR0_ECC[7]

AY2

DDR0_ECC[5]

BA4

DDR0_ECC[2]

AY4

DDR0_ECC[1]

BA1

DDR0_ECC[0]

BA2

DDR0_DQ[62]/DDR1_DQ[46]

L5

DDR0_DQ[61]/DDR1_DQ[45]

M2

DDR0_DQ[59]/DDR1_DQ[43]

L2

DDR0_DQ[56]/DDR1_DQ[40]

M4

DDR0_DQ[57]/DDR1_DQ[41]

M1

DDR0_DQ[53]/DDR1_DQ[37]

P2

DDR0_DQ[51]/DDR1_DQ[35]

P4

DDR0_DQ[50]/DDR1_DQ[34]

R4

DDR0_DQ[49]/DDR1_DQ[33]

P5

DDR0_DQ[48]/DDR1_DQ[32]

R2

DDR0_DQ[46]/DDR1_DQ[14]

U5

DDR0_DQ[38]/DDR1_DQ[6]

AA2

DDR0_DQ[24]/DDR0_DQ[40]

BD2

DDR0_ALERT#

AU5

DDR0_DQ[1]

BT6

DDR0_DQ[0]

BR6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

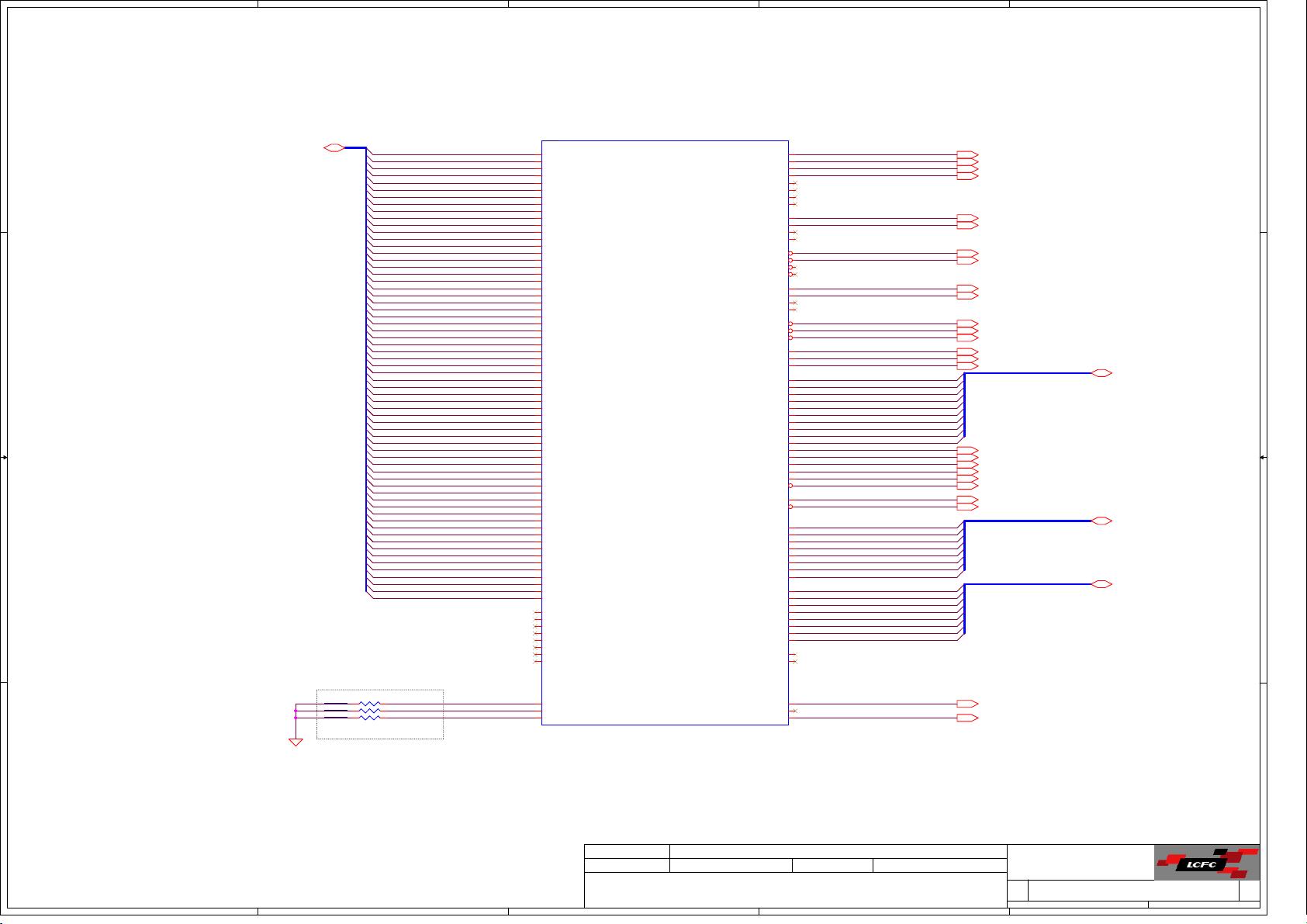

PLACE CLOSE TO CPU

DDR_VREF_CA : Connected to VREF_CA on DIMM CH-A

DDR0_VREF_DQ : NC

DDR1_VREF_DQ : Connected to VREF_CA on DIMM CH-B

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ1

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ17

M_B_DQ16

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ33

M_B_DQ32

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ49

M_B_DQ48

-M_B_DDRCLK1_1066M

M_B_DDRCLK1_1066M

M_B_CKE1

M_B_CKE0

-M_B_CS1

-M_B_CS0

-M_B_DDRCLK0_1066M

M_B_DDRCLK0_1066M

M_B_ODT0

M_B_ODT1

M_B_A16_RAS_N

M_B_BA0

M_B_A15_CAS_N

M_B_A14_WE_N

M_B_BG0

M_B_BA1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A12

M_B_A11

M_B_A10_AP

M_B_A9

-M_B_ACT

M_B_BG1

M_B_A13

M_B_A1

M_B_A0

-M_B_DQS2

-M_B_DQS3

-M_B_DQS4

-M_B_DQS5

-M_B_DQS6

-M_B_DQS7

M_B_DQS3

M_B_DQS2

M_B_DQS1

M_B_DQS0

M_B_DQS6

M_B_DQS5

M_B_DQS4

-M_B_DQS1

-M_B_DQS0

M_B_DQ0

M_B_DQS7

M_A_VREF_CA_CPU

M_B_VREF_DQ_CPU

-M_B_ALERT

M_B_PARITY

DDR_RCOMP2

DDR_RCOMP1

DDR_RCOMP0

-M_B_DDRCLK1_1066M [28]

-M_B_DDRCLK0_1066M [28]

M_B_DDRCLK0_1066M [28]

M_B_DDRCLK1_1066M [28]

M_B_ODT0 [28]

M_B_ODT1 [28]

M_B_CKE1 [28]

M_B_CKE0 [28]

-M_B_CS1 [28]

-M_B_CS0 [28]

M_B_BG0 [28]

M_B_BA1 [28]

M_B_BA0 [28]

-M_B_ALERT [28]

-M_B_ACT [28]

M_B_PARITY [28]

M_B_A11 [28]

M_B_A13 [28]

M_B_A12 [28]

M_B_BG1 [28]

M_B_A10_AP [28]

M_A_VREF_CA_CPU [27]

M_B_VREF_DQ_CPU [28]

M_B_DQ[0..63][28]

M_B_A15_CAS_N [28]

M_B_A14_WE_N [28]

M_B_A16_RAS_N [28]

M_B_DQS[0..7] [28]

-M_B_DQS[0..7] [28]

M_B_A[0..9] [28]

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : DDR4 CH-B

Custom

499

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : DDR4 CH-B

Custom

499

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet

of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : DDR4 CH-B

Custom

499

Tuesday, November 03, 2015

2015/07/16

2016/01/16

RC0303 100_0402_1%

12

RC0301 121_0402_1%

12

RC0302 75_0402_1%

12

DDR CHANNEL B

BGA1440

SKYLAKE_HALO

2 OF 14

UC1B

SKYLAKE-H-CPU_BGA1440

DDR1_DQ[0]/DDR0_DQ[16]

BT11

DDR1_DQ[3]/DDR0_DQ[19]

BR8

DDR1_DQ[4]/DDR0_DQ[20]

BP11

DDR1_DQ[5]/DDR0_DQ[21]

BN11

DDR1_DQ[6]/DDR0_DQ[22]

BP8

DDR1_DQ[7]/DDR0_DQ[23]

BN8

DDR1_DQ[8]/DDR0_DQ[24]

BL12

DDR1_DQ[9]/DDR0_DQ[25]

BL11

DDR1_DQ[11]/DDR0_DQ[27]

BJ8

DDR1_DQ[12]/DDR0_DQ[28]

BJ11

DDR1_DQ[14]/DDR0_DQ[30]

BL7

DDR1_DQ[15]/DDR0_DQ[31]

BJ7

DDR1_DQ[2]/DDR0_DQ[18]

BT8

DDR1_DQ[1]/DDR0_DQ[17]

BR11

DDR1_ECC[3]

AW8

DDR1_ECC[4]

AY10

DDR1_ECC[5]

AW10

DDR1_ECC[6]

AY7

DDR1_ECC[7]

AW7

DDR1_DQ[61]

M10

DDR1_DQ[60]

L10

DDR1_DQ[59]

M8

DDR1_DQ[58]

L7

DDR1_DQ[57]

M11

DDR1_DQ[56]

L11

DDR1_DQ[55]

P8

DDR1_DQ[54]

R7

DDR1_DQ[53]

P10

DDR1_ODT[0]

AF7

DDR1_CS#[3]

AE10

DDR1_CS#[2]

AF10

DDR1_ODT[1]

AE8

DDR1_ODT[2]

AE9

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

AH10

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

AH9

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

AJ9

DDR1_DQSN[6]

R9

DDR0_VREF_DQ

BP13

DDR_VREF_CA

BN13

DDR1_DQSN[5]/DDR1_DQSN[3]

W9

DDR1_PAR

AJ7

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

AT9

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

AR7

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

AF9

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

AN11

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

AR10

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

AH7

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

AN8

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

AR11

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

AN10

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

AN7

DDR1_MA[3]

AL5

DDR1_MA[4]

AL6

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

AM6

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

AK5

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

AK6

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

AR9

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

AH8

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

AH11

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

AF8

DDR1_ODT[3]

AE11

DDR1_CS#[1]

AE7

DDR1_CKE[3]

AT11

DDR1_CS#[0]

AF11

DDR1_CKE[2]

AT7

DDR1_CKE[1]

AT10

DDR1_CKE[0]

AT8

DDR1_CLKN[3]

AJ11

DDR1_CLKP[3]

AJ10

DDR1_CLKN[2]

AM10

DDR1_CLKP[2]

AM11

DDR1_CKP[1]

AM7

DDR1_CKN[1]

AM8

DDR1_CKP[0]

AM9

DDR1_CKN[0]

AN9

DDR1_ECC[2]

AY8

DDR1_ECC[1]

AY11

DDR1_ECC[0]

AW11

DDR1_DQ[63]

L8

DDR1_DQ[62]

M7

DDR1_DQ[51]

R8

DDR1_DQ[52]

R10

DDR1_DQ[50]

P7

DDR1_DQ[49]

P11

DDR1_DQ[48]

R11

DDR1_DQ[46]/DDR1_DQ[30]

V7

DDR1_DQ[47]/DDR1_DQ[31]

V8

DDR1_DQ[45]/DDR1_DQ[29]

W10

DDR1_DQ[43]/DDR1_DQ[27]

V11

DDR1_DQ[44]/DDR1_DQ[28]

W11

DDR1_DQ[40]/DDR1_DQ[24]

W8

DDR1_DQ[42]/DDR1_DQ[26]

V10

DDR1_DQ[41]/DDR1_DQ[25]

W7

DDR1_DQ[39]/DDR1_DQ[23]

AC7

DDR1_DQ[38]/DDR1_DQ[22]

AC8

DDR1_DQ[37]/DDR1_DQ[21]

AA8

DDR1_DQ[29]/DDR0_DQ[61]

BB10

DDR1_DQ[23]/DDR0_DQ[55]

BF7

DDR1_DQ[20]/DDR0_DQ[52]

BF11

DDR1_DQ[21]/DDR0_DQ[53]

BF10

DDR1_DQ[17]/DDR0_DQ[49]

BG10

DDR1_DQ[18]/DDR0_DQ[50]

BG8

DDR1_DQ[16]/DDR0_DQ[48]

BG11

DDR1_DQ[13]/DDR0_DQ[29]

BJ10

DDR1_DQ[10]/DDR0_DQ[26]

BL8

DDR1_DQ[19]/DDR0_DQ[51]

BF8

DDR1_DQ[26]/DDR0_DQ[58]

BB8

DDR1_VREF_DQ

BR13

DDR1_DQSN[8]

AY9

DDR1_DQSP[8]

AW9

DDR1_DQSP[7]

L9

DDR1_DQSP[6]

P9

DDR1_DQSP[5]/DDR1_DQSP[3]

V9

DDR1_DQSP[4]/DDR1_DQSP[2]

AA9

DDR1_DQSP[3]/DDR0_DQSP[7]

BB9

DDR1_DQSP[2]/DDR0_DQSP[6]

BF9

DDR1_DQSP[1]/DDR0_DQSP[3]

BJ9

DDR1_DQSP[0]/DDR0_DQSP[2]

BR9

DDR1_DQSN[7]

M9

DDR1_DQSN[4]/DDR1_DQSN[2]

AC9

DDR1_DQSN[3]/DDR0_DQSN[7]

BC9

DDR1_DQSN[2]/DDR0_DQSN[6]

BG9

DDR1_DQSN[1]/DDR0_DQSN[3]

BL9

DDR1_DQSN[0]/DDR0_DQSN[2]

BP9

DDR1_ALERT#

AR8

DDR1_DQ[36]/DDR1_DQ[20]

AA7

DDR1_DQ[35]/DDR1_DQ[19]

AC10

DDR1_DQ[34]/DDR1_DQ[18]

AC11

DDR1_DQ[33]/DDR1_DQ[17]

AA10

DDR1_DQ[32]/DDR1_DQ[16]

AA11

DDR1_DQ[31]/DDR0_DQ[63]

BB7

DDR1_DQ[30]/DDR0_DQ[62]

BC7

DDR1_DQ[28]/DDR0_DQ[60]

BC10

DDR1_DQ[27]/DDR0_DQ[59]

BC8

DDR1_DQ[25]/DDR0_DQ[57]

BC11

DDR1_DQ[24]/DDR0_DQ[56]

BB11

DDR1_DQ[22]/DDR0_DQ[54]

BG7

DDR_RCOMP[0]

G1

DDR_RCOMP[1]

H1

DDR_RCOMP[2]

J2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

PEG_COMP_W12mil

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

PEG_RXP0

PEG_RXN0

PEG_RXP1

PEG_RXN1

PEG_RXP2

PEG_RXN2

PEG_RXP3

PEG_RXN3

PEG_TXP0_C

PEG_TXN0_C

PEG_TXP0

PEG_TXN0

PEG_TXP1_C

PEG_TXN1_C

PEG_TXP2_C

PEG_TXN2_C

PEG_TXP3_C

PEG_TXN3_C

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

DMI_TXP0[15]

DMI_TXN0[15]

DMI_TXP1[15]

DMI_TXN1[15]

DMI_TXP2[15]

DMI_TXN2[15]

DMI_TXP3[15]

DMI_TXN3[15]

DMI_RXP0 [15]

DMI_RXN0 [15]

DMI_RXP1 [15]

DMI_RXN1 [15]

DMI_RXP2 [15]

DMI_RXN2 [15]

DMI_RXP3 [15]

DMI_RXN3 [15]

PEG_TXP[3:0] [31]

PEG_TXN[3:0] [31]

PEG_RXP[3:0][31]

PEG_RXN[3:0][31]

VCCCPUIO

Size

Document Number Rev

Date: Sheet of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : PEG/DMI

Custom

599

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : PEG/DMI

Custom

599

Tuesday, November 03, 2015

2015/07/16

2016/01/16

Size

Document Number Rev

Date: Sheet of

Security Classification

LC Future Center Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

Issued Date

Deciphered Date

Title

NM-A611

0.1

CPU SKL-H : PEG/DMI

Custom

599

Tuesday, November 03, 2015

2015/07/16

2016/01/16

C9042 0.22U_0201_6.3V6-KDIS@

1 2

RC0501

24.9_0402_1%

1 2

C9057 0.22U_0201_6.3V6-KDIS@

1 2

C9053 0.22U_0201_6.3V6-KDIS@

1 2

C9058 0.22U_0201_6.3V6-KDIS@

1 2

C9060 0.22U_0201_6.3V6-KDIS@

1 2

C9059 0.22U_0201_6.3V6-KDIS@

1 2

SKYLAKE_HALO

BGA1440

3 OF 14

UC1C

SKYLAKE-H-CPU_BGA1440

PEG_RXN[0]

D25

PEG_RXN[2]

D23

PEG_RXP[2]

E23

PEG_RXN[1]

F24

PEG_RXP[13]

F12

DMI_TXN[3]

B4

DMI_TXP[3]

D4

DMI_TXN[2]

A5

DMI_TXP[2]

B5

DMI_TXP[1]

C6

DMI_TXN[1]

B6

DMI_TXN[0]

A8

DMI_TXP[0]

B8

DMI_RXP[3]

J8

DMI_RXN[3]

J9

DMI_RXN[2]

E5

DMI_RXP[2]

D5

DMI_RXP[1]

E6

DMI_RXN[1]

F6

DMI_RXP[0]

D8

DMI_RXN[0]

E8

PEG_RCOMP

G2

PEG_RXP[15]

F10

PEG_RXP[14]

D11

PEG_RXN[15]

E10

PEG_RXP[8]

D17

PEG_RXN[7]

F18

PEG_RXP[7]

E18

PEG_RXN[3]

F22

PEG_RXP[1]

E24

PEG_RXP[3]

E22

PEG_RXP[4]

E21

PEG_RXN[4]

D21

PEG_RXP[5]

E20

PEG_RXP[6]

E19

PEG_RXP[10]

D15

PEG_RXN[10]

E15

PEG_RXP[11]

F14

PEG_RXN[11]

E14

PEG_RXP[12]

D13

PEG_RXN[13]

E12

PEG_RXN[14]

E11

PEG_TXP[0]

B25

PEG_TXN[0]

A25

PEG_TXP[1]

B24

PEG_TXN[1]

C24

PEG_TXN[2]

A23

PEG_TXP[2]

B23

PEG_TXN[3]

C22

PEG_TXP[3]

B22

PEG_TXP[4]

B21

PEG_TXN[5]

C20

PEG_TXN[4]

A21

PEG_TXP[5]

B20

PEG_TXN[6]

A19

PEG_TXP[6]

B19

PEG_TXP[7]

B18

PEG_TXP[8]

A17

PEG_TXN[10]

B15

PEG_TXP[10]

A15

PEG_TXN[9]

B16

PEG_TXP[11]

C14

PEG_TXN[11]

B14

PEG_TXN[12]

B13

PEG_TXP[12]

A13

PEG_TXN[13]

B12

PEG_TXP[13]

C12

PEG_TXN[14]

B11

PEG_TXP[14]

A11

PEG_TXP[15]

C10

PEG_TXN[15]

B10

PEG_RXN[12]

E13

PEG_RXN[9]

E16

PEG_RXN[8]

E17

PEG_TXP[9]

C16

PEG_TXN[8]

B17

PEG_RXP[9]

F16

PEG_TXN[7]

C18

PEG_RXN[5]

F20

PEG_RXN[6]

D19

PEG_RXP[0]

E25

C9055 0.22U_0201_6.3V6-KDIS@

1 2

C9054 0.22U_0201_6.3V6-KDIS@

1 2

剩余95页未读,继续阅读

asdsafasdfgh

- 粉丝: 10

- 资源: 29

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0