没有合适的资源?快使用搜索试试~ 我知道了~

PCB Designer's SI Guide.pdf

需积分: 0 20 下载量 154 浏览量

2009-04-05

15:34:05

上传

评论

收藏 2.86MB PDF 举报

温馨提示

试读

144页

信号完整性 pcb 知道手册 很有学习的价值 大家一起来学学学习把

资源详情

资源评论

资源推荐

PCB Designer’s

SI Guide

A basic guide for SI and crosstalk for a PCB designer

Preface

What the heck is SI?

Why and what should I Simulate?

What is the strategy for SI Analysis?

Is crosstalk happens when you talk in the mobile?

What do you mean by transmission line?

Topology??? Are you kidding?

Delay?? How about a schedule change?

This is a collection of articles, which are found in web and other sources trying to answer your

questions. Hope it will be helpful

PCB Designer’s SI Guide Page 2 Venkata

Table of Content

Basics of SI___________________________________________________________________5

1.1 When Speed is important? _____________________________________________5

1.1.1 Acceptable Voltage and timing values ________________________________5

1.2 Signal Integrity______________________________________________________5

1.2.1 Waveform Voltage Accuracy_______________________________________5

1.2.2 Timing_________________________________________________________5

1.3 Speed of currently used logic families ____________________________________5

1.3.1 Transition Electrical Length (TEL) __________________________________6

1.3.2 Critical length___________________________________________________6

1.3.3 What is Transmission Line? ________________________________________6

1.3.4 What is moving in a Transmission line?_______________________________6

1.3.5 Power Plane Definition____________________________________________6

1.3.6 The concept of Ground ____________________________________________7

1.4 STRIPLINE circuit with Electromagnetic field _____________________________7

1.5 RLC Transmission Line Model _________________________________________8

1.5.1 What is Impedance? ______________________________________________8

1.5.2 A Practical impedance equation for microstrip _________________________8

1.5.3 What is relative dielectric constant Er? _______________________________9

2 Interconnections for High Speed Digital Circuits _______________________________10

2.1.1 Summary______________________________________________________10

2.2 Examples of dynamic interfacing problems _______________________________10

2.3 IC Technology and Signal Integrity_____________________________________12

2.4 Speed and distance __________________________________________________14

2.5 Digital signals: Static interfacing _______________________________________15

2.6 Digital signals: Dynamic interfacing ____________________________________16

2.7 Review questions ___________________________________________________18

3 Interconnection Models____________________________________________________20

3.1 Summary__________________________________________________________20

3.2 Reference model for interconnection analysis _____________________________20

3.3 Receiver model_____________________________________________________21

3.4 RC interconnection model ____________________________________________23

3.5 Parameters of the interconnection ______________________________________25

3.6 Refined models _____________________________________________________26

3.7 Review question ____________________________________________________28

4 Transmission Line Models _________________________________________________31

4.1 Summary__________________________________________________________31

4.2 Transmission line models _____________________________________________31

4.3 Loss-less transmission lines ___________________________________________32

4.4 Critical Length _____________________________________________________34

4.5 Reference transmission line model______________________________________35

4.6 Line driving _______________________________________________________36

4.7 Propagation and reflected waves _______________________________________37

4.8 A sample system____________________________________________________39

4.9 Review questions ___________________________________________________42

PCB Designer’s SI Guide Page 3 Venkata

5 Analysis techniques _______________________________________________________45

5.1 Summary__________________________________________________________45

5.2 Transmission time and skew___________________________________________45

5.3 Effects of termination resistance _______________________________________46

5.4 Lattice diagram_____________________________________________________48

5.5 Examples of Real Lines ______________________________________________49

5.6 Simulation code ____________________________________________________51

5.7 Examples of results__________________________________________________54

5.8 Review questions ___________________________________________________55

6 Design guide for interconnection ____________________________________________57

6.1 Summary__________________________________________________________57

6.2 Incident wave switching ______________________________________________57

6.3 Effects of capacitive loading __________________________________________58

6.4 Termination circuits _________________________________________________59

6.4.1 Passive termination______________________________________________60

6.4.2 Low power termination___________________________________________61

6.4.3 Active low power termination circuit. _______________________________61

6.5 Driving point-to-point lines ___________________________________________62

6.6 Driving bused lines __________________________________________________64

6.7 Design guidelines ___________________________________________________67

6.8 Review questions ___________________________________________________67

7 Signal Integrity in Digital Circuits___________________________________________70

7.1 Crosstalk __________________________________________________________70

7.1.1 Summary______________________________________________________70

7.2 Examples of signal integrity problems ___________________________________70

7.3 Simplified Model for Crosstalk Analysis _________________________________71

7.4 Forward and backward crosstalk _______________________________________74

7.5 Examples__________________________________________________________76

7.6 Near-end and Far-end crosstalk ________________________________________80

7.7 Review questions ___________________________________________________81

8 Design Guide to Handle Crosstalk ___________________________________________85

8.1 Summary__________________________________________________________85

8.2 Effects of Crosstalk__________________________________________________85

8.3 Passive countermeasures _____________________________________________86

8.4 Active Control of Crosstalk ___________________________________________92

8.5 Review questions ___________________________________________________94

9 Ground Bounce and Switching Noise_________________________________________97

9.1 Summary__________________________________________________________97

9.2 The totem pole Current Spike__________________________________________97

9.3 Current flow in the output capacitance__________________________________100

9.4 Total Ground Bounce _______________________________________________100

9.5 Review questions __________________________________________________105

10 Design Guide for Ground & Power Distribution_____________________________107

10.1 Summary_________________________________________________________107

PCB Designer’s SI Guide Page 4 Venkata

10.2 Decoupling Capacitors ______________________________________________107

10.3 Placement of bypass Capacitors _______________________________________113

10.4 Ground and power distribution________________________________________114

10.5 Clock distribution__________________________________________________115

10.6 Review Questions __________________________________________________118

11 Laboratory Experience _________________________________________________120

11.1 Summary_________________________________________________________120

11.2 Aim of the experience_______________________________________________120

11.3 Generator Parameters _______________________________________________122

11.4 Cable Parameters __________________________________________________123

11.5 Mismatch at driver and at termination __________________________________124

11.6 Capacitive Load ___________________________________________________125

11.7 7. Time-domain reflectometer ________________________________________127

11.8 Driving the line with logic devices_____________________________________128

12 SI Analysis Strategy____________________________________________________133

12.1.1 A modern high-speed design methodology must involve the at least the

following: ____________________________________________________________133

12.2 POSSIBLE HIGH-SPEED DESIGN APPROACHES______________________133

12.2.1 There are two fundamental types of conditions that need to be considered for

solution space analysis:__________________________________________________134

12.3 SOLUTION SPACE ANALYSIS _____________________________________135

12.3.1 STEP 1 — DEFINING THE INITIAL TOPOLOGY __________________135

12.3.2 STEP 2 — DEFINE MANUFACTURING TOLERANCES AND THEIR

MIN/MAX VALUES ___________________________________________________135

12.3.3 STEP 3 — DEFINE THE STARTING POINT FOR DESIGN VARIANCES

136

12.3.4 STEP 4 — SET UP AND RUN A NUMBER OF SIMULATION CASES _136

12.3.5 STEP 5 — EXAMINE THE SIMULATION RESULTS, IDENTIFY WHICH

CASES FAILED AND WHY ____________________________________________136

12.3.6 STEP 6 — ADAPT THE TOPOLOGY AND DESIGN RULES AS

APPROPRIATE _______________________________________________________137

12.3.7 STEP 7 — REPEAT STEPS 4-6 UNTIL THE TOPOLOGY CONVERGES

ON A SET OF VALUES THAT PASS FOR ALL CASES ANALYZED __________137

12.3.8 STEP 8 — DERIVE DESIGN RULES FOR THE TARGET CAD SYSTEM

137

12.3.9 STEP 9 — DRIVE THE CAD RULES INTO THE CAD DATABASE, AND

USE THEM TO DRIVE THE PLACEMENT/ROUTING PROCESSES ___________138

12.3.10 STEP 10 — POST LAYOUT SI ANALYSIS ______________________139

12.4 CONCLUSION____________________________________________________139

13 Glossary _____________________________________________________________141

PCB Designer’s SI Guide Page 5 Venkata

Basics of SI

1.1 When Speed is important?

Speed is important when; the edge rate (rise or fall time) of a clock is fast enough that the signal can

change from one logic state to the other in the same or less time than it takes the signal to travel the

length of the wire or net.

1.1.1 Acceptable Voltage and timing values

Any voltage level within the values of the Vin Maximum to Vin Minimum is a valid logic signal.

Excursions outside these limits will cause logic malfunction. SI engineering involves; developing

design rules that insures all logic signals fall within the envelope for any allowed combination of

components, temperature and power supply voltage.

1.2 Signal Integrity

SI has 2 components that are interlinked; voltage accuracy of the waveform and timing of arrival of

switching edges at the input.

1.2.1 Waveform Voltage Accuracy

It is affected by impedance matches, ground bounce and coupling etc.

1.2.2 Timing

Is affected by propagation delay variations in ICs, travel time on wires, and variation in edge rates of

ICs.

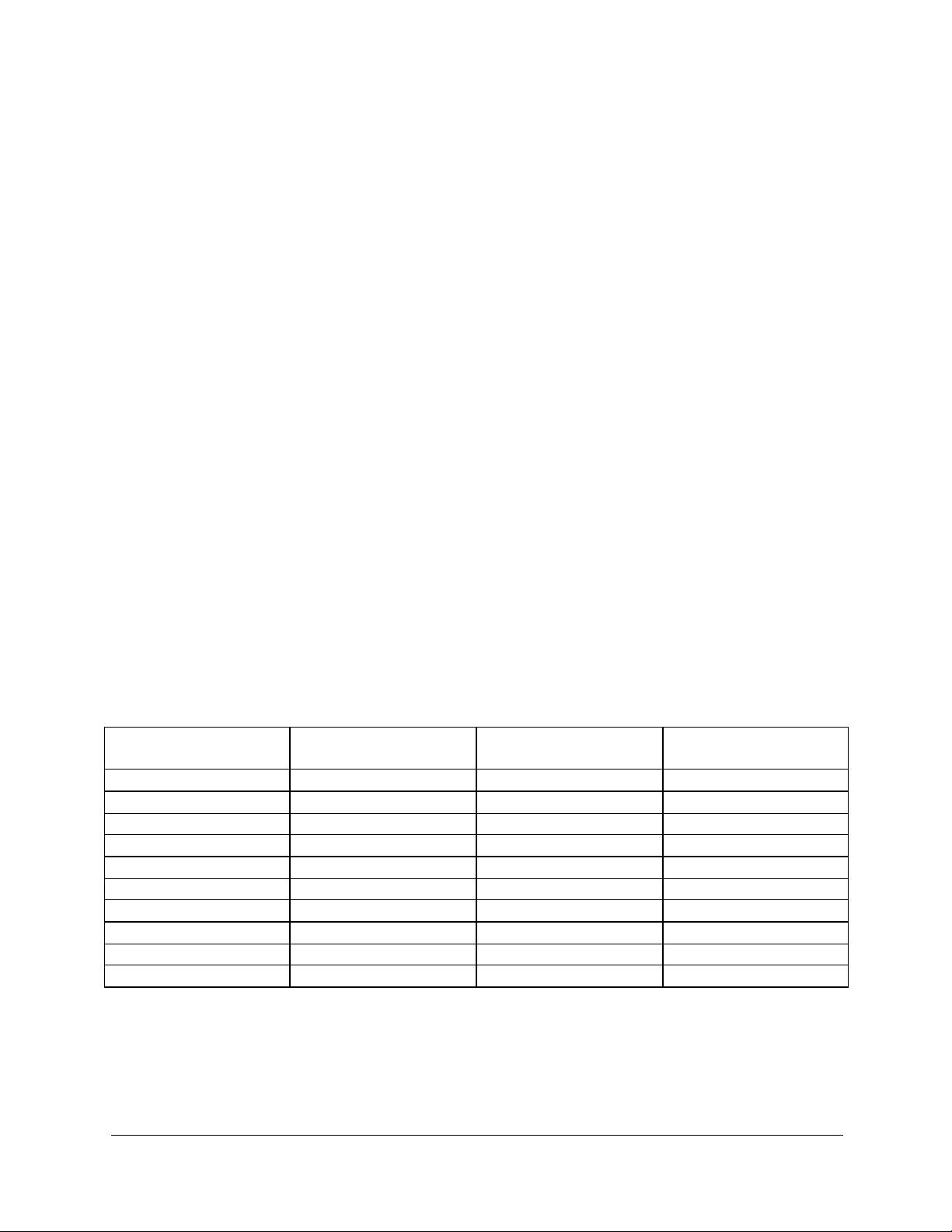

1.3 Speed of currently used logic families

Logic type Typical edge speed

(nSEC)

Transition electrical

length in FR-4 (inches)

Critical length in

inches

STANDARD TTL 5.0 29.0 14.5

ASTTL 1.9 10.9 5.45

FTTL 1.2 6.9 3.45

10K ECL 2.5 14.4 7.2

BTL 1.0 5.8 3.9

CMOS/DS 1.5 9.0 4.5

LVDS 0.3 1.73 0.86

100K ECL 0.5 2.88 1.44

GA AS 106 0.3 1.73 0.86

GTL+(PENTPRO) 0.3 1.73 0.86

Overshoot and undershoot problems will start to occur at less than 1/3 of the Transition Electrical

Length (TEL) and may require series termination of transmission lines, as well as impedance control.

剩余143页未读,继续阅读

MJTOK

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于keras+fasterRCNN,在VOC格式的口罩数据集上训练,检测人群中有无戴口罩python源码+模型

- 管道内检测缺陷数据库管理系统源码+文档说明+sln

- 毕业设计-低功耗STM32F411开发板(原理图+PCB源文件+官方例程+驱动等)源码+文档说明+截图

- 基于yolov5-tensorRT检测+发动机缸体内壁缺陷检测系统源码+文档说明

- 基于C++实现的锂电池缺陷检测源码+文档说明

- push_version

- 软件自制图像批量压缩工具

- 经典缺陷检测算法源码整理包含PaDiM(2020ICPR)、PatchCore(2022CVPR)、SimpleNet+文档说明

- 基于深度学习的抗梯度噪声的缺陷检测器python源码+文档说明+模型的预训练

- 基于python+pytorch+mysql实现停车场车牌识别管理系统源码+文档说明

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0