SPRS087E − FEBRUARY 1999 − REVISED JANUARY 2004

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

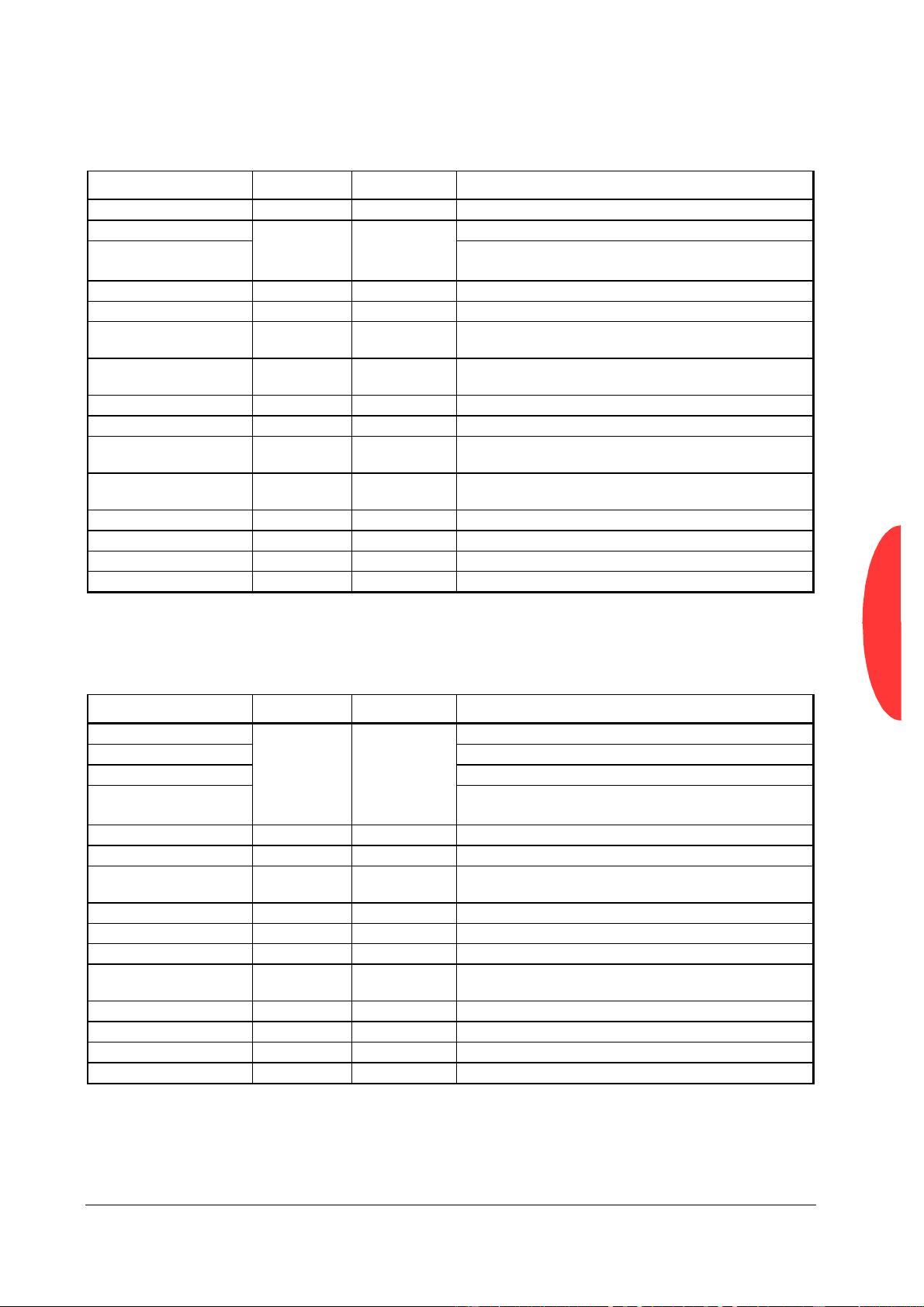

D High-Performance Floating-Point Digital

Signal Processor (DSP):

− TMS320VC33-150

− 13-ns Instruction Cycle Time

− 150 Million Floating-Point Operations

Per Second (MFLOPS)

− 75 Million Instructions Per Second

(MIPS)

− TMS320VC33-120

− 17-ns Instruction Cycle Time

− 120 MFLOPS

− 60 MIPS

D 34K × 32-Bit (1.1-Mbit) On-Chip Words of

Dual-Access Static Random-Access

Memory (SRAM) Configured in 2 × 16K Plus

2 × 1K Blocks to Improve Internal

Performance

D x5 Phase-Locked Loop (PLL) Clock

Generator

D Very Low Power: < 200 mW @ 150 MFLOPS

D 32-Bit High-Performance CPU

D 16-/32-Bit Integer and 32-/40-Bit

Floating-Point Operations

D Four Internally Decoded Page Strobes to

Simplify Interface to I/O and Memory

Devices

D Boot-Program Loader

D EDGEMODE Selectable External Interrupts

D 32-Bit Instruction Word, 24-Bit Addresses

D Eight Extended-Precision Registers

D On-Chip Memory-Mapped Peripherals:

− One Serial Port

− Two 32-Bit Timers

− Direct Memory Access (DMA)

Coprocessor for Concurrent I/O and CPU

Operation

D Fabricated Using the 0.18-µm (l

eff

-Effective

Gate Length) TImeline Process

Technology by Texas Instruments (TI)

D 144-Pin Low-Profile Quad Flatpack (LQFP)

(PGE Suffix)

D Two Address Generators With Eight

Auxiliary Registers and Two Auxiliary

Register Arithmetic Units (ARAUs)

D Two Low-Power Modes

D Two- and Three-Operand Instructions

D Parallel Arithmetic/Logic Unit (ALU) and

Multiplier Execution in a Single Cycle

D Block-Repeat Capability

D Zero-Overhead Loops With Single-Cycle

Branches

D Conditional Calls and Returns

D Interlocked Instructions for

Multiprocessing Support

D Bus-Control Registers Configure

Strobe-Control Wait-State Generation

D 1.8-V (Core) and 3.3-V (I/O) Supply Voltages

D On-Chip Scan-Based Emulation Logic,

IEEE Std 1149.1

†

(JTAG)

description

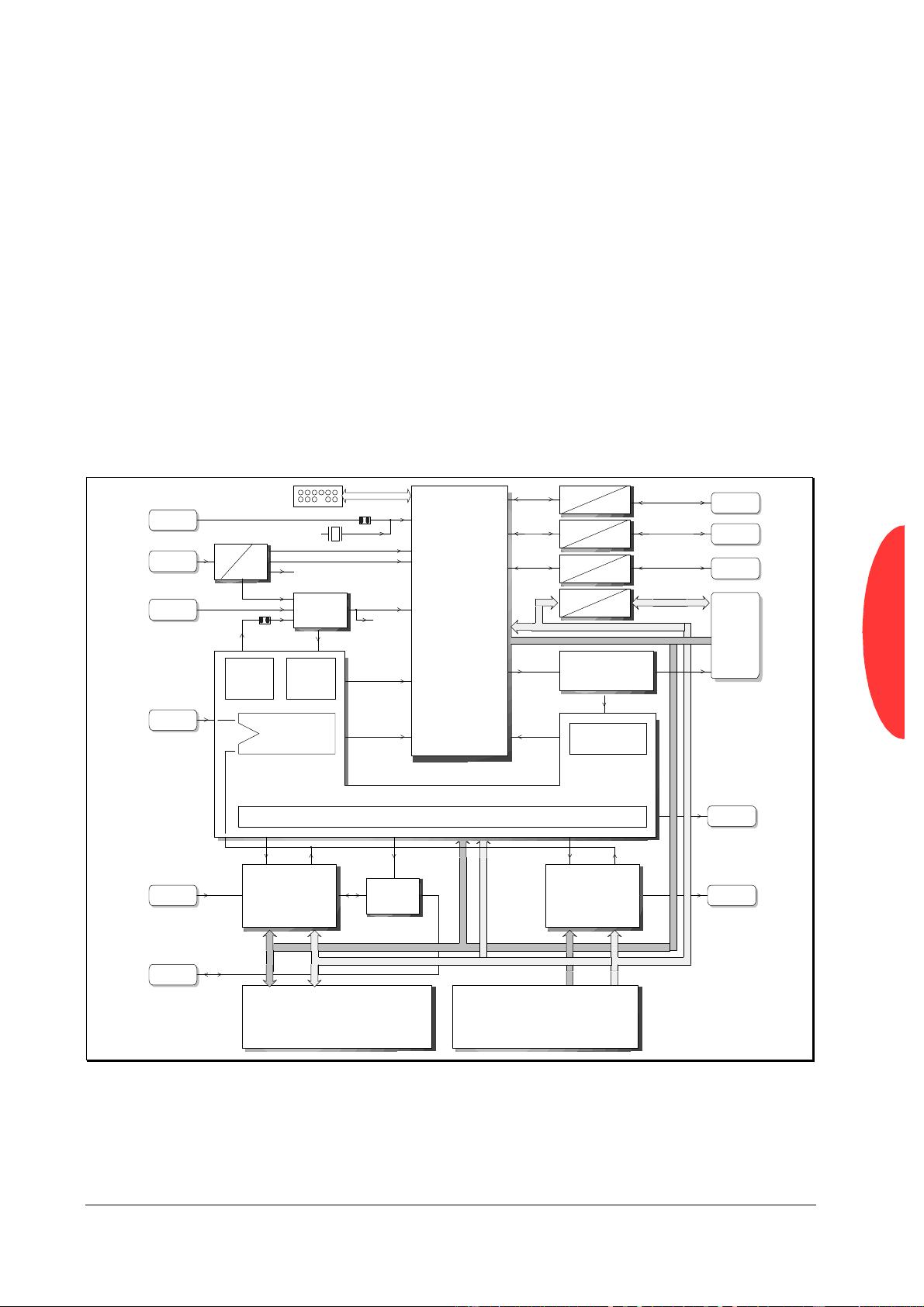

The TMS320VC33 DSP is a 32-bit, floating-point processor manufactured in 0.18-µm four-level-metal CMOS

(TImeline) technology. The TMS320VC33 is part of the TMS320C3x generation of DSPs from Texas

Instruments.

The TMS320C3x’s internal busing and special digital-signal-processing instruction set have the speed and

flexibility to execute up to 150 million floating-point operations per second (MFLOPS). The TMS320VC33

optimizes speed by implementing functions in hardware that other processors implement through software or

microcode. This hardware-intensive approach provides performance previously unavailable on a single chip.

The TMS320VC33 can perform parallel multiply and ALU operations on integer or floating-point data in a single

cycle. Each processor also possesses a general-purpose register file, a program cache, dedicated ARAUs,

internal dual-access memories, one DMA channel supporting concurrent I/O, and a short machine-cycle time.

High performance and ease of use are the results of these features.

Copyright 2004, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications o

f

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

†

IEEE Standard 1149.1-1990 Standard-Test-Access Port

!"# $%

$ ! ! & '

$$ ()% $ !* $ #) #$

* ## !%

TImeline is a trademark of Texas Instruments.

Other trademarks are the property of their respective owners.