没有合适的资源?快使用搜索试试~ 我知道了~

资源详情

资源评论

资源推荐

第一节 概述

一.VHDL 简介

VHDL(Very high speed intergated circuit Hardware

Description Language):非常高速集成电路的硬件描述语言。

20 世纪 80 年代诞生于美国国防部的一项研究计划,目的是使电路的

设计能够以文字的方式保存下来。

被列为 IEEE1076 标准,也成为工业界的标准。

2.Verilog HDL 语言简介

Verilog HDL 它是在 C 语言的基础上发展起来的,由

GDA(Gateway Design Automation)公司创造的,1989 年

cadence 公司收购了 GDA 公司,使得 Verilog HDL 成为了该公司

的独家专利。1990 年 Cadence 公司公开发表了 Verilog HDL,

并成立 LVI 组织以促进 Verilog HDL 成为 IEEE 标准,即 IEEE

Standard 1364-1995。

Verilog HDL 的最大特点就是易学易用,如果有 C 语言的编程经验,

可以在一个较短的时间内很快的学习和掌握,Verilog HDL 语言的

系统抽象能力稍逊于 VHDL,而对门级开关电路的描述能力则优于

VHDL。

二、VHDL 的优点

1. 支持层次化设计

2. 具有多层次描述系统硬件功能的能力

3. 具有丰富的仿真语句和库函数

4. VHDL 语句的行为描述能力和程序结构决定了他具有支持大规模设

计的分解和已有设计的再利用功能

VHDL 的优点

5. 对设计的描述具有相对独立性,与硬件的结构无关

6.可以利用 EDA 工具进行逻辑综合和优化,并自动将 VHDL 描述转

化为门级网表。

7. 具有可移植性,可以在不同的设计环境和系统平台中使用。

8. 具有良好的可读性。

三、VHDL 与高级语言的区别

1.某些并行语句可以自动的重复执行,不需要用循环指令来保证。

2.VHDL 中的许多语句不是按排列顺序执行的,而是可以同时执行的

(VHDL 的并行性)。

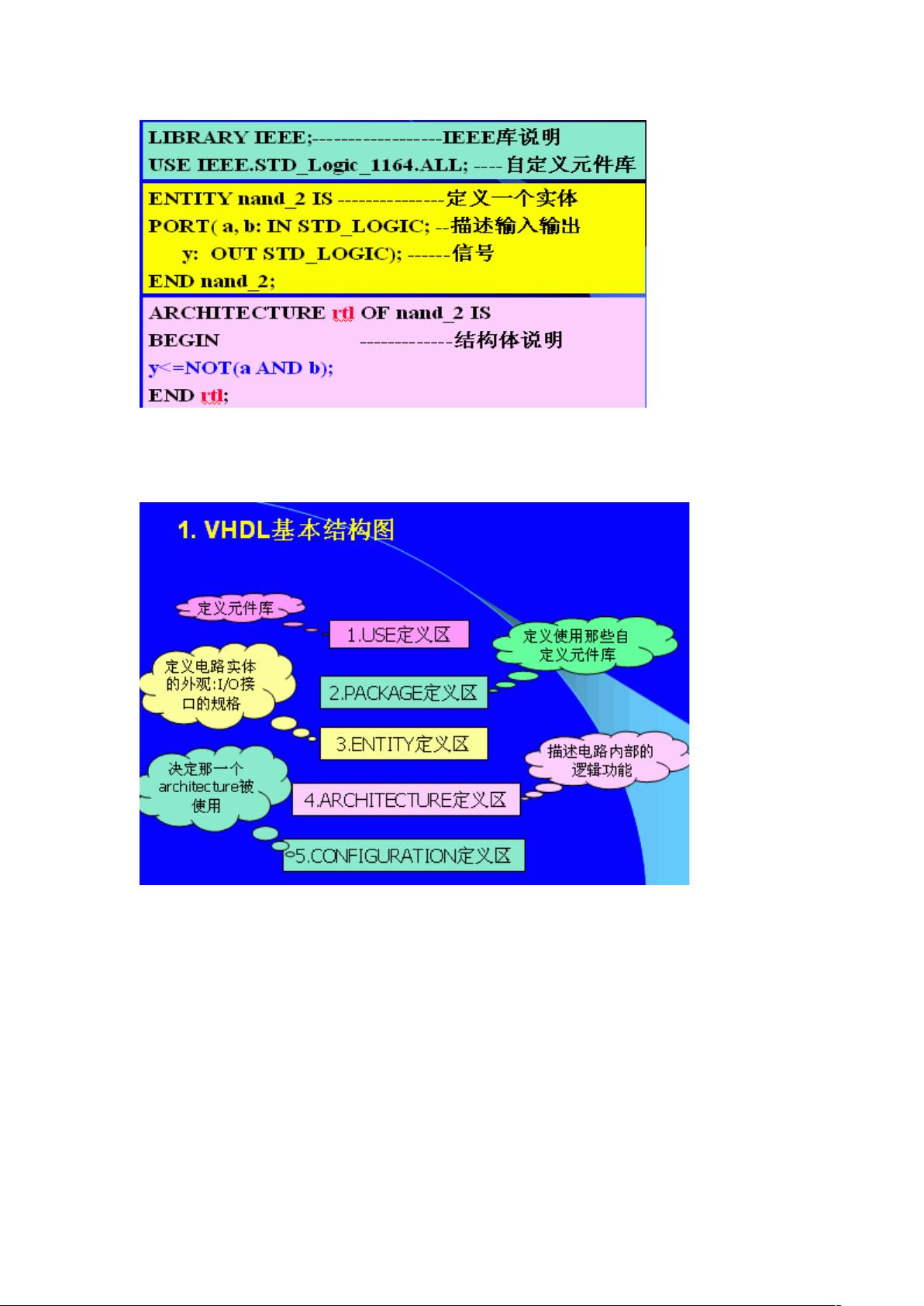

第二节 VHDL 程序结构

一、VHDL 的基本结构

1. VHDL 基本结构图

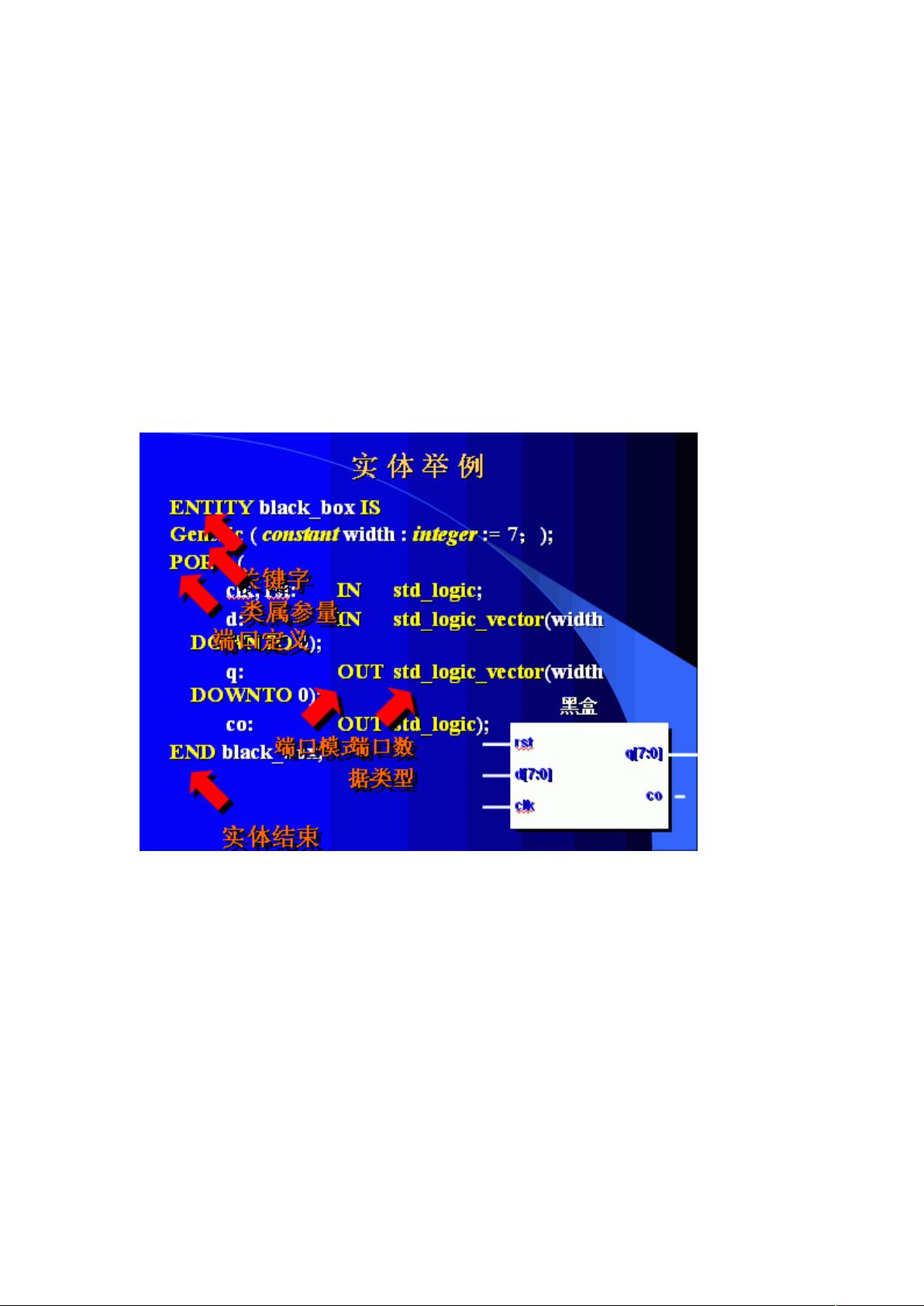

2. 实体说明

功能:描述设计模块的输入/输出信号或引脚,并给出设计模块与外界

的接口。实体类似一个“黑盒”,实体描述了“黑盒”的输入输出口。

格式:

ENTITY 实体名 IS

[GENERIC(类属表);]

[PORT(端口表);]

END [ENTITY] [实体名]

实 体 名

实体名实际上是器件名,最好根据相应的电路功能确定。如 4 位 2 进

制计数器用 counter4b;8 位加法器用 add8b;3/8 译码器用

ym_38。

实体名必须与文件名相同,否则无法编译。

实体名不能用工具库中定义好的元件名。

实体名不能用中文,也不能用数字开头。

类 属 表

类属表:用以将信息参数传递到实体。

类属表的一般格式为:

GENERIC(常数名:数据类型[:=设定值]

……)

GENERIC(awidth : INTEGER:=3;

timex: time );

其中:常数名由设计者确定;数据类型通常取 INTEGER 或 time 等;

在表中提供时间参数、总线宽度等信息

端 口 表

端口表:指明实体的输入、输出信号极其模式。

端口表的一般格式为:

PORT(端口名:端口模式 数据类型…… )

端口模式:共四种: IN(输入)、 OUT(输出)、 INOUT(双向

端口) 、 BUFFER(输出并向内部反馈)

数据类型:VHDL 作为一种强类型语言,必须对数据对象(常量、变

量、信号)规定取值范围,即对传输或存储数据的类型作明确的界定。

练 习 一

编写包含以下内容的实体代码

端口 D 为 12 位输入总线

端口 OE 和 CLK 都是 1 位输入

端口 AD 为 12 位双向总线

剩余60页未读,继续阅读

aoeui

- 粉丝: 1

- 资源: 24

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0