没有合适的资源?快使用搜索试试~ 我知道了~

24C02CEEPROM使用手册

需积分: 9 2 下载量 71 浏览量

2009-10-16

20:35:22

上传

评论

收藏 102KB PDF 举报

温馨提示

试读

12页

24C02CEEPROM,用I2C通信,是ARM的I2C学习时经常用的。英文版

资源详情

资源评论

资源推荐

1997 Microchip Technology Inc.

Preliminary

DS21202A-page 1

M

24C02C

FEATURES

• Single supply with operation from 4.5 to 5.5V

• Low power CMOS technology

- 1 mA active current typical

- 10

µ

A standby current typical at 5.5V

• Organized as a single block of 256 bytes (256 x 8)

• Hardware write protection for upper half of array

• 2-wire serial interface bus, I

2

C compatible

• 100 kHz and 400 kHz compatibility

• Page-write buffer for up to 16 bytes

• Self-timed write cycle (including auto-erase)

• Fast 1 mS write cycle time for byte or page mode

• Address lines allow up to eight devices on bus

• 1,000,000 erase/write cycles guaranteed

• ESD protection > 4,000V

• Data retention > 200 years

• 8-pin PDIP, SOIC or TSSOP packages

• Available for extended temperature ranges

DESCRIPTION

The Microchip Technology Inc. 24C02C is a 2K bit

Serial Electrically Erasable PROM with a voltage range

of 4.5V to 5.5V. The device is organized as a single

block of 256 x 8-bit memory with a 2-wire serial inter-

face. Low current design permits operation with typical

standby and active currents of only 10

µ

A and 1 mA

respectively. The device has a page-write capability for

up to 16 bytes of data and has fast write cycle times of

only 1 mS for both byte and page writes. Functional

address lines allow the connection of up to eight

24C02C devices on the same bus for up to 16K bits of

contiguous EEPROM memory. The device is available

in the standard 8-pin PDIP, 8-pin SOIC (150 mil), and

TSSOP packages.

PACKAGE TYPES

BLOCK DIAGRAM

- Commercial (C): 0

°

C to +70

°

C

- Industrial (I): -40

°

C to +85

°

C

- Automotive (E): -40

°

C to +125

°

C

PDIP/SOIC

TSSOP

A0

A1

A2

Vss

Vcc

WP

SCL

SDA

24C02C

24C02C

1

2

3

4

8

7

6

5

A0

A1

A2

V

SS

VCC

WP

SCL

SDA

1

2

3

4

8

7

6

5

I/O

Control

Logic

Memory

Control

Logic

XDEC

HV Generator

EEPROM

Array

Write Protect

Circuitry

YDEC

Vcc

Vss

SENSE AMP

R/W CONTROL

SDA

SCL

A0 A1 A2

WP

2K 5.0V I

2

C

™

Serial EEPROM

I

2

C is a trademark of Philips Corporation.

查询24C02C供应商

24C02C

DS21202A-page 2

Preliminary

1997 Microchip Technology Inc.

1.0 ELECTRICAL

CHARACTERISTICS

1.1 Maxim

um Ratings*

V

CC

........................................................................ 7.0V

All inputs and outputs w.r.t. V

SS

......-0.6V to V

CC

+1.0V

Storage temperature ...........................-65˚C to +150˚C

Ambient temp. with power applied.......-65˚C to +125˚C

Soldering temperature of leads (10 seconds) ...+300˚C

ESD protection on all pins

......................................≥

4 kV

*Notice:

Stresses above those listed under “Maximum ratings” may

cause permanent damage to the device. This is a stress rating only and

functional operation of the device at those or any other conditions

above those indicated in the operational listings of this specification is

not implied. Exposure to maximum rating conditions for extended peri-

ods may affect device reliability.

TABLE 1-1: PIN FUNCTION TABLE

Name Function

V

SS

SDA

SCL

V

CC

A0, A1, A2

WP

Ground

Serial Data

Serial Clock

+4.5V to 5.5V Power Supply

Chip Selects

Hardware Write Protect

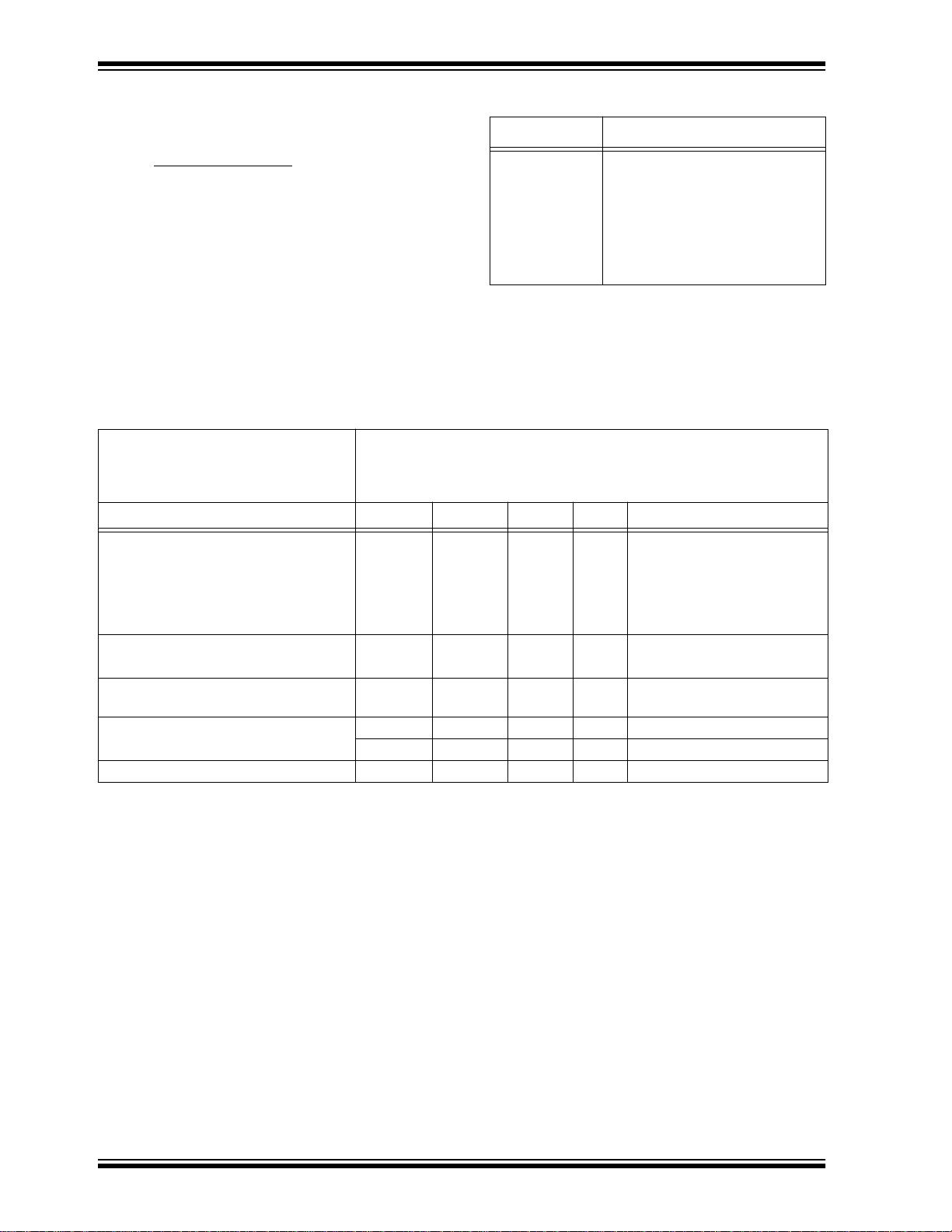

TABLE 1-2: DC CHARACTERISTICS

All parameters apply across the speci-

fied operating ranges unless otherwise

noted.

V

CC

= +4.5V to +5.5V

Commercial (C): Tamb = 0

°

C to +70

°

C

Industrial (I): Tamb = -40

°

C to +85

°

C

Automotive (E): Tamb = -40

°

C to +125

°

C

Parameter Symbol Min. Max. Units Conditions

SCL and SDA pins:

High level input voltage V

IH

0.7 V

CC

— V

Low level input voltage V

IL

— 0.3 V

CC

V

Hysteresis of Schmitt trigger inputs V

HYS

0.05 V

CC

— V (Note)

Low level output voltage V

OL

— 0.40 V I

OL

= 3.0 mA, Vcc = 4.5V

Input leakage current I

LI

-10 10

µ

A V

IN

= 0.1V to 5.5V, WP = Vss

Output leakage current I

LO

-10 10

µ

A V

OUT

= 0.1V to 5.5V

Pin capacitance (all inputs/outputs)

C

IN

, C

OUT

— 10 pF V

CC

= 5.0V (Note)

Tamb = 25

°

C, f = 1 MHz

Operating current

I

CC

Read — 1 mA V

CC

= 5.5V, SCL = 400 kHz

I

CC

Write — 3 mA V

CC

= 5.5V

Standby current I

CCS

— 50

µ

A V

CC

= 5.5V, SDA = SCL = V

CC

Note

: This parameter is periodically sampled and not 100% tested.

24C02C

1997 Microchip Technology Inc.

Preliminary

DS21202A-page 3

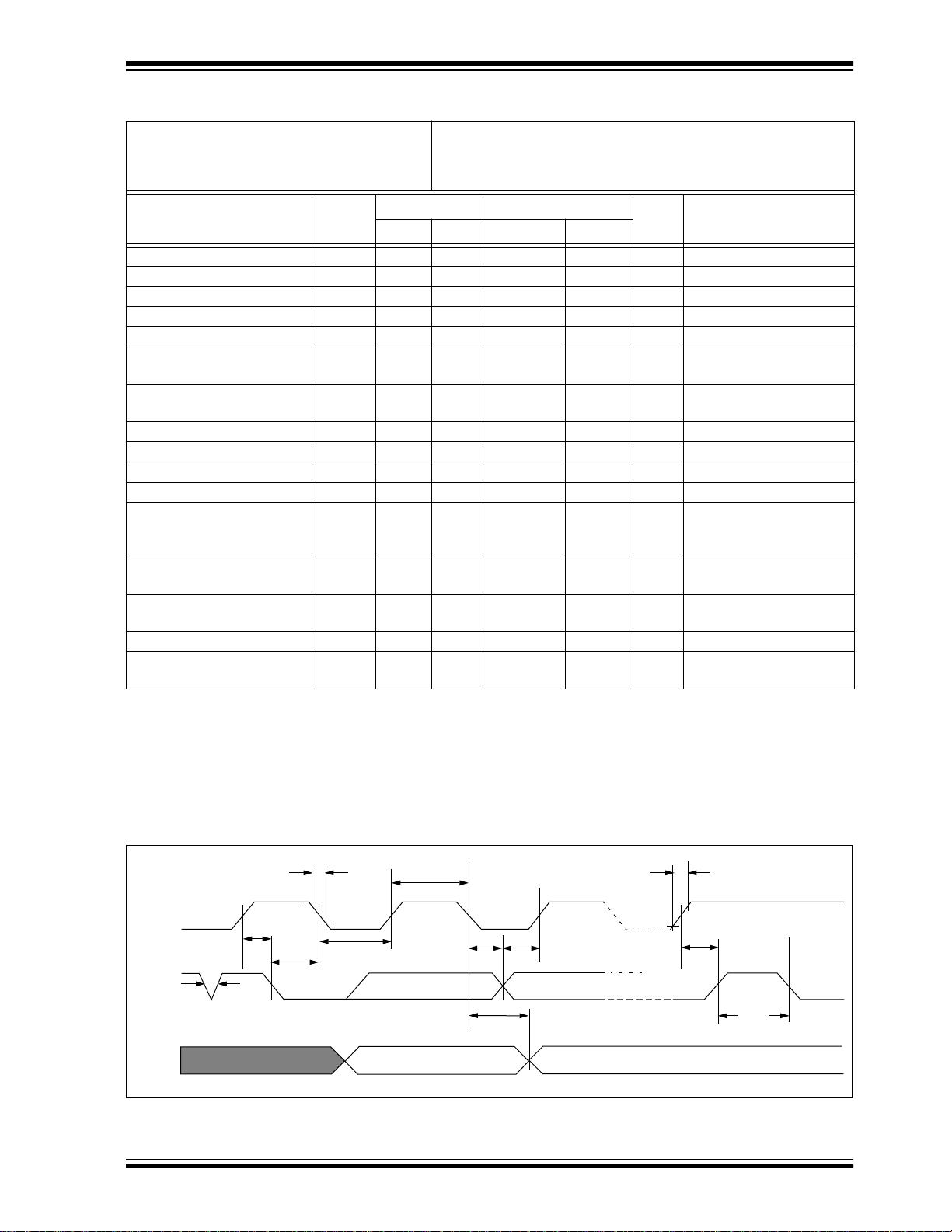

TABLE 1-3: AC CHARACTERISTICS

FIGURE 1-1: BUS TIMING DATA

All parameters apply across the specified oper-

ating ranges unless otherwise noted.

Vcc = 4.5V to 5.5V

Commercial (C): Tamb = 0

°

C to +70

°

C

Industrial (I): Tamb = -40

°

C to +85

°

C

Automotive (E): Tamb = -40

°

C to +125

°

C

Parameter Symbol

Tamb

>

+85

°

C -40

°

C

≤

Tamb

≤

+85

°

C

Units Remarks

Min. Max. Min. Max.

Clock frequency F

CLK

— 100 — 400 kHz

Clock high time T

HIGH

4000 — 600 — ns

Clock low time T

LOW

4700 — 1300 — ns

SDA and SCL rise time T

R

— 1000 — 300 ns (Note 1)

SDA and SCL fall time T

F

— 300 — 300 ns (Note 1)

START condition hold time T

HD

:

STA

4000 — 600 — ns After this period the first

clock pulse is generated

START condition setup time T

SU

:

STA

4700 — 600 — ns Only relevant for repeated

START condition

Data input hold time T

HD

:

DAT

0 — 0 — ns (Note 2)

Data input setup time T

SU

:

DAT

250 — 100 — ns

STOP condition setup time T

SU

:

STO

4000 — 600 — ns

Output valid from clock T

AA

— 3500 — 900 ns (Note 2)

Bus free time T

BUF

4700 — 1300 — ns Time the bus must be free

before a new transmission

can start

Output fall time from V

IH

minimum to V

IL

maximum

T

OF

— 250 20 + 0.1 C

B

250 ns (Note 1), C

B

≤

100 pF

Input filter spike suppression

(SDA and SCL pins)

T

SP

— 50 — 50 ns (Note 3)

Write cycle time T

WR

— 1.5 — 1 ms Byte or Page mode

Endurance 1M — 1M — cycles 25

°

C, V

CC

= 5.0V, Block

Mode (Note 4)

Note 1:

Not 100% tested. C

B

= total capacitance of one bus line in pF.

2:

As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region

(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

3:

The combined T

SP and VHYS specifications are due to Schmitt trigger inputs which provide improved noise

spike suppression. This eliminates the need for a TI specification for standard operation.

4: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific appli-

cation, please consult the Total Endurance Model which can be obtained on our BBS or website.

SCL

SDA

IN

TSU:STA

SDA

OUT

THD:STA

TLOW

THIGH

TR

TBUF

TAA

THD:DAT TSU:DAT TSU:STO

TSP

TF

剩余11页未读,继续阅读

zhu2008kuaile

- 粉丝: 1

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0